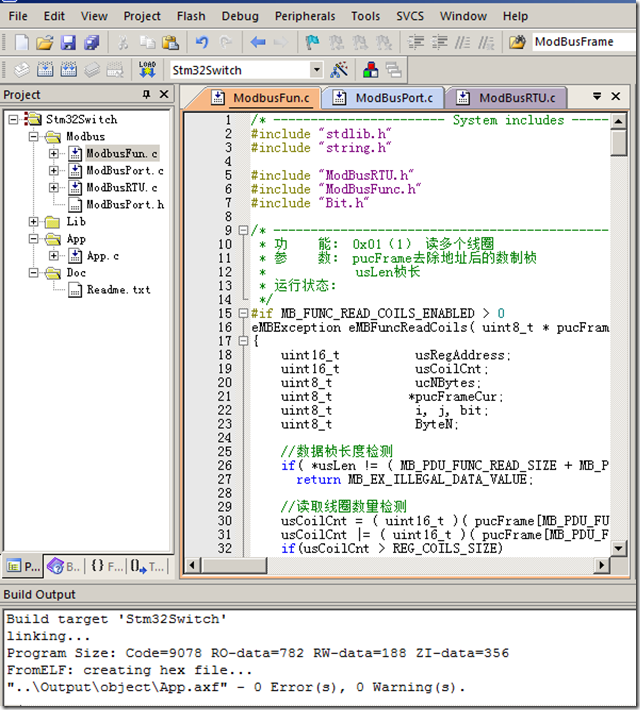

FreeModbus For stm32:点击下载源码

1、测试环境Keil MDK 4.7a stm32f103c8, PB12为输出线圈,

可以通过Modbus Poll来控制线圈的输出状态。

2、通过ModbusProt.h配置硬件、数据缓冲区大小和功能码配置

#define UART_USE 2 //串口号

#define TIM_USE 3 //定时器号

#define CPU_CLK 8 //8MHz

#define REG_INPUT_START 0x0000 //输入寄存器起始地址

#define REG_INPUT_NREGS 6 //输入寄存器数量

#define REG_HOLDING_START 0x0000 //保持寄存器起始地址

#define REG_HOLDING_NREGS 6 //保持寄存器数量

#define REG_COILS_START 0x0000 //线圈起始地址

#define REG_COILS_SIZE 8 //线圈数量(小于0x07B0)

#define REG_DISCRETE_START 0x0000 //离散开关起始地址

#define REG_DISCRETE_SIZE 8 //离散开关数量(小于0x07D0)

#define MB_FUNC_HANDLERS_MAX ( 4 ) //使用的功能码数量

#define MB_FUNC_OTHER_REP_SLAVEID_BUF ( 4 )

#define MB_FUNC_OTHER_REP_SLAVEID_ENABLED ( 0 ) //报告从设备功能

#define MB_FUNC_READ_INPUT_ENABLED ( 0 ) //读输入寄存器功能

#define MB_FUNC_READ_HOLDING_ENABLED ( 1 ) //读保持寄存器功能

#define MB_FUNC_WRITE_HOLDING_ENABLED ( 0 ) //写操持寄存存功能

#define MB_FUNC_WRITE_MULTIPLE_HOLDING_ENABLED ( 1 ) //写多个操持寄存存功能

#define MB_FUNC_READ_COILS_ENABLED ( 0 ) //读线圈

#define MB_FUNC_WRITE_COIL_ENABLED ( 1 ) //写线圈

#define MB_FUNC_WRITE_MULTIPLE_COILS_ENABLED ( 0 ) //写多个线圈

#define MB_FUNC_READ_DISCRETE_INPUTS_ENABLED ( 0 ) //读离散输入

#define MB_FUNC_READWRITE_HOLDING_ENABLED ( 0 ) //读写多个寄存器

3、移植要点为Port.c和Port.h

定时器操作在stm32平台下基本不用改

a、定时器初始化; xMBPortTimersInit()

b、开定时器及中断; vMBPortTimersEnable()

c、关定时器及中断; vMBPortTimersDisable()

d、定时器溢出中断服务程序;TIME_IQR_HANDLER()

串口操作:

a、串初始化; xMBPortSerialInit()

b、串口发送中断、接收中断; UART_IQR_HANDLER()

c、串口收发控制; vMBPortSerialEnable()

开关量操作 CPU硬件寄存器类型指针定义,用于定义IO输入和输出,

注意在此定义的IO必须初始化为输入或输出。

typedef volatile uint32_t * CPURegistertype;

//线圈状态, 存储格式:&IO输出口寄存器, 引脚号

MBCoilType MBCoils[REG_COILS_SIZE] = {

&(GPIOB->ODR), 12, //PB12做为输出线圈

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

};

//离散开关输入状态, 存储格式:&IO输出口寄存器, 引脚号

MBDiscreteType MBDiscretes[REG_DISCRETE_SIZE] = {

&(GPIOB->ODR), 12, //PB12做为离散输入

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

&(GPIOB->ODR), 12,

};

Mail: worldsing@foxmail.com

QQ: 237539049