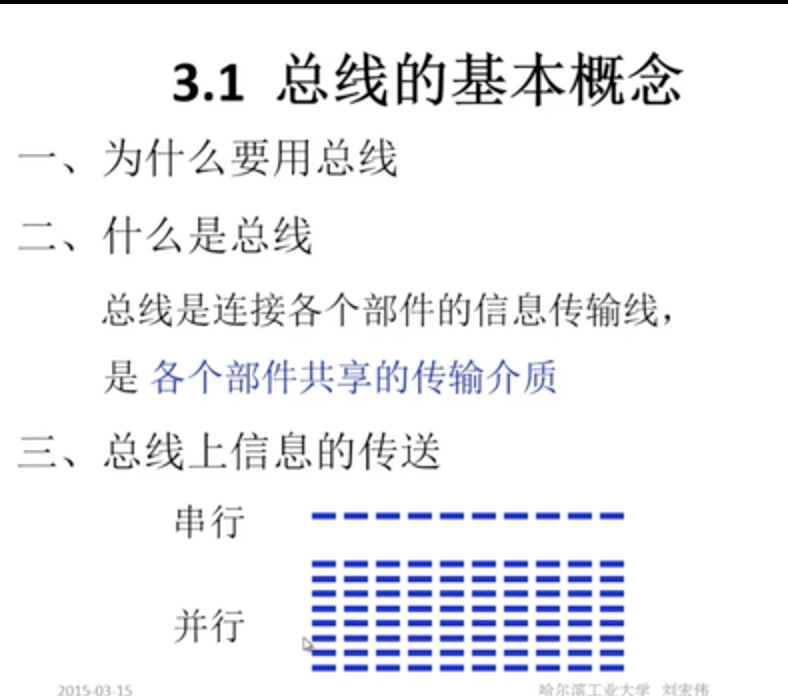

.1-总线的基本概念

http://m.elecfans.com/article/669460.html

http://m.elecfans.com/article/669460.html

https://baike.baidu.com/item/%E6%97%B6%E9%92%9F%E9%A2%91%E7%8E%87/103708?fr=aladdin 时钟频率

http://www.cnblogs.com/juner/p/5514615.html 为什么目前的串行比并行传输快

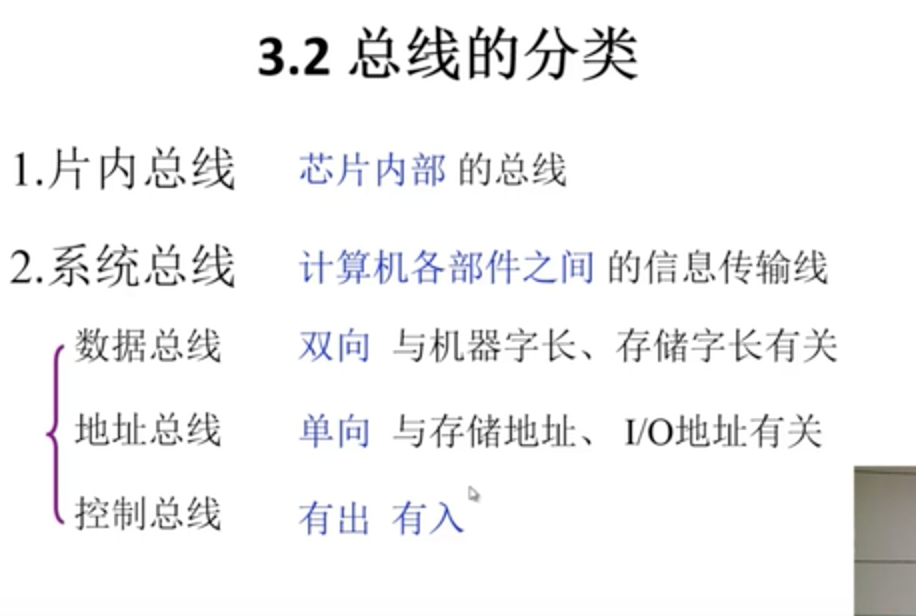

.2 总线的分类

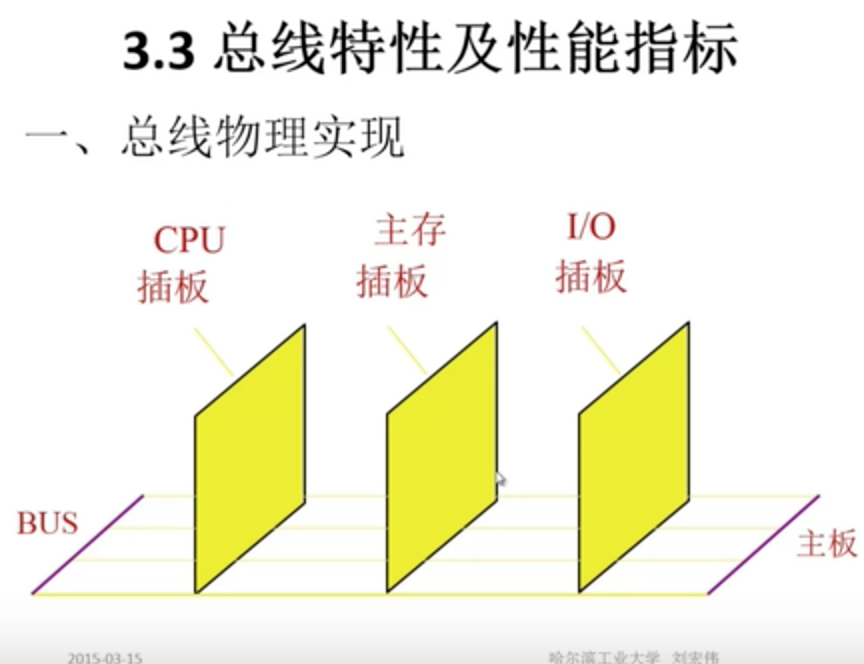

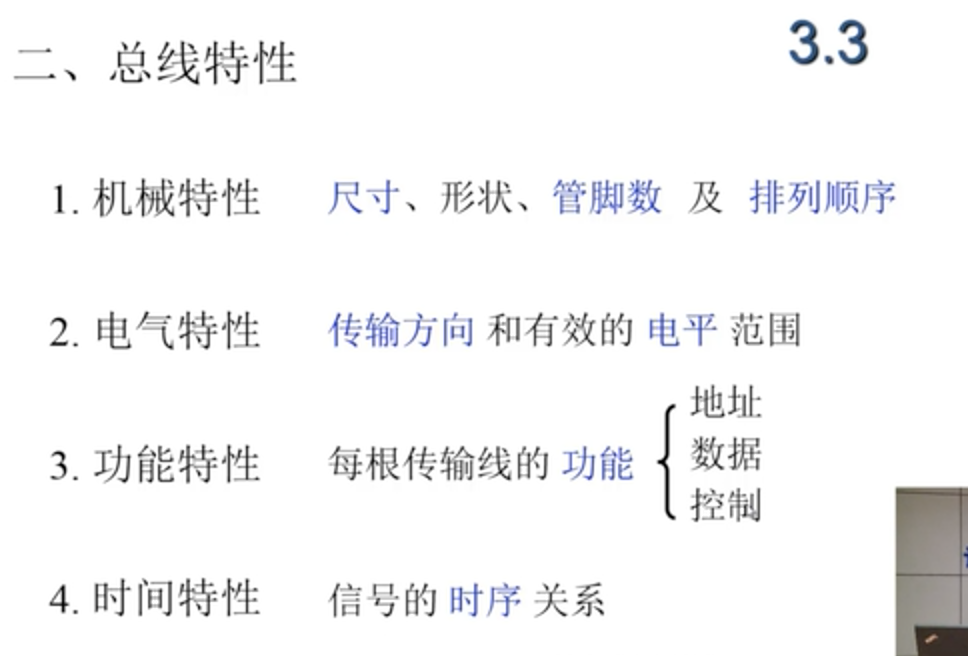

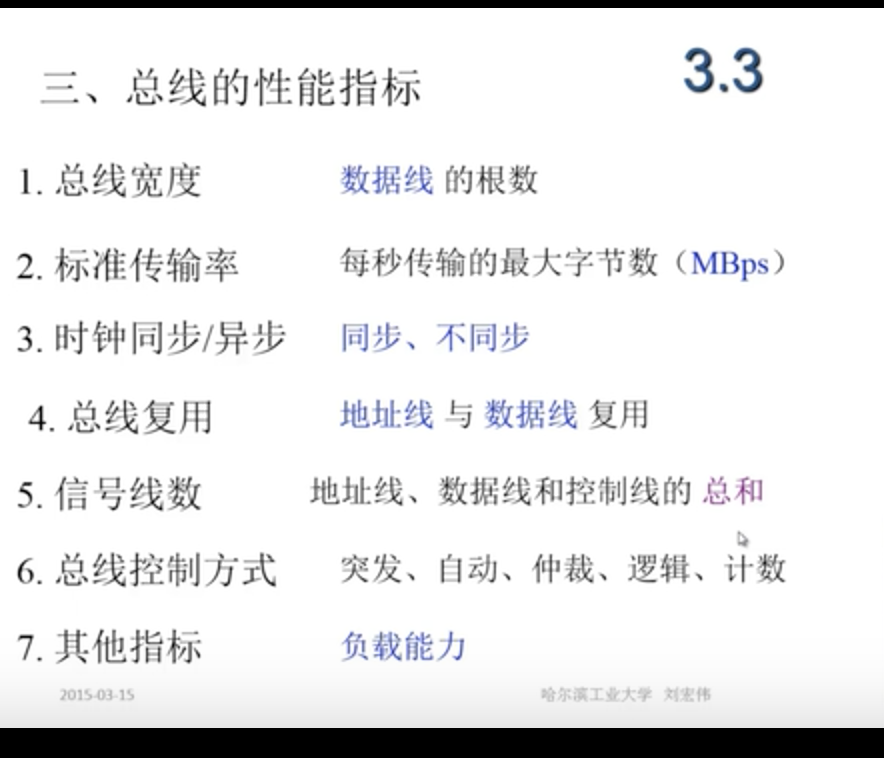

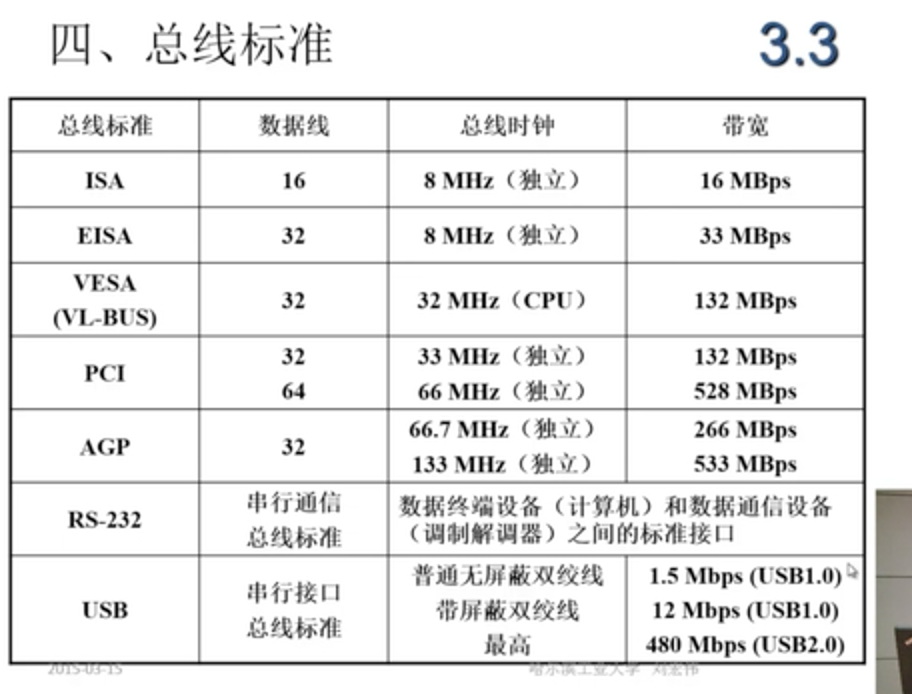

.3总线的特性及性能

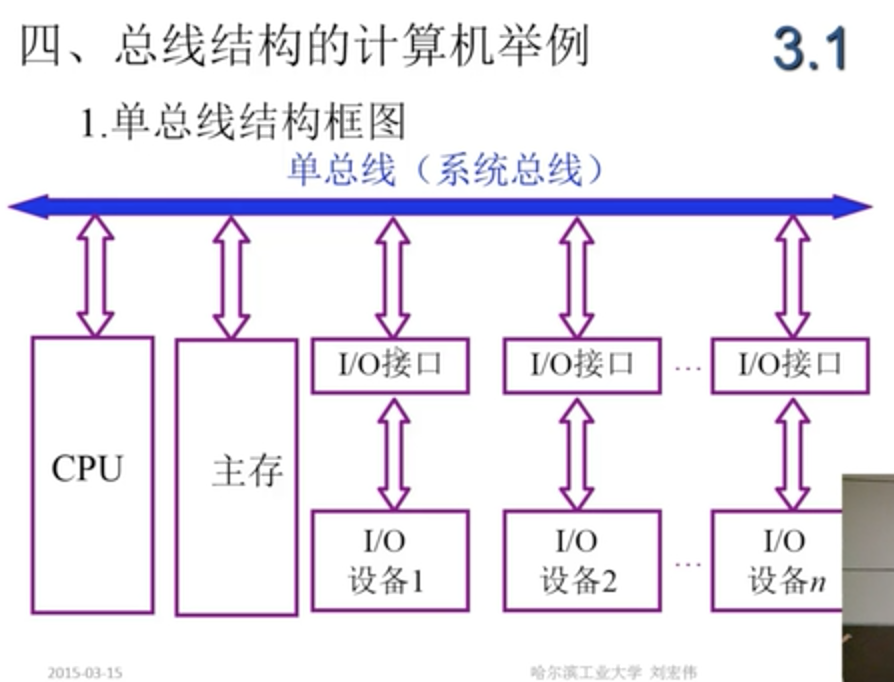

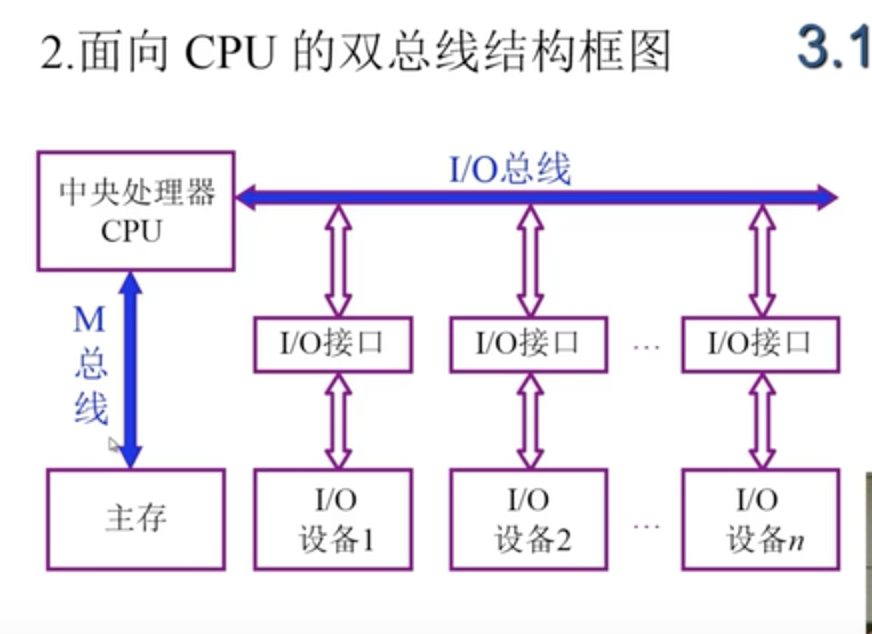

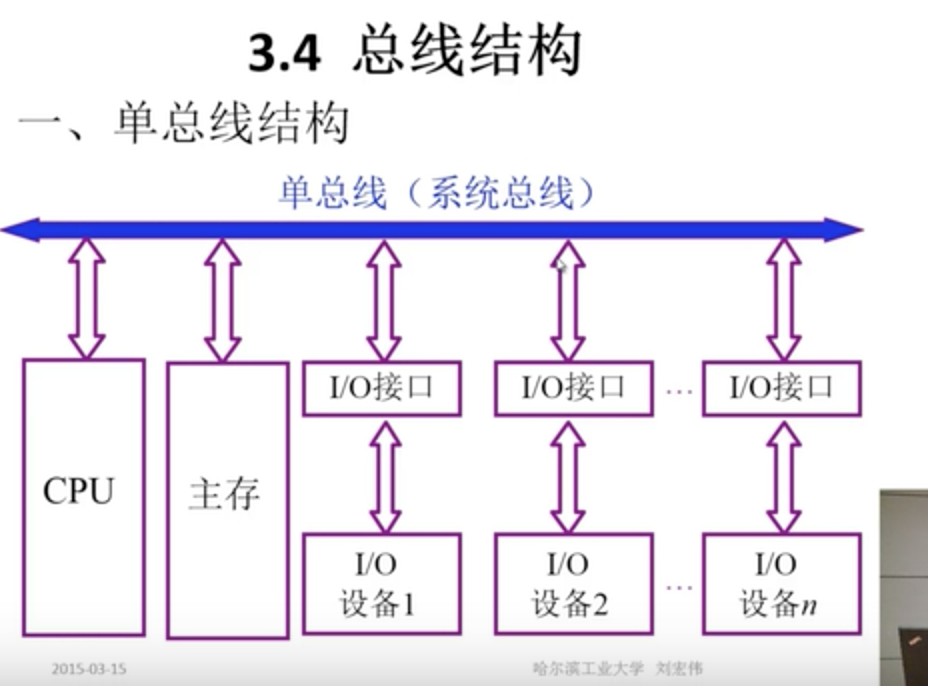

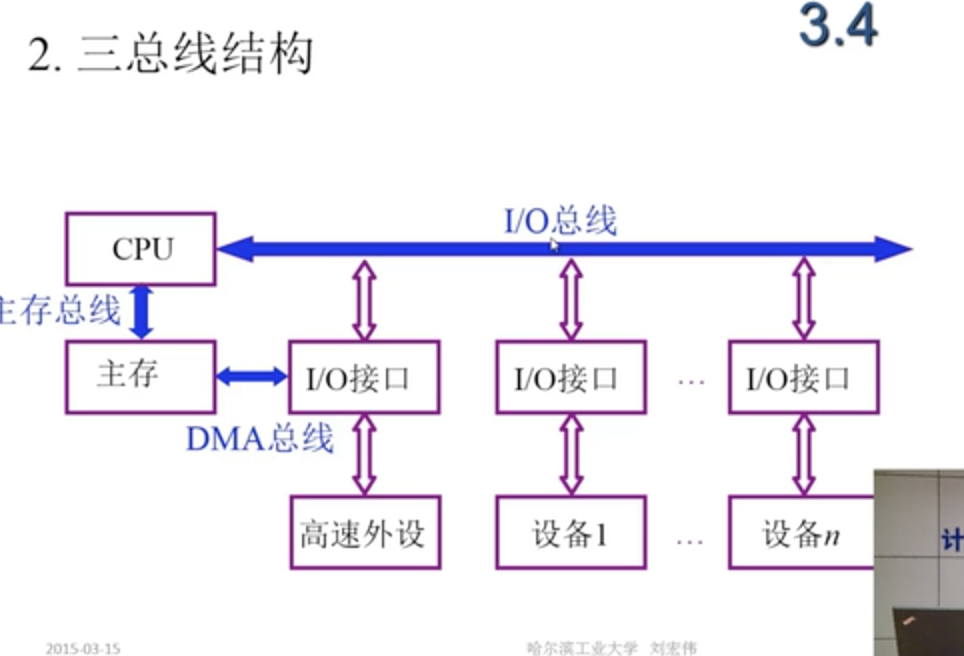

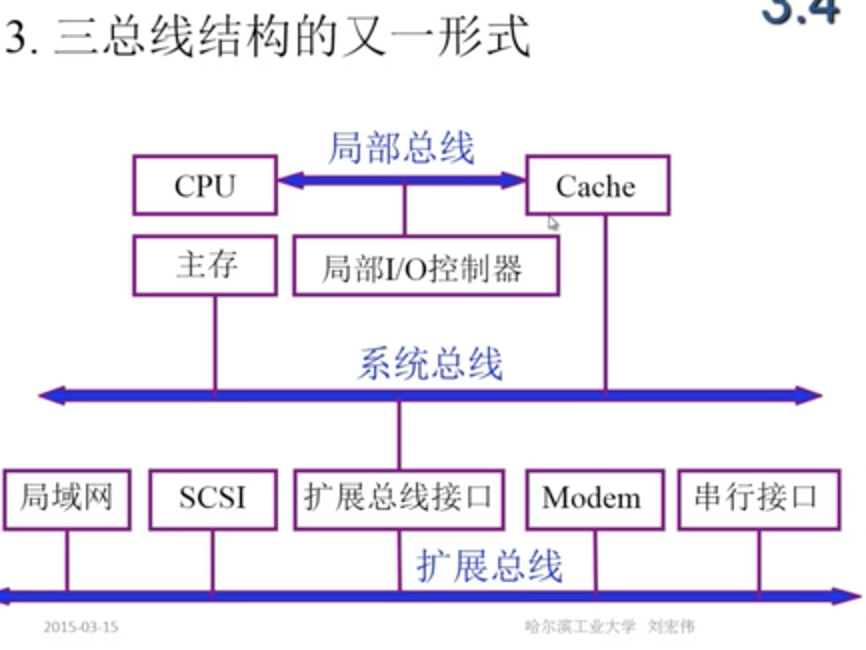

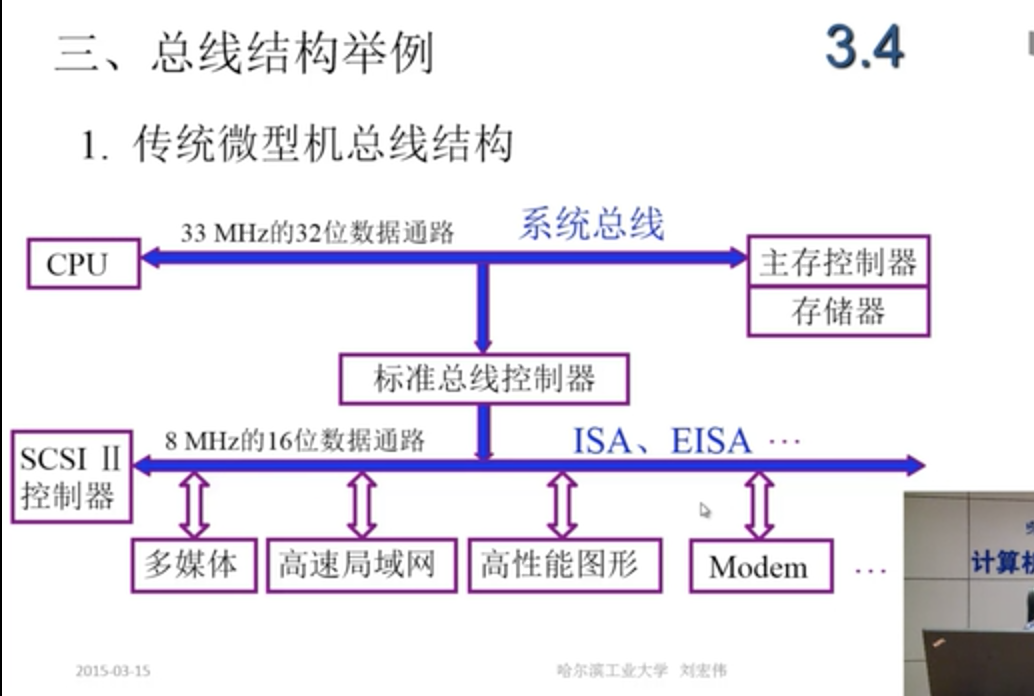

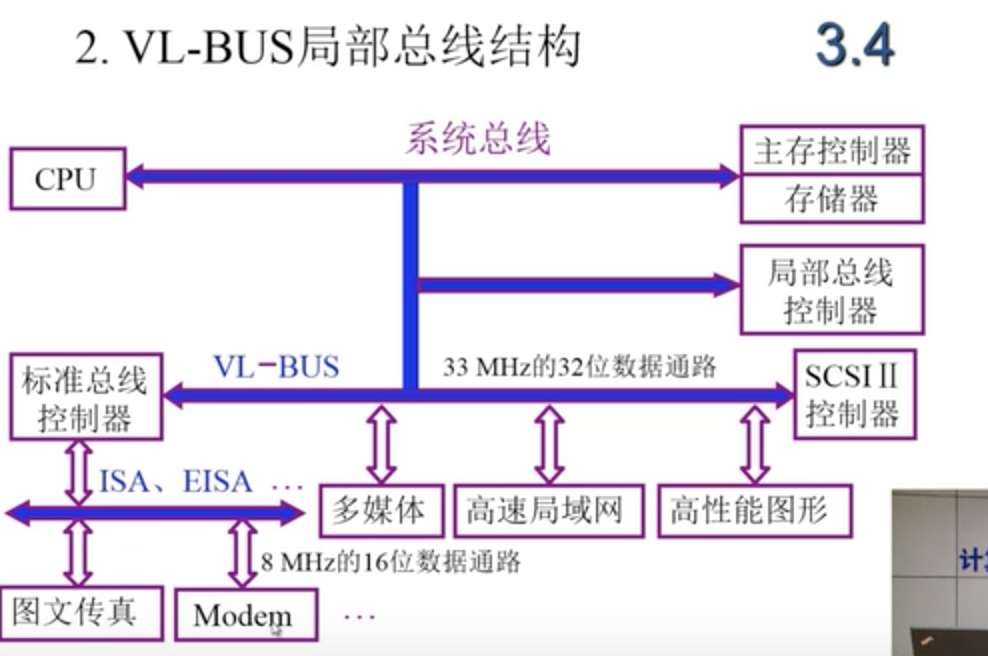

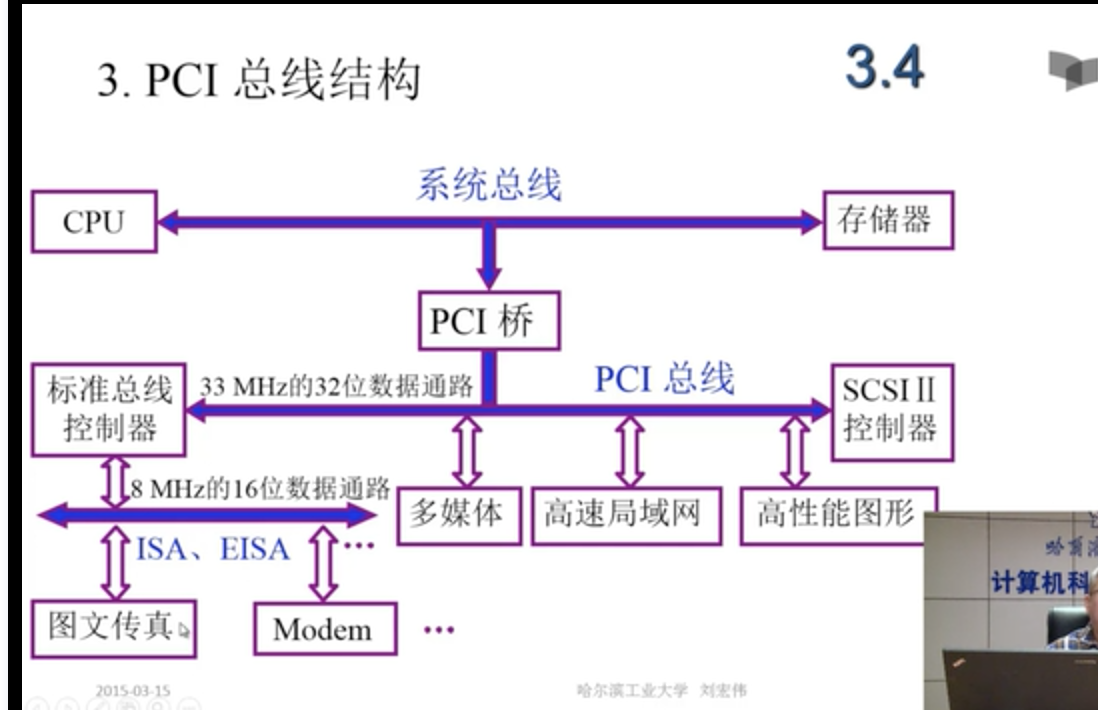

. 4总线结构

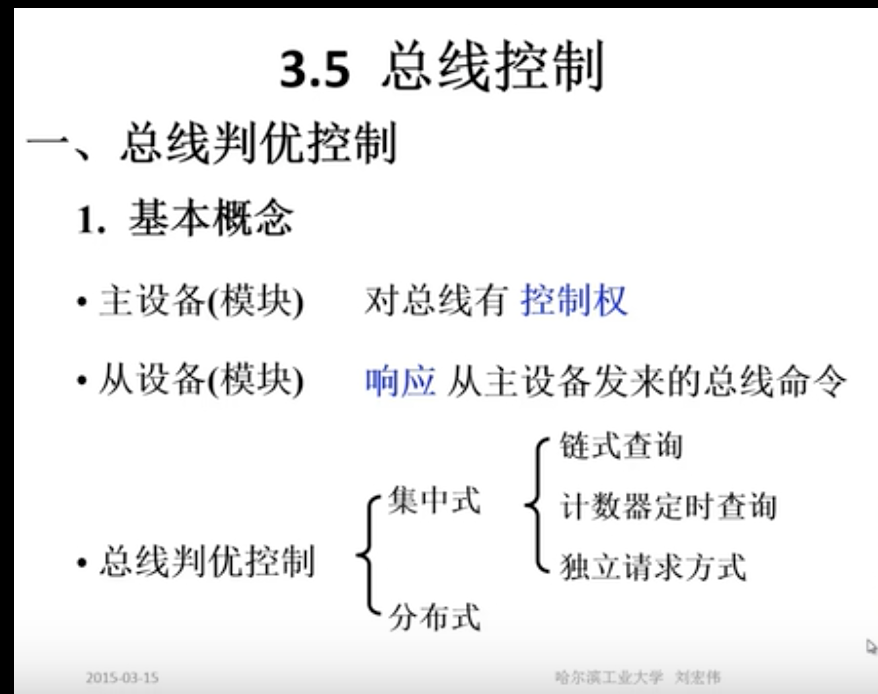

.5 总线控制a

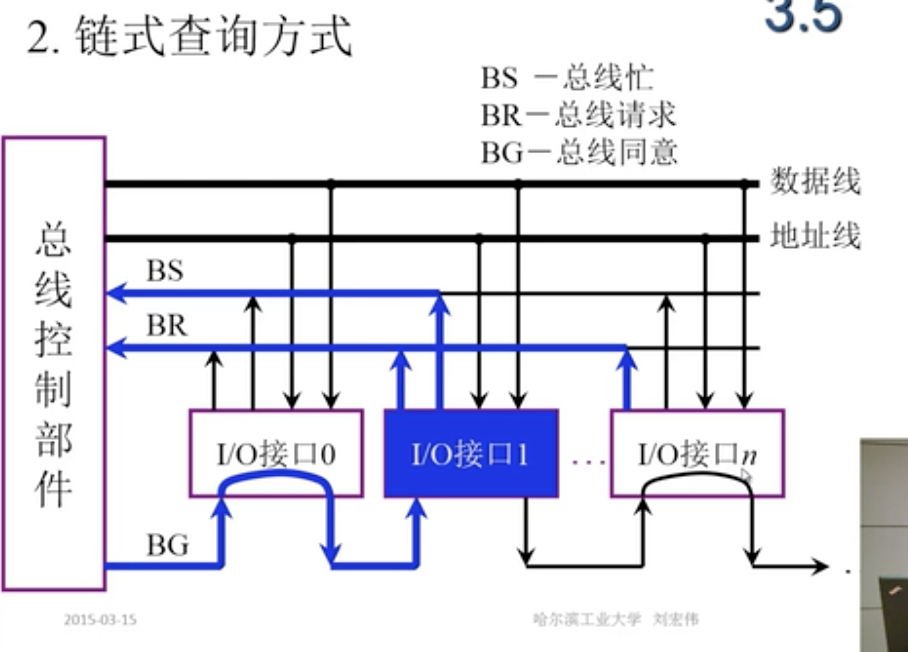

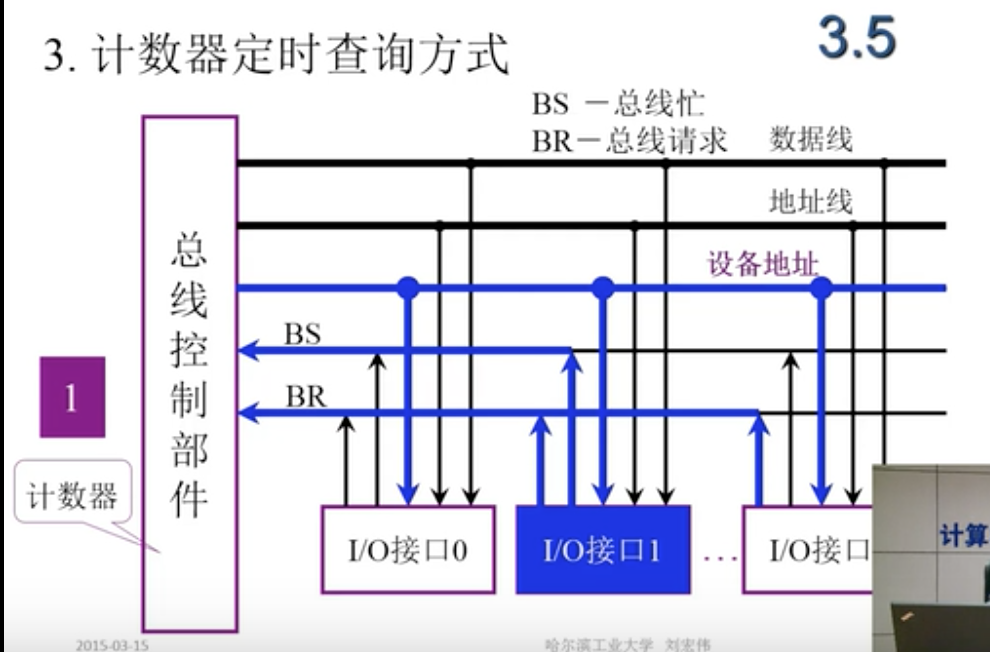

BR ---> BG

BR ---> BG

这两种速度都比较慢 需要排序,查找

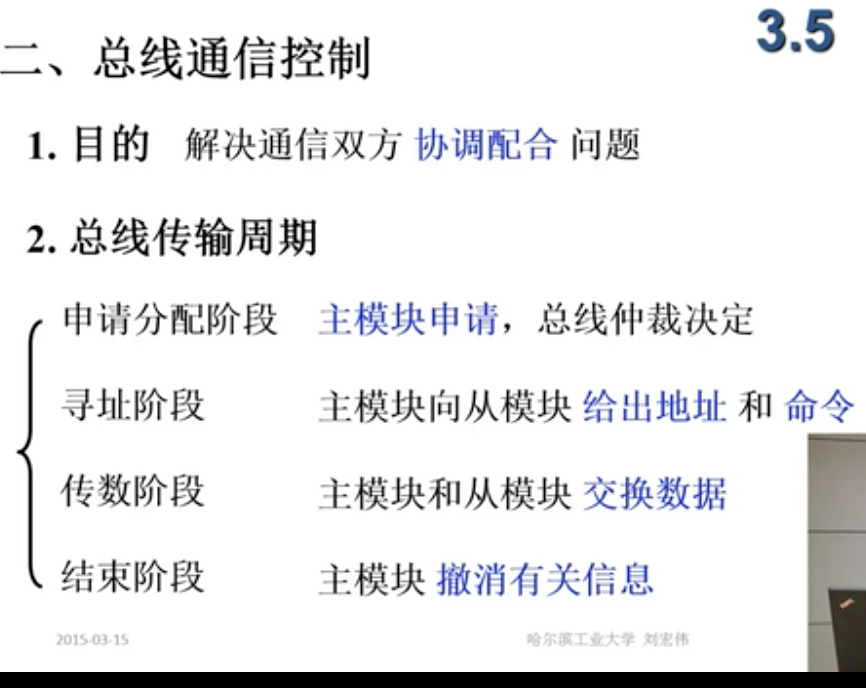

.5 b 总线控制b

的潜力

的潜力

为什么同步通信一般用于总线较短的场合?

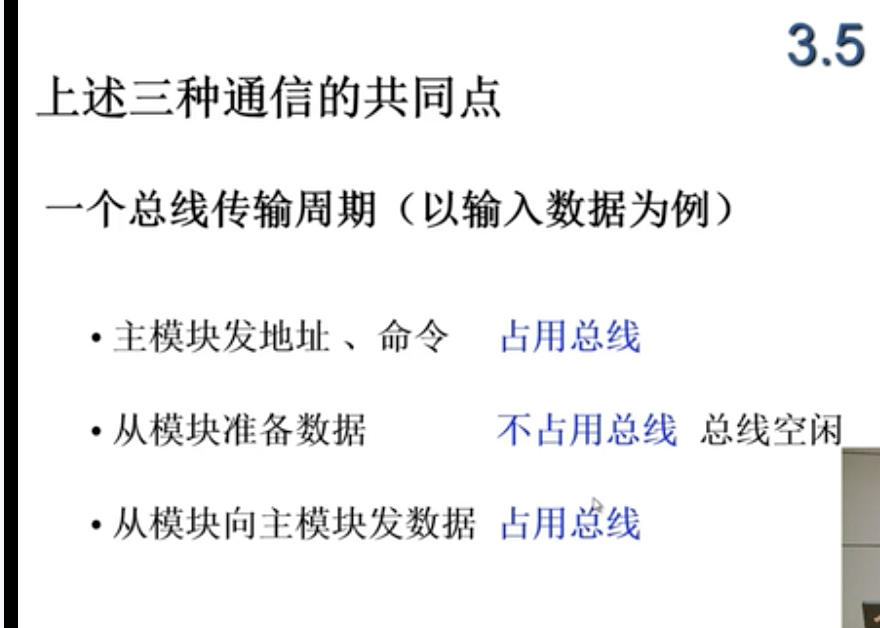

总线同步通信

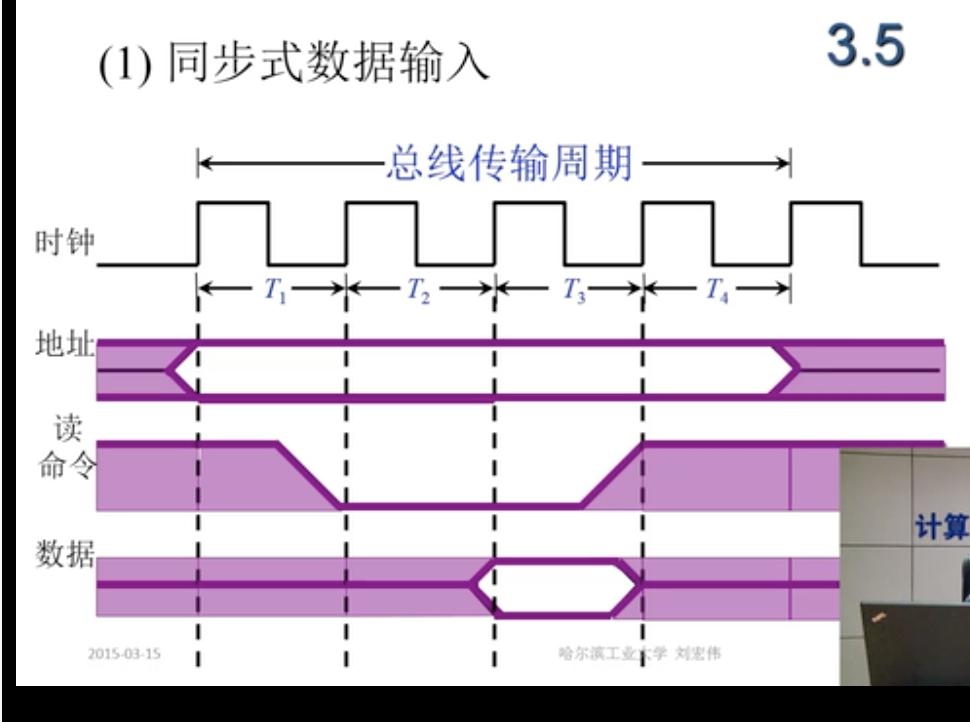

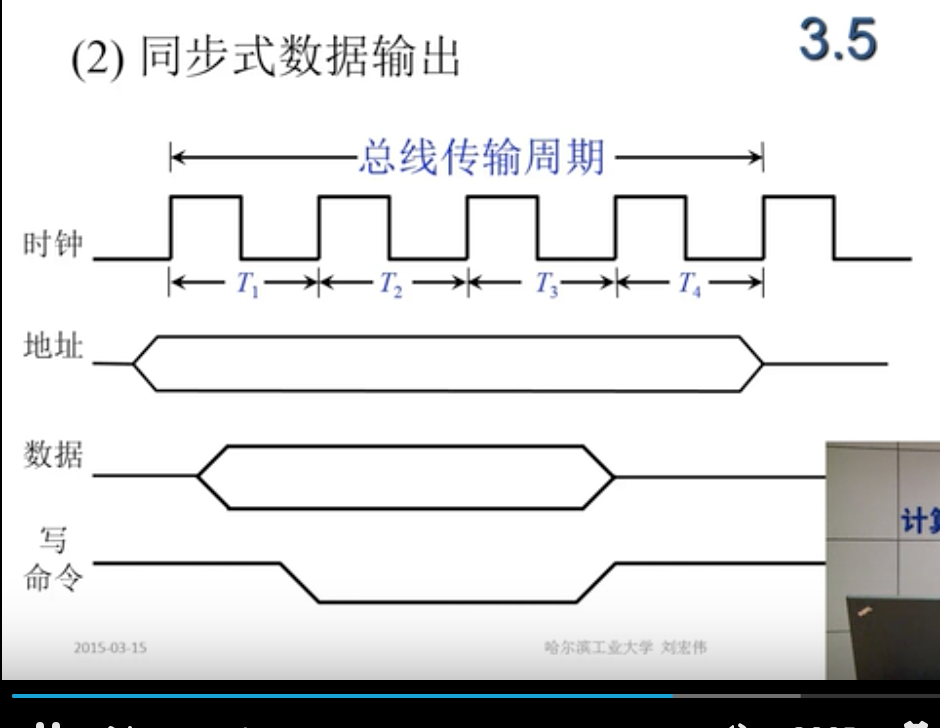

也称为总线同步定时方式。 总线上的部件通过总线进行信息传送时,用一个公共的时钟信号进行同步,这种方式成为同步通信。这个公共的时钟可以由CPU总线控制部件发送到每一个部件(设备),也可以让每个部件有各自的时钟发生器,然而它们都必须有总线控制部件发出的时钟信号进行同步。

由于采用了公共时钟,每个部件什么时候发送或接收信息都由统一的时钟规定,因此,同步通信具有较高的传输频率。

同步通信适用于总线长度较短、各部件存取时间比较接近的情况。这是因为,同步方式对任何两个设备之间的通信都给予同样的时间安排。就总线长度来讲,必须按距离最长的两个设备的传输延迟来设计公共时钟。但是总线长了势必降低传输频率。

存取时间是指部件接到读/写命令,到完成读出或写入一个数据所需要的时间。同步总线必须按最慢的部件设计公共时钟,如果各部件存取时间相差很大,也会损失总线效率。

https://zhidao.baidu.com/question/1952848401026531668.html

半互锁的缺点,从设备发送接收到的信号后,1变0,但是主设备可能一直没有接到信号,所以主设备还一直保持1

可能是这个意思啊,我猜的

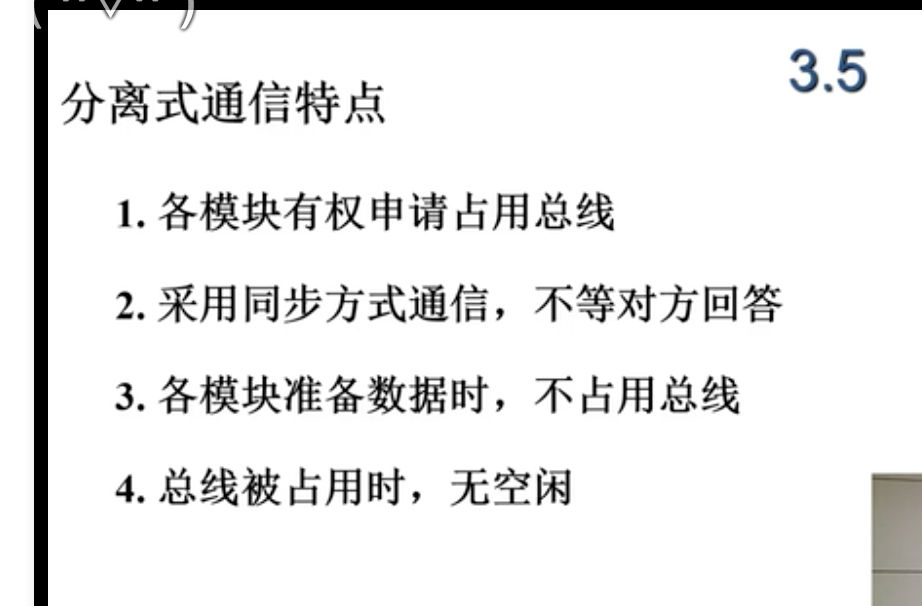

.5c

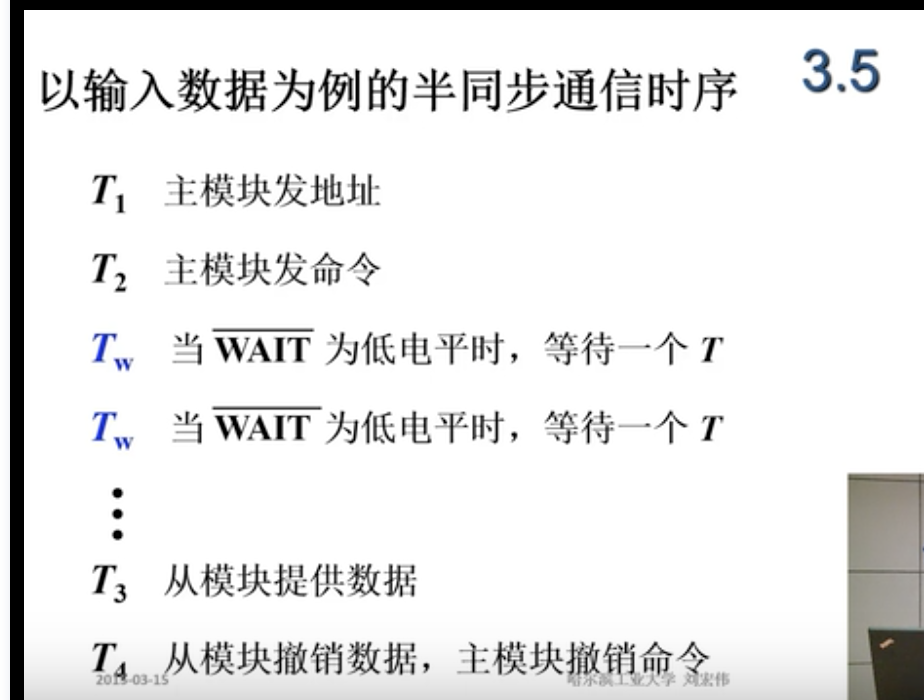

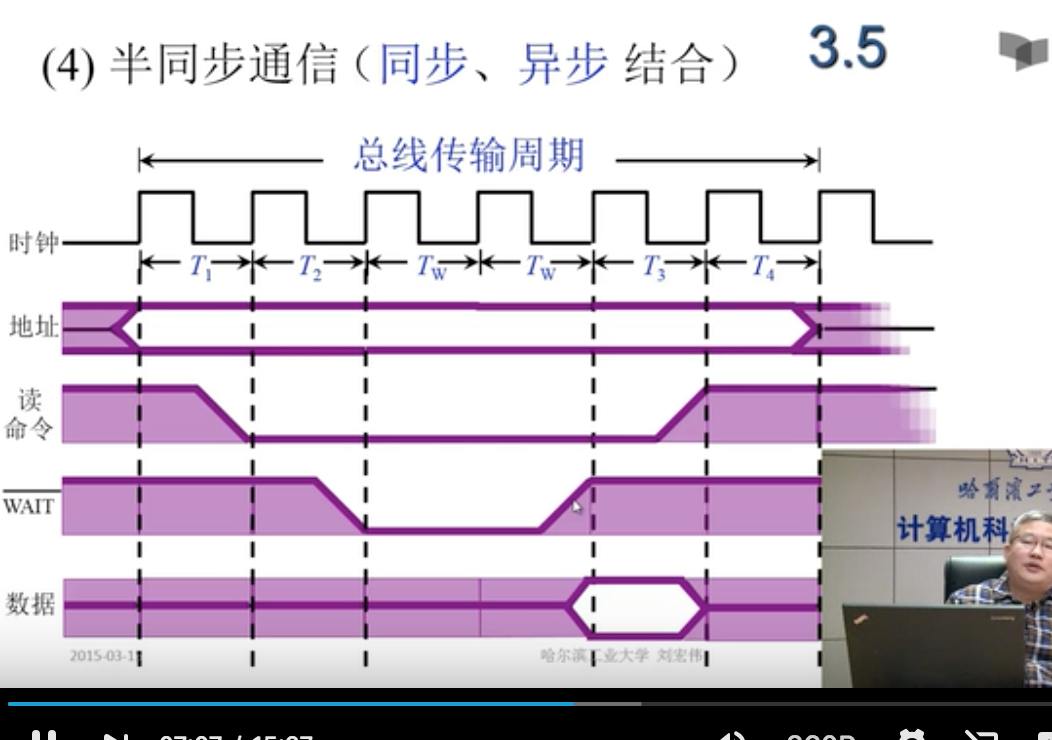

主模块cpu,从模块存储器,t3到来之

主模块cpu,从模块存储器,t3到来之

前,从模块发送wait信号,

可以类比java中的指令重排吧,和老师讲的机械硬盘寻址那个