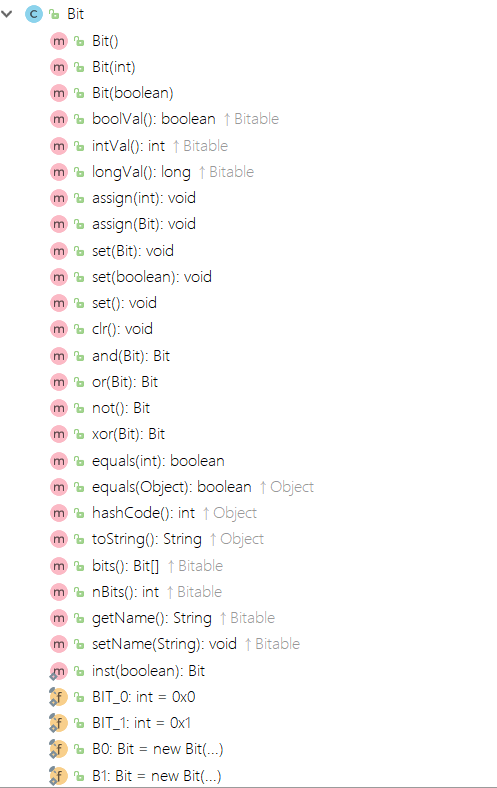

一. Bit

类结构如下:

主要属性:

- value: bit的值,只支持0,1, 分别为 Bit.BIT_0 和 Bit.BIT_1;

主要方法:

- 构造方法

Bit(): 创建一个Bit,值为默认值0;

Bit(int value): 创建一个Bit,值为参数value;

Bit(boolean): 创建一个Bit,boolean参数为true,则比特值为1,反之为0;

- 获取值的方法

boolVal(): 比特值为1,则返回true,为0则返回false;

intVal():返回int型(32位)0或1;

longVal(): 返回long型(64位)0或1;

- 赋值方法

set(): 置1;

clr(): 清0;

被Bits使用的赋值方法:assign;

被Reg使用的赋值方法:set;

- 逻辑操作方法

and(): 与;

or(): 或;

not(): 非;

xor(): 异或;

- 判断方法

equals(int value): 判断是否月value相等;

equals(Object): 判断是否与某个Bit相同或值相等;

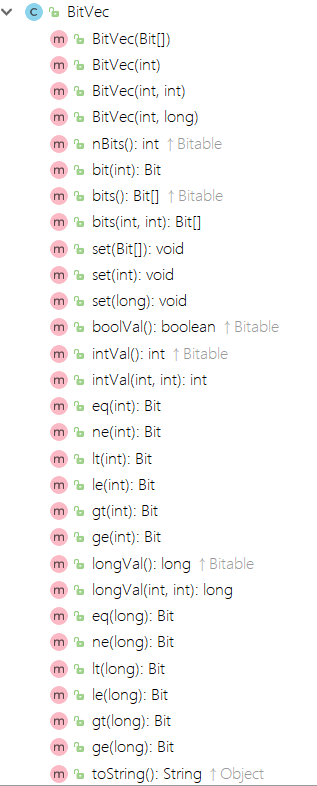

二. BitVec

辅助类,方便处理一组Bit;

Bits和Reg继承自BitVec;

类结构如下:

主要属性:

- Bit[]: 比特数组,0为lsb,length - 1为msb;

- nBits: 比特位数;

主要方法:

- 构造方法

BitVec(Bit[]): 直接基于提供的比特数组,创建比特向量;

BitVec(int nBits): 创建一个nBits位的比特向量,所有比特为默认值;

BitVec(int nBits, int value): 创建一个nBits位(最多32位)的比特向量,使用int值(最多32位)的每一位分别赋值;

BitVec(int nBits, long value): 创建一个nBits位(最多64位)的比特向量,使用long值(最多64位)的每一位分别赋值;

- 获取值的方法

boolVal(): 所有比特值都为0,则返回false,否则返回true;

intVal():返回int型(32位)值,从lsb到msb每一个比特的值,分别赋值给int值的每一位;

intVal(int msb, int lsb):返回从lsb到msb这一部分比特位组成的int值;

longVal(): 返回long型(64位)值,从lsb到msb每一个比特的值,分别赋值给long值的每一位;

longVal(int msb, int lsb): 返回从lsb到msb这一部分比特组成的long值;

- 获取某一个比特

bit(int index): 获取第index个比特(从0开始);

- 获取全部比特:bits()

- 获取部分比特

bits(int msb, int lsb):[msb, lsb], 获取从lsb(包含)到msb(包含)的比特;如果msb < lsb,则获取的比特逆序;

如:一组比特abcd, bits(1,0)返回cd,bits(0,1)返回dc.

- 赋值方法

这里主要提供set方法。

- 判断方法

eq: 等于

ne: 不等于

lt: 小于

le: 小于等于

gt: 大于

ge: 大于等于

需要注意的是,这些判断方法,返回的不是布尔型true/false,而是一个Bit。

这样做一则方便判断的结果参与后续的处理,一则更贴近判断的物理意义(返回值通过一根线的高低电平标识)。

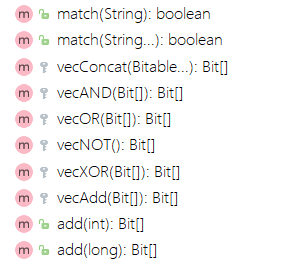

- match():把把比特数组的值分别与字符串如"0b10xx"逐位比较,忽略字符串标识为x的位,看值是否匹配;

- 连接方法:vecConcat()

举例:a.vecConcat(b, c)之后,返回的bit[]的值为abc,如果b=0bxyz,则bit[]值为0baxyzc

- 逻辑运算:与或非、异或

- 数学运算:加法

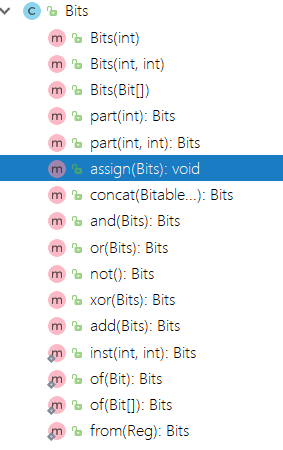

三. Bits

意为一组线,处理一组线的各种操作。使用BitVec提供的方法,但是返回的类型为Bits类型,而非比特数组;

Bits赋值使用assign方法,不能使用set方法。

主要方法:

- 构造方法

与BitVec对应;

- 获取部分比特

类似于BitVec的bits()方法组,但是返回的不是比特数组,而是Bits类的对象;

- 赋值方法

assign():意义上相当于Verilog中对线的continuous assignment.

- 连接方法

concat():同BitVec的连接方法,返回Bits类的对象;

- 逻辑操作

同BitVec的逻辑操作,返回Bits类的对象;

- 数学运算

只实现了加法,同BitVec的运算方法,返回Bits对象;

静态辅助方法:

- inst():是Bits的创建更紧凑,省略new的使用;

- Bits.of(Bit):返回只包含一根线的Bits对象,一般是为了方便与其他Bits进行操作,如连接;

- Bits.of(Bit[]):返回包含比特数组的Bits对象;

- Bits.from(Reg):返回有Reg包含的一组比特构成的Bits,意义上的理解为:返回的是寄存器的输出线;

四. Reg

意为寄存器,处理寄存器的各种操作。使用BitVec提供的方法,但是返回的类型为Reg类型,而非比特数组;

寄存器赋值使用set方法,不能使用assign方法。

可以看到基本与Bits的方法相同,只是返回的为Reg对象。这里不做赘述。

增加了一个赋值方法:

- set(Bits): 把Bits包含的比特数组的值分别赋给reg包含的比特数组,意为:Bits中的线为Reg对象的输入线;

增加了一组方便方法:简化只有一个比特的寄存器与Bit之间的操作:

- set(Bit):将reg第一个比特的值,赋值为参数比特的值;

- and(Bit):将reg第一个比特,与参数Bit相与;

- or(Bit):将reg第一个比特,与参数Bit相或;

- xor(Bit):将reg第一个比特,与参数Bit相异或;

不同的静态辅助方法为:

- Reg.to(Bit): 返回比特组成的Reg对象,意为:参数Bit对应的线为返回的Reg对象的输出线;

- Reg.to(Bits):返回Bits的比特数组组成的Reg对象,意为:参数Bits中的线为返回的Reg对象的输出线,即返回的Reg对象的值输出到Bits中的线上;

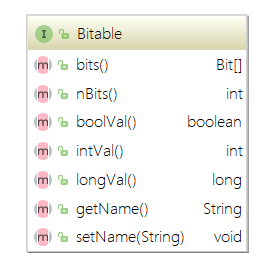

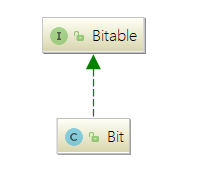

五. Bitable

辅助接口,方便对Bit、Bits、Reg的统一处理。意义为:可比特化的类型。比如Bits和Reg都可以分为多个比特。