介绍硬件建模的各个层次,以及基于RTL进一步提高层次的方法。

1. 物理版图

直接画出各个物理器件的物理连接图,这个应该是最低的硬件建模层次了。

MOS6502据说就是这么开发的:http://www.visual6502.org/JSSim/expert.html

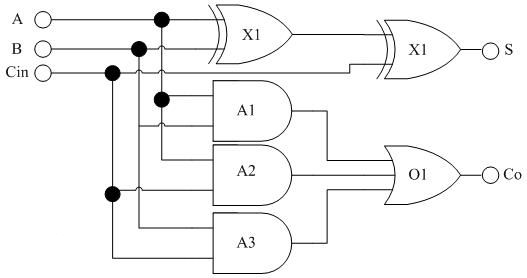

2. 门和开关层(GSL)

门也是由开关组成的。

GSL把门和开关抽象成为关键字,连线抽象成为传参。描述的也是各个物理器件及其连线关系。

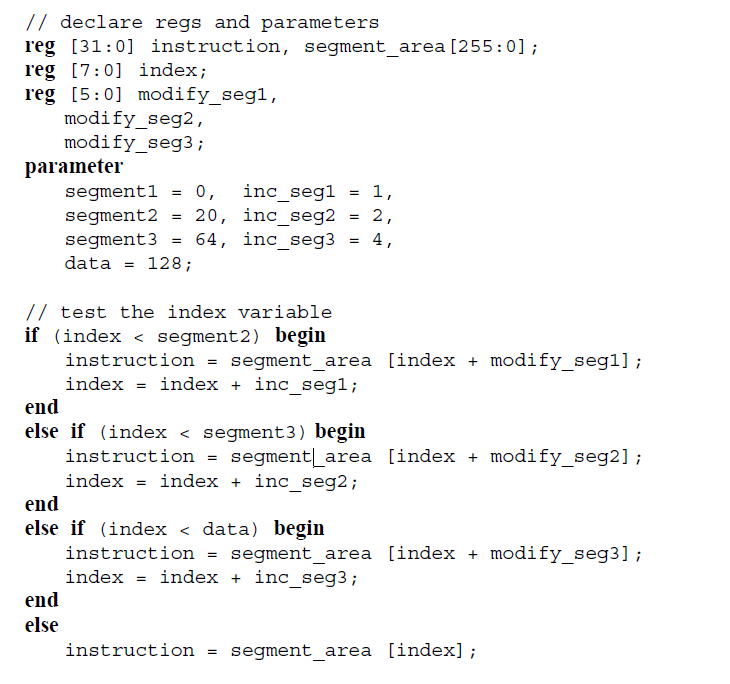

3. 寄存器传输层(RTL)

RTL层把DFF抽象成为reg类型;把常用的逻辑单元抽象成为符号,如加减乘除移位等;把连接抽象为赋值。

从描述硬件结构转换为描述行为逻辑,极大的降低了工作量,提高了效率。

4. 再提高一层

再提高一个层次呢?

基于公式:程序 = 数据 + 算法,有以下几个方面:

1) 提高数据类型层次

在RTL wire/reg的基础上,把数据类型提高一个抽象层次,如:

a. Chisel中的UInt/SInt/Bool/Aggregate/Clock,以及用户自定义数据类型Bundle等;

b. SystemC中位数确定的,位数任意的,定点浮点的数据类型;

c. SystemC中的事件类型的数据,用以提取出等待(wait)和通知(notify)行为;

2) 提高模型层次(HLS)

直接提高模型的抽象层次,以提高灵活性和效率。

a. 基于硬件建模思维

如SystemC,可以在系统级建模。

抽象出模块,process, clock, event, signal, port, interface等概念,直接在高于RTL的层次建模。

事实上,在SystemC的系统级建模层次上,硬件建模思维与软件建模思维是统一的。

b. 基于软件编程思维

如Vivado HLS, 把C语言函数转换为模块,把函数调用转换为模块关联。

如SystemC METHOD的实现。

这个需要把以软件编程思维编写的程序,转换为硬件模型。

3) 提高构建层次(Generator)

模型层保持不变,而使用生成器提高构建的层次。

这样一则模型容易理解,二则可以提高构建效率。

如Verilog的generate,Chisel的circuit generator。

5. SystemC

a. 提高了数据类型的抽象层次;

b. 可以进行系统级建模(system-level modeling),提高了模型层次;

c. METHOD实现使用软件编程思维方式,需要进行转换;

6. Chisel

a. 提高了数据类型的抽象层次;

b. 没有提高构建出的硬件模型的抽象层次;

c. 使用电路生成器提高了构建的层次;

硬件模型没有提高抽象层次,易于理解。

电路生成器,可以使用任何思维,任何语言特性,任何官方或第三方代码库。

只要落实到硬件模型上,生成器拥有无穷无尽的自由。