https://mp.weixin.qq.com/s/2vjM-gcauvHnn6KJzlOm4g

Chisel的模块和Verilog的模块很相似,都用来定义模块结构(hierarchical structure)。

Chisel的模块定义,包含三部分内容:

a. 继承自Module类;

b. 定义模块输入输出接口(继承自Bundle);

c. 把内部各部分与输入输出接口连接起来;

参考链接:

示例:

class Mux2 extends Module {

val io = IO(new Bundle{

val sel = Input(UInt(1.W))

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val out = Output(UInt(1.W))

})

io.out := (io.sel & io.in1) | (~io.sel & io.in0)

}

1. 继承Module类

如示例中:

class Mux2 extends Module

在Mux2类的定义中,val io是Mux2类的成员。代码:io.out := (io.sel & io.in1) | (~io.sel & io.in0) 定义了模块内部电路结构。

2. 定义输入输出接口

val io = IO(new Bundle{

val sel = Input(UInt(1.W))

val in0 = Input(UInt(1.W))

val in1 = Input(UInt(1.W))

val out = Output(UInt(1.W))

})

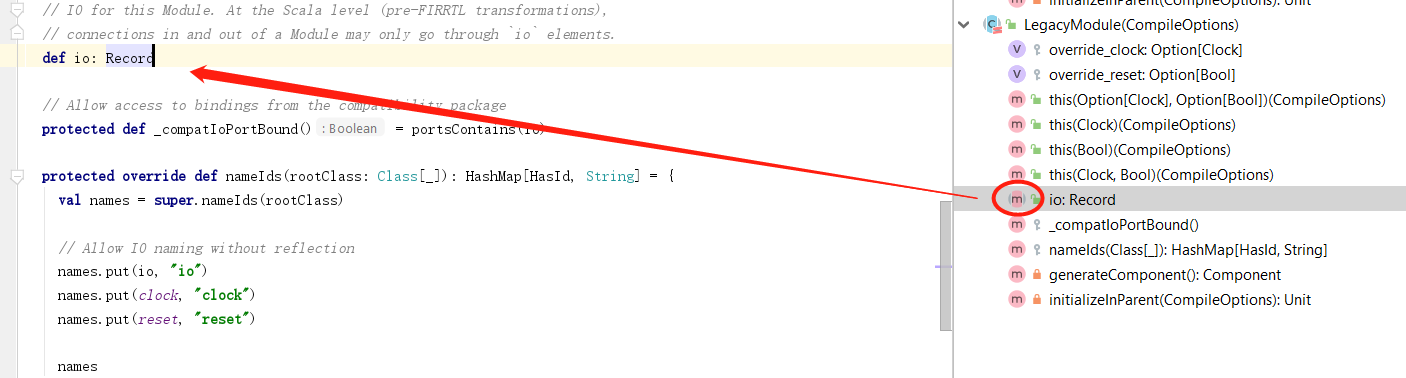

Module中定义了io,作为抽象成员存在,任何子类都要实现这个成员。

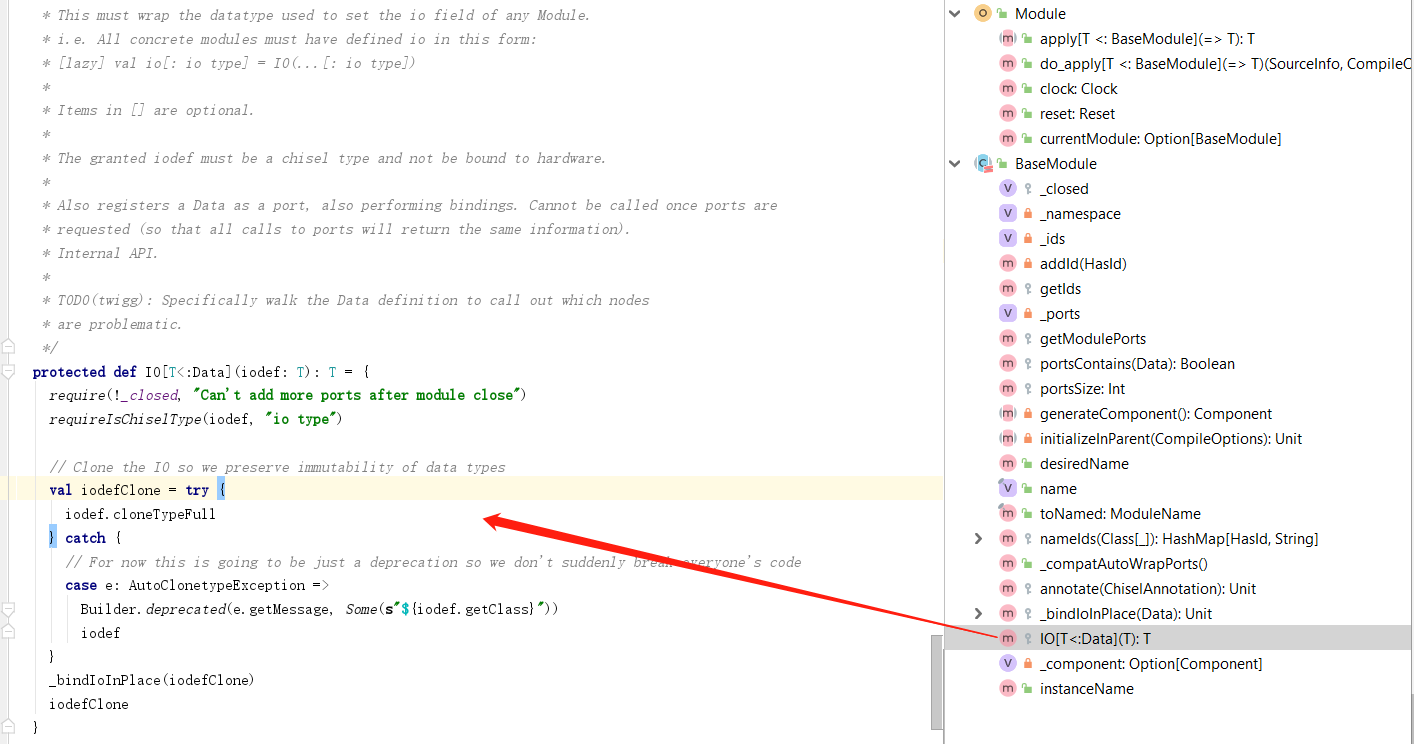

使用IO方法包裹,IO方法记录入参的信息:

实现一个匿名的Bundle子类,并定义数据成员。这个子类作为IO方法的参数,被绑定为模块的输入输出端口。

3. 连接内部子电路

代码行:io.out := (io.sel & io.in1) | (~io.sel & io.in0) 描述Mux2模块内部结构,并把输入输出连接起来。

需要注意的是io.out := (io.sel & io.in1) | (~io.sel & io.in0)直接是一行代码,写在类的定义中。这与Java中类的定义不同。形式上相当于Java中用static包裹住的静态代码,但效果上相当于构造方法中的代码。即在每一次new一个Mux2对象的时候,都会执行这一段代码。(Java类中的static代码块只在类加载时执行)

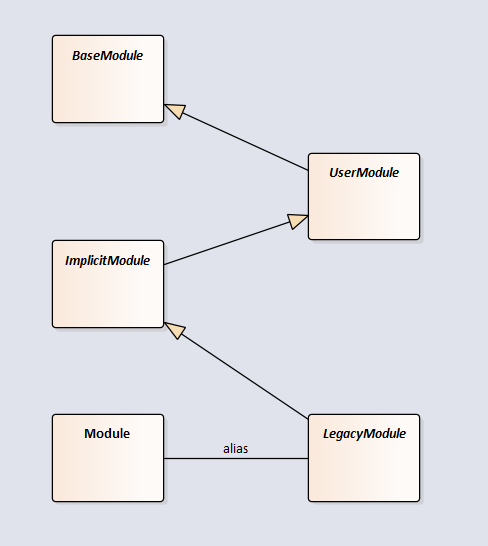

4. Chisel3中Module相关类的类图