1、数据的表示

以H结尾的数字表示该数是 16进制的,比如C7FFFH

1.1、进制的转换

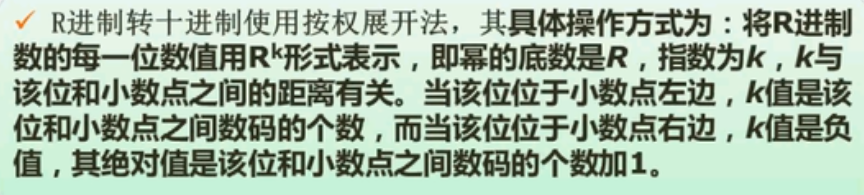

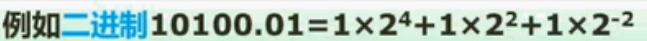

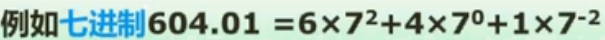

1.1.1、将R进制转10进制

1.1.2、将10进制转换为R进制

10进制转换为r进制数时,采用除r取余方法,即将十进制整数不断除以r取余数,直到商为0,所得的余数按逆序排列

1.1.3、二进制转八进制和十六进制

二进制转八进制可以将该二进制的数字从右到左,每三个为一组,一组转换为一个八进制数即可。比如:10001110 转为八进制为:216

二进制转十六进制可以将二进制的数字从右到左,没四个为一组,一组转换为一个十六进制即可,大于10进制的数,A表示10、B表示11、C表示12,以此类推。例如:10001110 转为十六进制为:8E

1.2、原码、反码、补码

原码、反码、补码能表示的数据范围如下:n 表示的是有多少位,1个字节有8位。

比如1个字节,原码范围:-127~127;反码:-127~127;补码:-128~127。可以看到原码和反码表示的范围是一样的,而补码比他们多了一个数,这是因为原码和反码的 0 有两种形式:0000 0000、1000 0000,而补码的 0 都是:0000 0000。

1.2.1、原码

原码就是符号位加上真值的绝对值, 即用第一位表示符号, 其余位表示值. 比如如果是8位二进制:

[+1]原 = 0000 0001

[-1]原 = 1000 0001

第一位是符号位. 因为第一位是符号位, 所以8位二进制数的取值范围就是:

[1111 1111 , 0111 1111]

即

[-127 , 127]

1.2.2、反码

正数的反码和原码一样,负数的反码是在其原码的基础上, 符号位不变,其余各个位取反。

[+1] = [00000001]原 = [00000001]反

[-1] = [10000001]原 = [11111110]反

可见如果一个反码表示的是负数, 人脑无法直观的看出来它的数值. 通常要将其转换成原码再计算.

1.2.3、补码

正数的补码跟原码一样,负数的补码是在其原码的基础上, 符号位不变, 其余各位取反, 最后再+1. (即在反码的基础上+1)

[+1] = [00000001]原 = [00000001]反 = [00000001]补

[-1] = [10000001]原 = [11111110]反 = [11111111]补

对于负数, 补码表示方式也是人脑无法直观看出其数值的. 通常也需要转换成原码在计算其数值.

1.3、浮点数运算

浮点数其实就是数学中用科学计算法表示数字的方式,比如1000,可以表示为 1.0*103。

下面当中,其中 1≤|M|<10

2、计算机结构

2.1、CPU结构

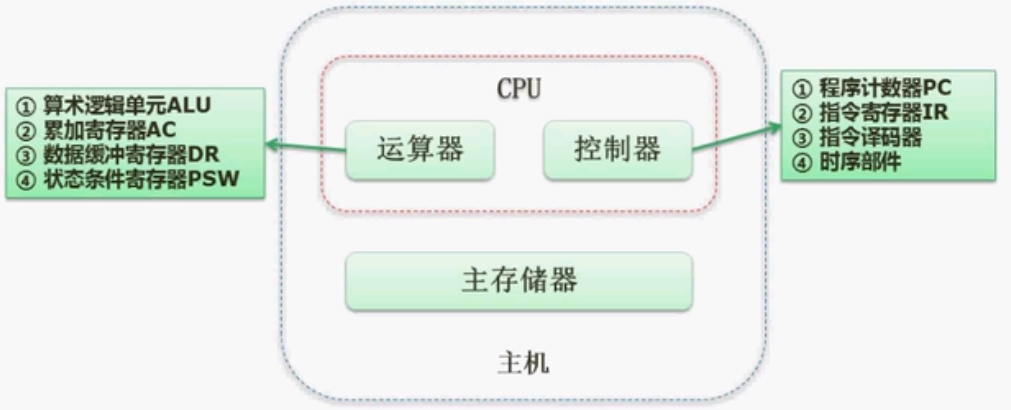

CPU由运算器和控制器组成

运算器:

算术逻辑单元(ALU):负责对数据进行算术和逻辑运算,暂时存储计算结果等。

累加寄存器(AC):当ALU执行算术或是逻辑运算的时候,为ALU提供一个工作区。

数据缓冲寄存器(DR):对内存进行读写操作时,用来暂存数据的。作为CPU和内存,外围设备之间数据的中转站。是CPU和内存,外围设备之间在操作速度上的缓冲

状态条件寄存器(PSW):存储运算过程中相关的标志,比如一些运算涉及到进位、溢出、中断等待,涉及到一些状态的信息。

控制器:

程序计数器PC:具有寄存信息和记数两种功能,又称为指令计数器。用来存放下一条指令所在的单位的地址的地方。

指令寄存器IR:当CPU执行一条指令时,先把它从内存储器取到指令缓存器中,再送入到指令寄存器中,然后经过指令译码器的译码,从而产生各种微操作。

地址寄存器(AR):保存当前CPU所访问的内存单元的地址,由于CPU和内存在操作速度上的差异,所以需要使用AR保持地址信息,直到内存的读写操作完成。

指令译码器(ID):指令译码器对指令的操作码和地址码进行解析,转换成相应的操作信号,控制各部件的工作,完成所需要的功能。

2.2、各种不同的计算机体系结构分类

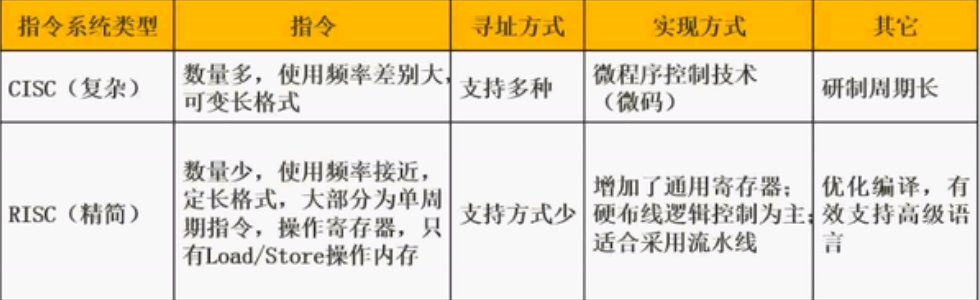

2.3、CISC和RISC指令系统的特点

CISC是计算机非常老旧时的指令系统,一台计算机可能就是专门为某个机构定制的,指令多且复杂。

RISC适应于大众使用,指令简化,追求高效率和简单

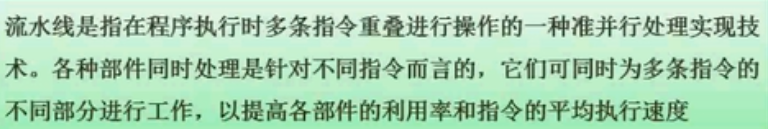

3、流水线

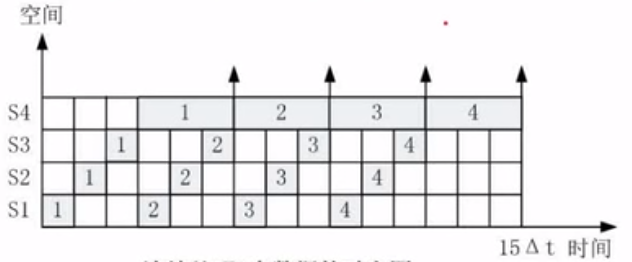

执行一条指令会分为:取指、分析、执行三个步骤:

![]()

由于取指、分析、执行三个步骤是由不同的部件完成的,所以第1 条执行分析时,此时取指部件可以空余出来执行第 2 条执行的取指步骤。

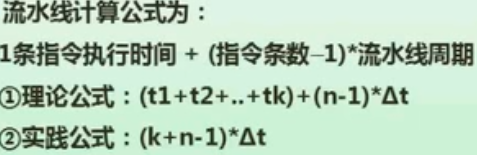

3.1、流水线的周期和计算指令执行时间

例题:

上面题目中,流水线周期为 2ns,100条指令的执行时间为:(2+2+1)+(100-1)*2 = 203ns,或者是(3+100-1)*2 = 204ns。一般来说都是采用理论公式计算,但也可能会采用实践公式来算。

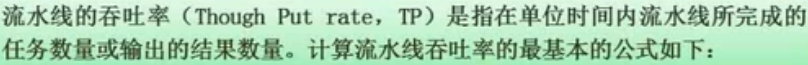

3.2、流水线的吞吐率

,流水线的最大吞吐率计算公式:

,流水线的最大吞吐率计算公式:![]()

如上面例题,流水线的吞吐率为:100/203 ,最大吞吐率为:1/2

3.3、流水线的加速比

![]()

![]()

如上面例题,加速比为:(2+2+1)*100/203

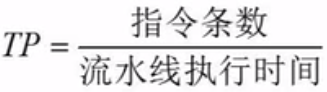

3.3、流水线的效率

上图中,流水线的效率为:((1+1+1+3)*4)/(15*4),也就是说,流水线的效率在空间图上可以看做是:工作占用时空区/总的时空区

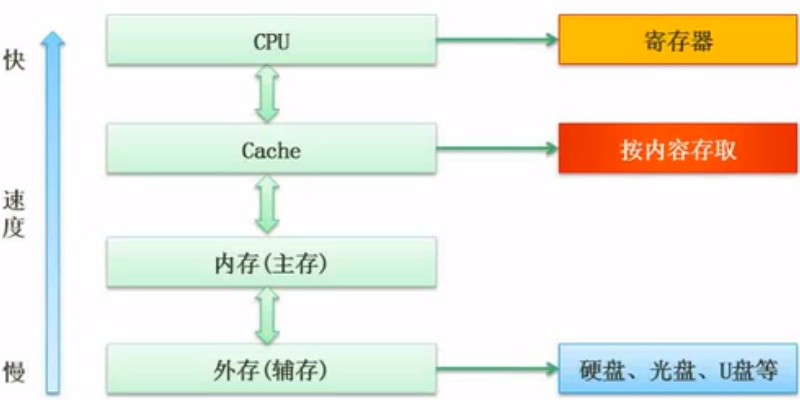

4、计算机的层次化存储

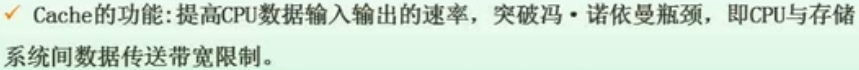

4.1、cache

![]() 有时候并不会把寄存器放在存储体系中,所以可以将 cache 认为是访问速度最快的层次,但如果有寄存器,实际上还是会选寄存器。

有时候并不会把寄存器放在存储体系中,所以可以将 cache 认为是访问速度最快的层次,但如果有寄存器,实际上还是会选寄存器。

![]()

电脑使用cache和主存储器时,平均周期的计算公式:

比如,对cache的访问命中率为 95%,cache的周期时间为 1ns,主存储器周期为 1000ns,那么此时系统的平均周期为:0.95*1 +(1-0.95)*1000 = 50.95ns

4.2、主存

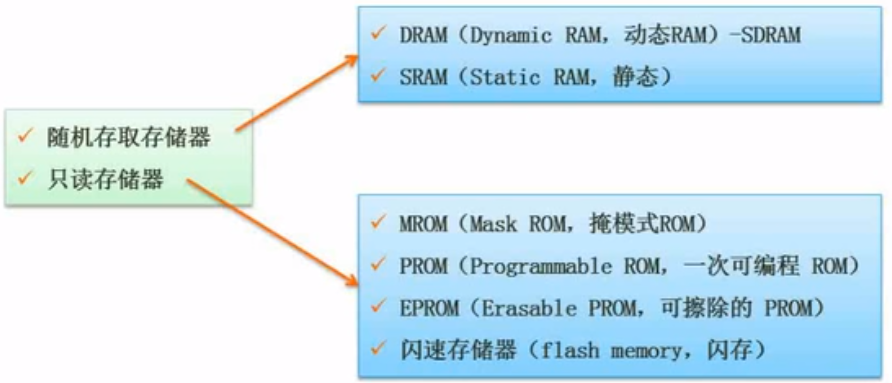

主存可分为随机存取存储器和只读存储器。计算机系统的主存主要由DRAM构成,SRAM主要组成cache。

RAM和ROM的应用:系统的内存一般由RAM和ROM组成,像cache一般是用静态RAM的因为需要高速的缓存,需要读写速度快,而主存的话一般是用动态ram,便于存储对读写速度每那么的快,而ROM则是存放一些系统程序的存储器,有只读功能,不可写,比如开机的时候的BIOS。外存有很多种如闪存USB的硬盘,还有SSD的固态硬盘等。

4.3、主存 -- 编址

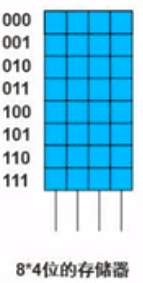

表示这个芯片有 8 个地址单元,每个地址空间有 4 个 bit 位信息,一共可以存储 32 bit 位信息。注意,这么一个存储器称之为一个芯片,每一行称之为 1 个地址单元或者内存地址,每 1 格就是 1 个 bit。

表示这个芯片有 8 个地址单元,每个地址空间有 4 个 bit 位信息,一共可以存储 32 bit 位信息。注意,这么一个存储器称之为一个芯片,每一行称之为 1 个地址单元或者内存地址,每 1 格就是 1 个 bit。

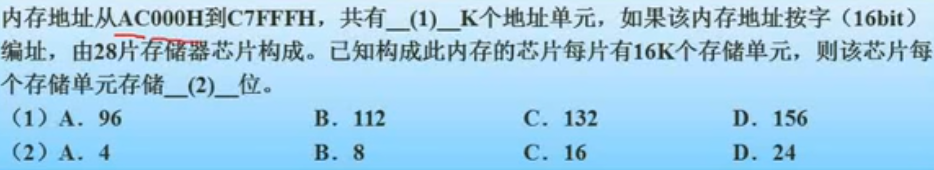

例题:

地址由AC000H到C7FFFH,由C7FFFH 减去 AC000H 得到的是多少,然后 +1,就是多少个地址单元,因为 1 个地址单元能表示 1 个地址,有多少个地址就有多少个地址单元。C7FFFH 和 AC000H 都是 16进制的数,相减得到是 1C000H,实际上就是1*164+12*163,然后再除以 K 即 210 就可以得到第一个空的答案:112。

如果该内存地址按字(16bit)编址,意思是每个地址单元有 16 位。由 28 片芯片构成,每个芯片有 16k 个存储单元,那么每个存储单元的存储位为:(112K * 16)/(28*16K)= 4

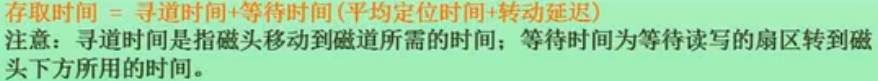

4.4、磁盘结构与参数

先在磁道读取完数据,然后才能对数据进行处理。

例题:

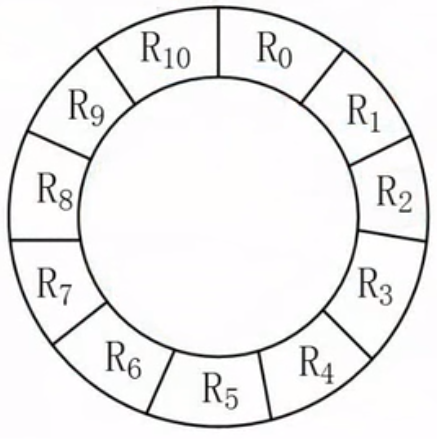

旋转周期为33ms,则旋转1个扇区需要3ms。磁头处于R0开始处,则读取R0需要3ms,但每个记录的处理也要3ms,处理完R0后磁头已经到了R2开始处,因为要顺序处理,所以需等到磁头重新旋转至R1开始处,需等待30ms,然后读取R1,处理R1,以此类推,计算后可以得到答案为 366ms。

旋转周期为33ms,则旋转1个扇区需要3ms。磁头处于R0开始处,则读取R0需要3ms,但每个记录的处理也要3ms,处理完R0后磁头已经到了R2开始处,因为要顺序处理,所以需等到磁头重新旋转至R1开始处,需等待30ms,然后读取R1,处理R1,以此类推,计算后可以得到答案为 366ms。

如果信息存储可以优化分布,那就可以像左图,处理完R0后,磁头刚好处于R1开始处,可以立即处理R1,不用等待。以此类推,计算后可得此时答案为 66ms。

如果信息存储可以优化分布,那就可以像左图,处理完R0后,磁头刚好处于R1开始处,可以立即处理R1,不用等待。以此类推,计算后可得此时答案为 66ms。

5、计算机总线

根据总线所处的位置不同,总线通常被分成三种类型,分别是:内部总线、系统总线(数据总线、地址总线、控制总线)、外部总线

数据总线:数据总线用于传递数据信息。

地址总线:地址总线用于传输地址的信息,如要访问外设的内存地址、某个外设的地址等。由于地址通常由CPU提供的,所以地址总线一般是单向传输的。

控制总线:顾名思义,控制总线用于传送控制信号。例如CPU向内存或输入输出接口电路发出的读写信号;又如,输入输出接口电路向CPU发送的用于同步工作的联络信号等。

6、串联系统和并联系统

串联系统模型:

![]()

可靠性:![]() ,即为各个子系统的可靠性相乘的值

,即为各个子系统的可靠性相乘的值

可靠性:

可靠性:![]() 当所有系统都失效时,系统才失效。

当所有系统都失效时,系统才失效。

7、CRC与海明校验码

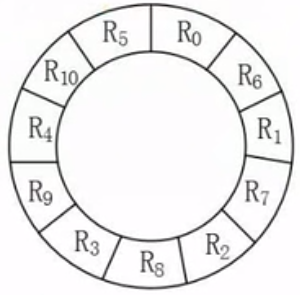

7.1、码距

在整个编码系统中,所有的任意的两个码字之间,一个码字最少需要改变多少个位才能变成另一个码字,这个位数就是码距。

7.2、循环校验码CRC

循环校验码可以检错但不能纠错。

在信息传送时,会在其尾部加入校验信息,加入校验码后的数据与生成多项式进行模2相除,余数如果为0则认为没出错,否则认为传输过程中出错了。

7.3、海明校验码

海明校验码可以检错也可以纠错。

根据接收到的数据的信息位生成校验位,如果生成的校验位和得到的校验位不一致,则认为出错。两个校验位信息异或,得到是多少就认为是哪个位置出错。

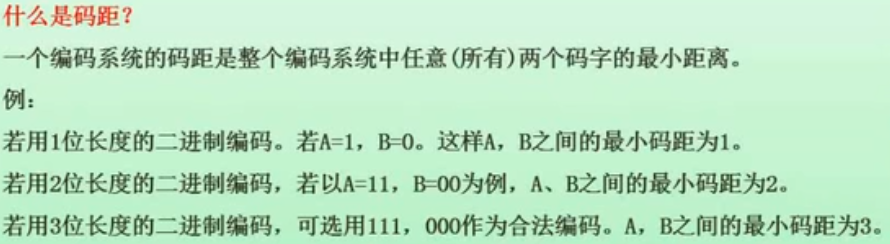

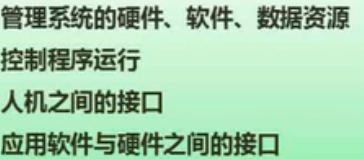

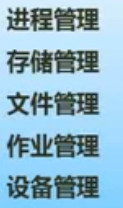

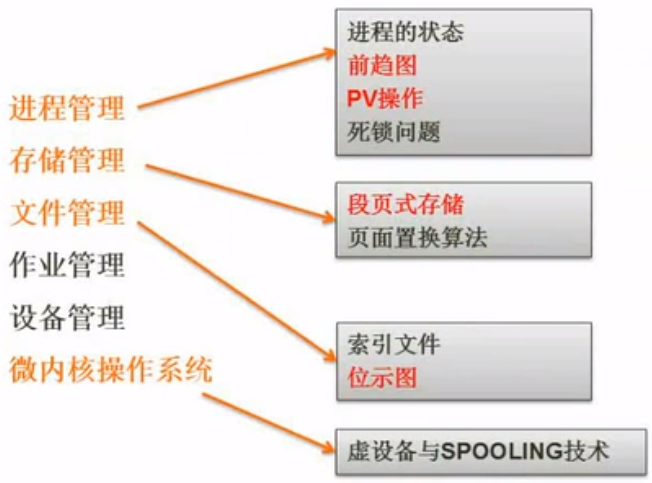

8、操作系统

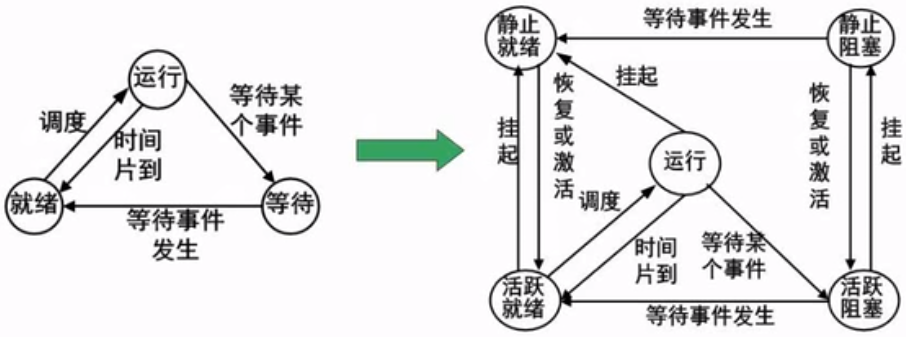

8.1、进程的状态