软件触发中断(NVIC->STIR)

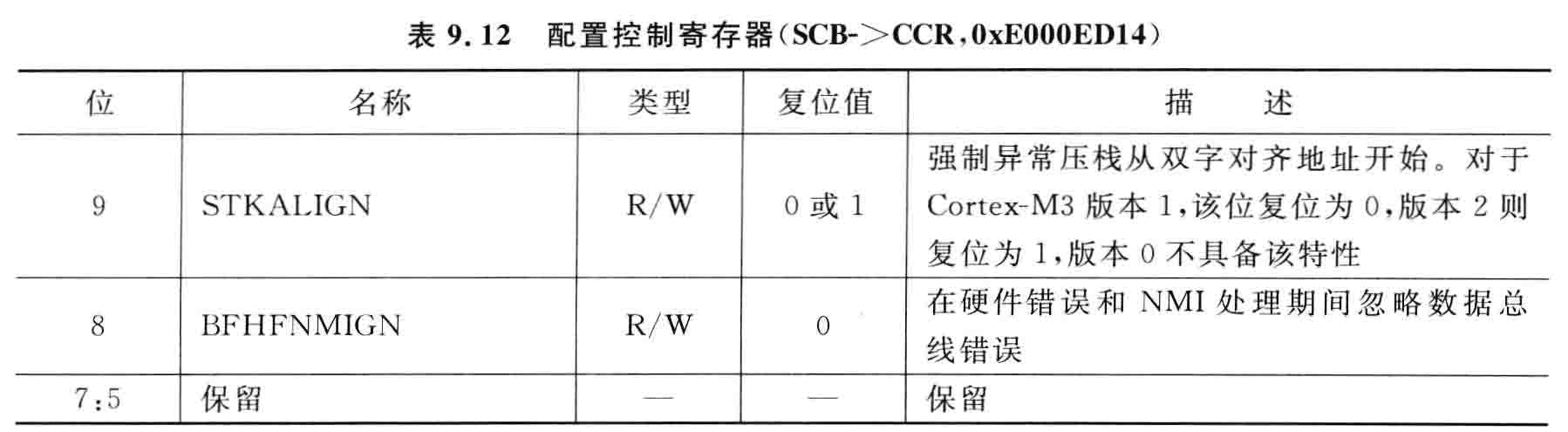

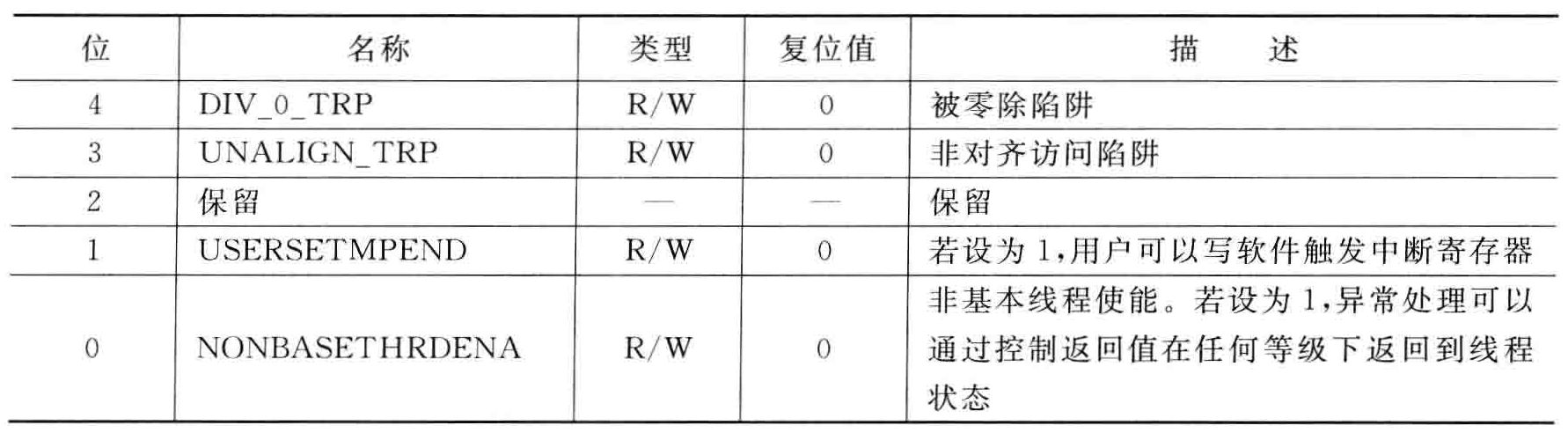

首先我们要打开这个功能,怎么打开?看表!

那么代码怎么写呢?

1 /* 使能软件触发中断功能 */ 2 SCB->CCR |= 0x1 << 1; 3 4 #if 0//中断向量表示例 5 #pragma language = extended 6 #pragma segment = "CSTACK" 7 8 #pragma location = ".intvec" 9 __root const intvec_elem __vector_table[64]= 10 { 11 {.__ptr = __sfe("CSTACK")}, 12 __iar_program_start, 13 /****** Cortex-M4 Processor Exceptions Numbers *******************************/ 14 NMI_Handler, /*!< -14 02 Non Maskable Interrupt */ 15 HardFault_Handler, /*!< -13 03 Hard Fault Interrupt */ 16 MemManage_Handler, /*!< -12 04 Memory Management Interrupt */ 17 BusFault_Handler, /*!< -11 05 Bus Fault Interrupt */ 18 UsageFault_Handler, /*!< -10 06 Usage Fault Interrupt */ 19 0,0,0,0, /*!< Reserved Interrupt */ 20 SVC_Handler, /*!< -05 11 SV Call Interrupt */ 21 DebugMon_Handler, /*!< -04 12 Debug Monitor Interrupt */ 22 0, /*!< Reserved Interrupt*/ 23 PendSV_Handler, /*!< -02 14 Pend SV Interrupt */ 24 SysTick_Handler, /*!< -01 15 System Tick Interrupt */ 25 /****** smt specific Interrupt Numbers ****************************************/ 26 TWDG_IRQHandler, /*!< 00 16 W-WATCHDOG Interrupt */ 27 IWDG_IRQHandler, /*!< 01 17 I-WATCHDOG Interrupt */ 28 FPU_IRQHandler, /*!< 02 18 FPU Interrupt */ 29 fft_irqhandle, /*!< 03 19 FFT Interrupt */ 30 vad_irqhandle, /*!< 04 20 VAD Interrupt */ 31 dnn_irqhandle, /*!< 05 21 DNN Interrupt */ 32 ADC_IRQHandler, /*!< 06 22 ADC Interrupt */ 33 SDC_IRQHandler, /*!< 07 23 SDIO Interrupt */ 34 DMA_IRQHandler, /*!< 08 24 DMA Interrupt */ 35 IIS_DMA0_IRQHandler, /*!< 09 25 IIS_DMA0 Interrupt */ 36 IIS_DMA1_IRQHandler, /*!< 10 26 IIS_DMA1 Interrupt */ 37 SCU_IRQHandler, /*!< 11 27 SCU Interrupt */ 38 EXTI0_IRQHandler, /*!< 12 28 EXT0 Interrupt */ 39 EXTI1_IRQHandler, /*!< 13 29 EXT1 Interrupt */ 40 0, /*!< 14 30 ALC Interrupt */ 41 TIM0_IRQHandler, /*!< 15 31 TIMER0 Interrupt */ 42 TIM1_IRQHandler, /*!< 16 32 TIMER1 Interrupt */ 43 TIM2_IRQHandler, /*!< 17 33 TIMER2 Interrupt */ 44 TIM3_IRQHandler, /*!< 18 34 TIMER3 Interrupt */ 45 UART0_IRQHandler, /*!< 19 35 UART0 Interrupt */ 46 UART1_IRQHandler, /*!< 20 36 UART1 Interrupt */ 47 UART2_IRQHandler, /*!< 21 37 UART2 Interrupt */ 48 I2C0_IRQHandler, /*!< 22 38 IIC2 Interrupt */ 49 I2C1_IRQHandler, /*!< 23 39 IIC1 Interrupt */ 50 GPIO5_IRQHandler, /*!< 24 40 GPIO5 Interrupt */ 51 SPI1_IRQHandler, /*!< 25 41 SPI1 *Interrupt */ 52 GPIO0_IRQHandler, /*!< 26 42 GPIO0 Interrupt */ 53 GPIO1_IRQHandler, /*!< 27 43 GPIO1 Interrupt */ 54 GPIO2_IRQHandler, /*!< 28 44 GPIO2 Interrupt */ 55 GPIO3_IRQHandler, /*!< 29 45 GPIO3 Interrupt */ 56 GPIO4_IRQHandler, /*!< 30 46 GPIO4 Interrupt */ 57 0, /*!< 31 47 PSRAM Interrupt */ 58 0, /*!< 32 48 ICACHE Interrupt */ 59 IIS1_IRQHandler, /*!< 33 49 IIS1 Interrupt */ 60 0, /*!< 34 50 SCACHE Interrupt */ 61 IIS3_IRQHandler, /*!< 35 51 IIS3 Interrupt */ 62 0, /*!< 36 52 IIS2 Interrupt */ 63 /********************************* END ****************************************/ 64 }; 65 #endif 66 67 /* 触发TWDG中断 */ 68 NVIC->STIR = 0; 69 70 /* 触发IWDG中断 */ 71 NVIC->STIR = 0x1; 72 73 //其他的就不写了