之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习,将感悟记于此,如有错误,欢迎指出、讨论。

一、关于时钟引脚

FPGA芯片一般有好几组时钟引脚 CLK [0..N] [p,n],我的理解是:首先,时钟必须由外部晶振通过CLK引脚输入到FPGA的时钟网络,至于选用哪一组CLK,主要看FPGA哪个bank对时钟要求最为苛刻;其次,一般用p端,n端由quartus置位三态;再次,对于简单的系统,只有一组CLK输入作为系统主时钟,其他时钟引脚空置,或者作为某些高带载能力的时钟的输出口(是否可作为输出口,要看芯片手册);然后,复杂系统,可以有不同源的时钟分别从不同CLK引脚输入,只是猜想,没实践过,个人认为这样不好,因为FPGA的核心就是同步;另外,不要把CLK引脚和全局时钟、区域时钟什么的混为一谈,一个是时钟输入引脚,一个是内部时钟走线;最后,CLK引脚进去的走线肯定进过优化的(H型铜皮,专用的、直达每个触发器的布线资源),所以能做到小的抖动和偏斜,带载能力

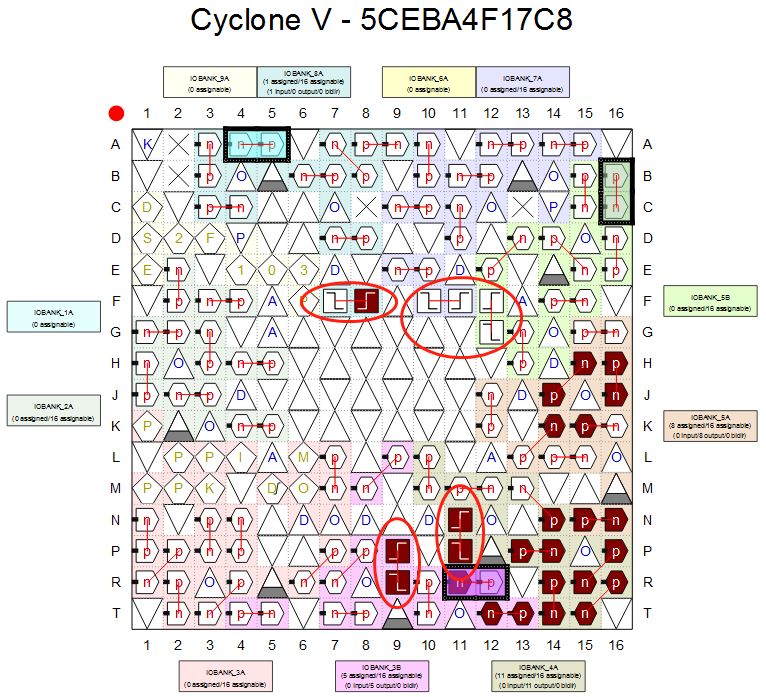

图1

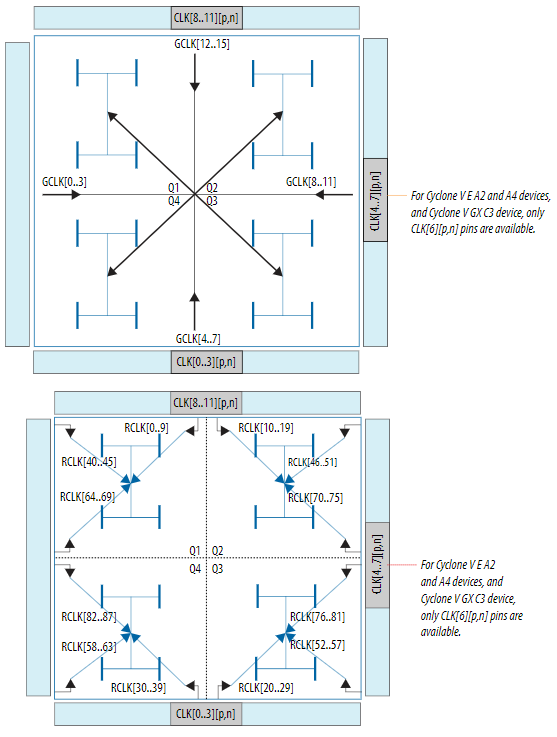

图2

图1所示:红圈为时钟输入引脚,当然,从时钟引脚输入的时钟必定首先进入全局时钟网络,再进一步驱动区域时钟,或者由PLL进行分/倍频==;三个黑色方框内PLL输出引脚,我的理解是:这几组引脚的布线也经过了优化,可以使PLL分/倍频后输出的时钟信号质量较好。

图2所示:CLK9p作为系统唯一的外部输入时钟源,图3

图4

******注意******

- 常规操作:外部晶振—>时钟引脚—>PLL—>区域时钟、各个模块、输出(待验证和完善,我也迷)。

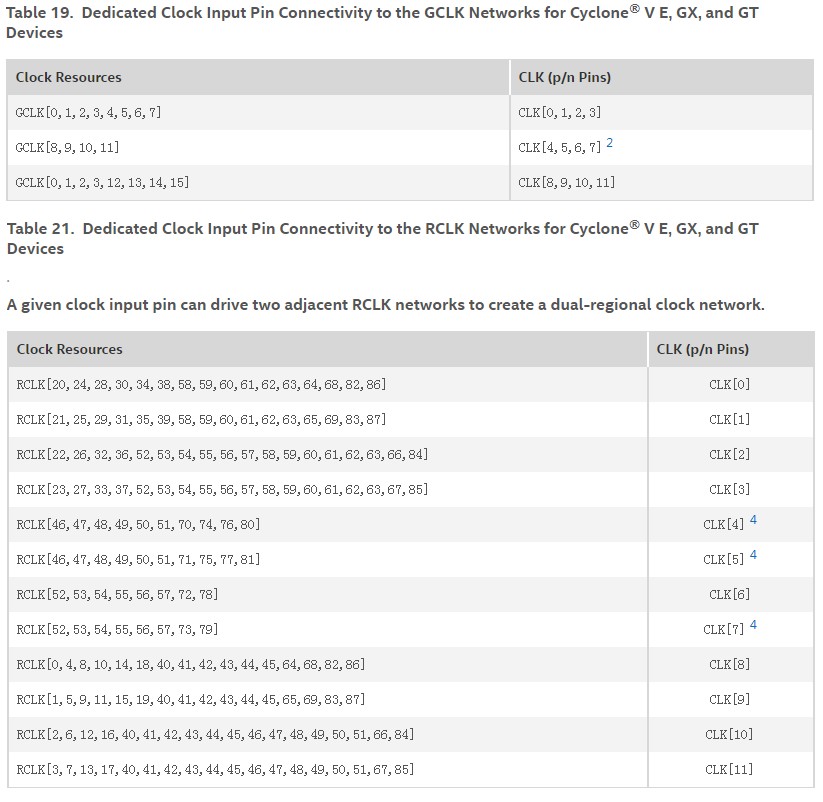

- 关于CLK引脚选择:不是所有的CLK引脚都可以连接到所有的全局/区域时钟网路,见图5。

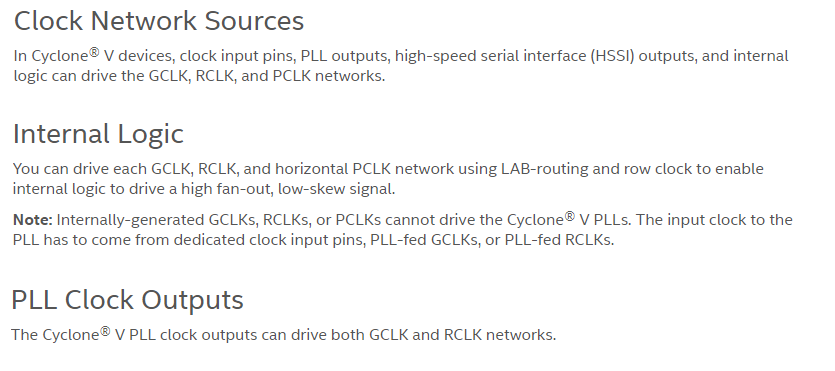

- 关于PLL:不是所有始终都可以驱动PLL,详见手册,如图6所示。

图5

图6

三、时钟资源的使用、分配

20181101提出

- 疑问:编写逻辑电路,或者布局布线时,我怎么知道某个时钟具体使用了哪种、哪个网络?以及怎么人为地控制使用具体某个网络?

20181102补充

- 除非是时钟资源(尤其是全局时钟资源)紧张,或者需要进行时序优化,否则,一般不用过于关心这些资源怎么使用的,quartus会根据电路逻辑,自动选择最优的布局布线。

- 实际上,根据硬件电路和逻辑电路,也能推断出用了多少全局时钟、区域时钟。

- 比如:clk0=50MHz,然后它在几个always中都被用到,而这几个always占用的逻辑资源分布在不同的区域,那么这个时钟应该是全局时钟;再比如:clk1=100MHz,它只在一个always里被使用,或使用它的逻辑资源都在一个区域,那么clk1应该是区域时钟。

- https://www.cnblogs.com/zuilangsanshu/