存储器

存储器分类

按存储介质分类

存储介质主要有半导体器件、磁性材料、光盘。

半导体存储器

存储元件由半导体器件组成的存储器称为半导体存储器。

现代半导体存储器都用超大规模集成电路工艺制成芯片。

-

-

- 优点:体积小、功耗低、存取时间短。

- 缺点:是一种易失性存储器,断电时存储的信息容易丢失。近年来已研制出用非挥发性材料制成的半导体存储器,克服了信息易失的弊病。

-

半导体存储器按其所使用材料的不同,又可分为:

-

-

- 双极半导体存储器:高速。

- MOS半导体存储器:高集成度,制造简单、成本低、功耗小,故被广泛使用。

-

磁性存储器

磁表面存储器

磁表面存储器是在金属或塑料基体的表面涂一层磁性材料作为记录介质,工作时,磁层随载磁体高速运转,用磁头在磁层上进行读/写操作。故称为磁表面存储器。

按载磁体形状的不同可分为:

磁盘(将圆形的磁性盘片装在一个密封盒子里,就是硬盘了)。

磁带(录音机磁带)

磁鼓(已淘汰)。

特点:非易失。

磁芯存储器

磁芯是由硬磁材料做成的环状元件,在磁芯中穿有驱动线和度读出现。功耗太大,已被半导体存储器取代。

光盘存储器

光盘存储器是应用激光在记录介质(磁光材料)上进行读写的存储器。

纪录密度高、耐用性好、可靠性高,所以应用越来越广泛。

按存取方式分类

随机存储器(RAM,Random Access Memory)

- 特征:

可读可写,任何一个存储单元的内容都可以随机存取,存储时间、顺序与存储单元的物理地址无关。

计算机的内存(主存)一般都采用RAM。

根据存储信息的原理不同,又可将其分为静态RAM和动态RAM。

静态RAM(SRAM):以触发器原理寄存信息。

动态RAN(DRAM):以电容充放电原理寄存信息。

只读存储器(ROM,Read Only Memory)

- 特征

能读出其存储的信息,不能对其重新写入。

这种存储器一旦写入了原始信息之后,在程序执行过程中,只能将内部信息读出,而不能随意重新写入新的信息去改变原始信息。

- ROM派生出的新类型

- PROM,Programable Read Only Memory,可编程只读存储器。

- EPROM,Erasable Programable Read Only Memory,可擦除可编程只读存储器。

串行访问存储器

- 特征

在对存储单元进行读/写操作时,需按其物理位置的先后顺序寻找地址。

例如:磁带。不论信息处在哪个位置,读写时必须从其介质的起始位置开始查找。故这类串行访问的存储器又称为顺序存取存储器。

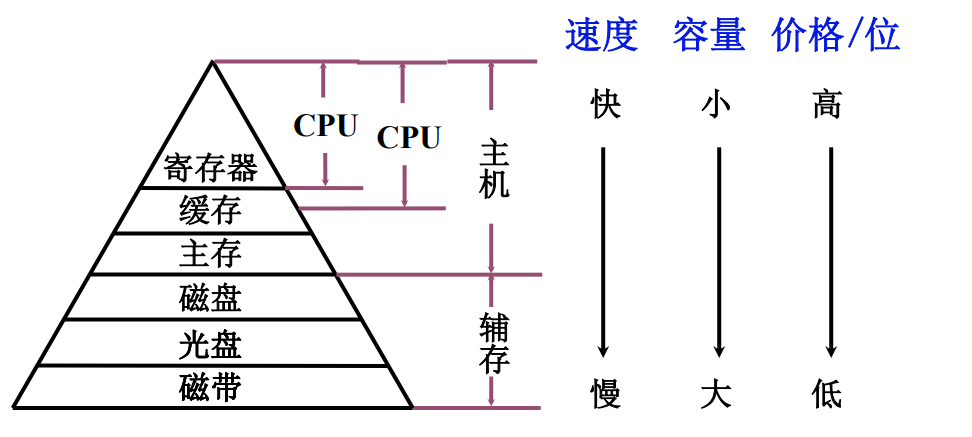

按在计算机中的作用分类

存储器的层次结构

- 寄存器:寄存器通常都制作在CPU芯片内部,寄存器中的数据直接在CPU内部参与运算,CPU内部可以有十几个,甚至几十个寄存器。

- 主存:用来存放将要参与运行的程序和数据。

- 缓存:主存与CPU的速度茶具较大,为了是它们之间的速度更加匹配,在主存与CPU之间插入了一种比主存速度更快、容量更小的高速缓冲存储器(Cache)。

- 缓存-主存层次主要解决CPU与主存速度不匹配的问题。

- 主存-辅存主要解决存储系统的容量问题。

主存储器

主存的基本组成

- 根据MAR(存储器地址寄存器)中的地址访问某个存储单元时:要经过地址译码、驱动等电路,才能找到所需访问的存储单元。

- 将存储单元中的数据读出时:需经过读出放大器,才能将被选中的存储单元中的存储字送到MDR(存储器数据寄存器)。

- 将MDR中的数据写入存储单元时:数据必须经过写入电路才能真正写入到被选中的存储单元中。

- 图中的驱动器、译码器、读写电路均集成在半导体存储器芯片中。

主存与CPU的联系

- MAR、MDR集成在CPU芯片中。

- 存储芯片和CPU芯片通过总线连接。

CPU从主存储器读取信息的过程:

首先CPU将该信息的地址送至MAR,经由地址总线送至主存,然后发出读命令。

主存接到读命令后,得知需将该地址单元的内容读出,将该地址单元的内容读取至数据总线上,传送至MDR。(随后MDR中的信息要作何处理由CPU决定,与主存无关)。

CPU向主存储器写入信息的过程

首先CPU将该信息要写入的主存单元的地址经由MAR发送至地址总线,并将信息送入MDR。

然后向主存发出写命令,主存接到写命令后,便将数据总线上的信息写入到地址总线指出的对应的主存单元中。

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX