Verilog HDL(Hardware Description,硬件描述语言)

HDL语言是对已知硬件电路的文本形式编写,编写前对所需实现的硬件电路“胸有成竹”

相比C语言,最显著的区别在于HDL语言具备硬件设计的概念:

互连(connectivity):-wire型变量描述各个模块之间的端口与网线连接关系

并发(concurrency):-可以有效地描述并行的硬件系统

时间(time):-定义了绝对和相对的时间度量,可综合操作符具有物理延迟

HDL中可用于综合描述的语句:

可综合四大法宝:always, if-else, case, assign

可综合禁止出现:function, for, fork-join, while 主要用于test bench(仿真)

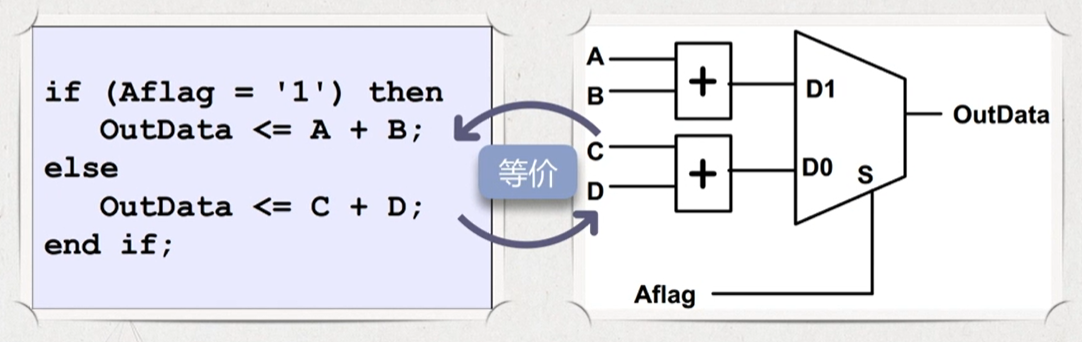

if-else硬件结构电路:

映射的硬件结构:Multiplexing Hardware(多路选择器),输出结果由输入的选择条件决定

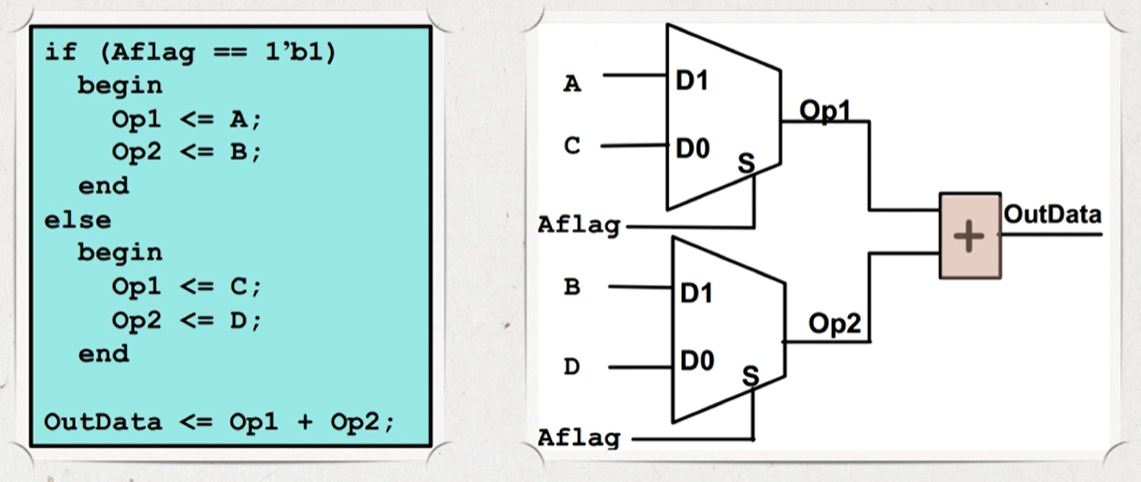

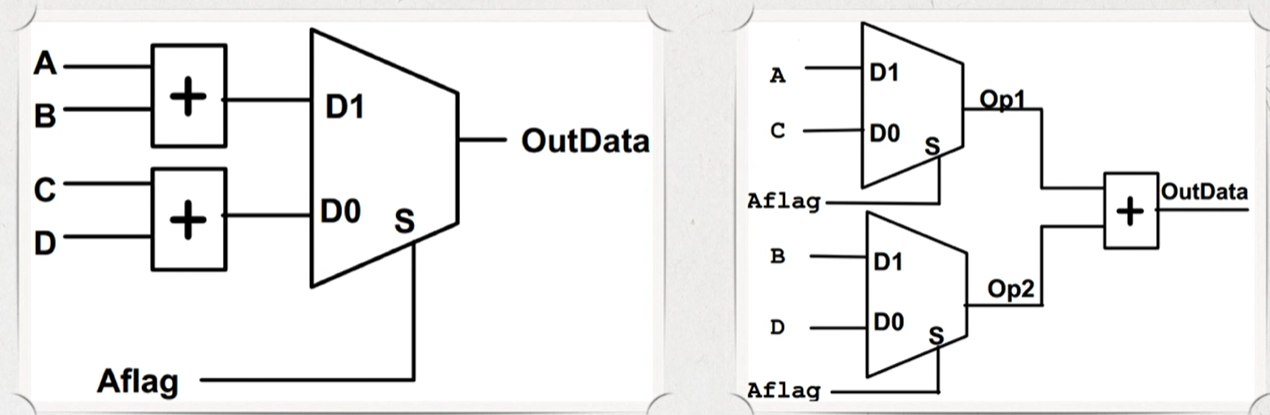

进行修改:if-else映射的硬件结构:减少一个加法器,减少硬件的面积

分析两种电路的优劣:

分析两种电路的传播延迟(OutData的延迟):(左)数据通路延迟 一个加法器和一个选择器,控制通道只有一个选择器;

(右)数据通路是一个选择器和一个加法器,控制通道是一个选择器和一个加法器;

相比右侧电路因为加法器减少而使得面积较少,但是在传播延迟方面右侧电路在控制通道上比左侧电路更多延迟(即如果Aflage到来的较晚,第二种(右)电路比第一种电路(左)性能差)。

(根据输入约束,小心设计:先“加”后选,先“选”后“加”)

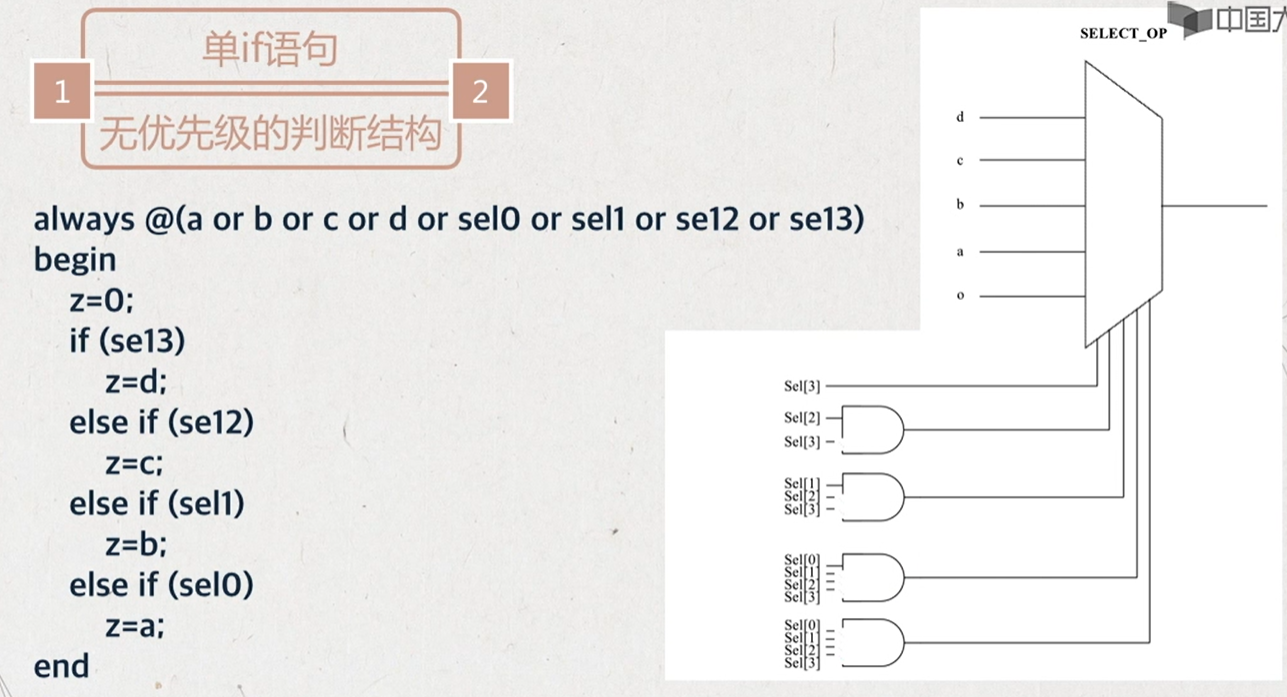

单if语句:无优先级的判断结构

推荐初学者尽量使用单if语句(if...else if..else if...)描述多条件判断结构

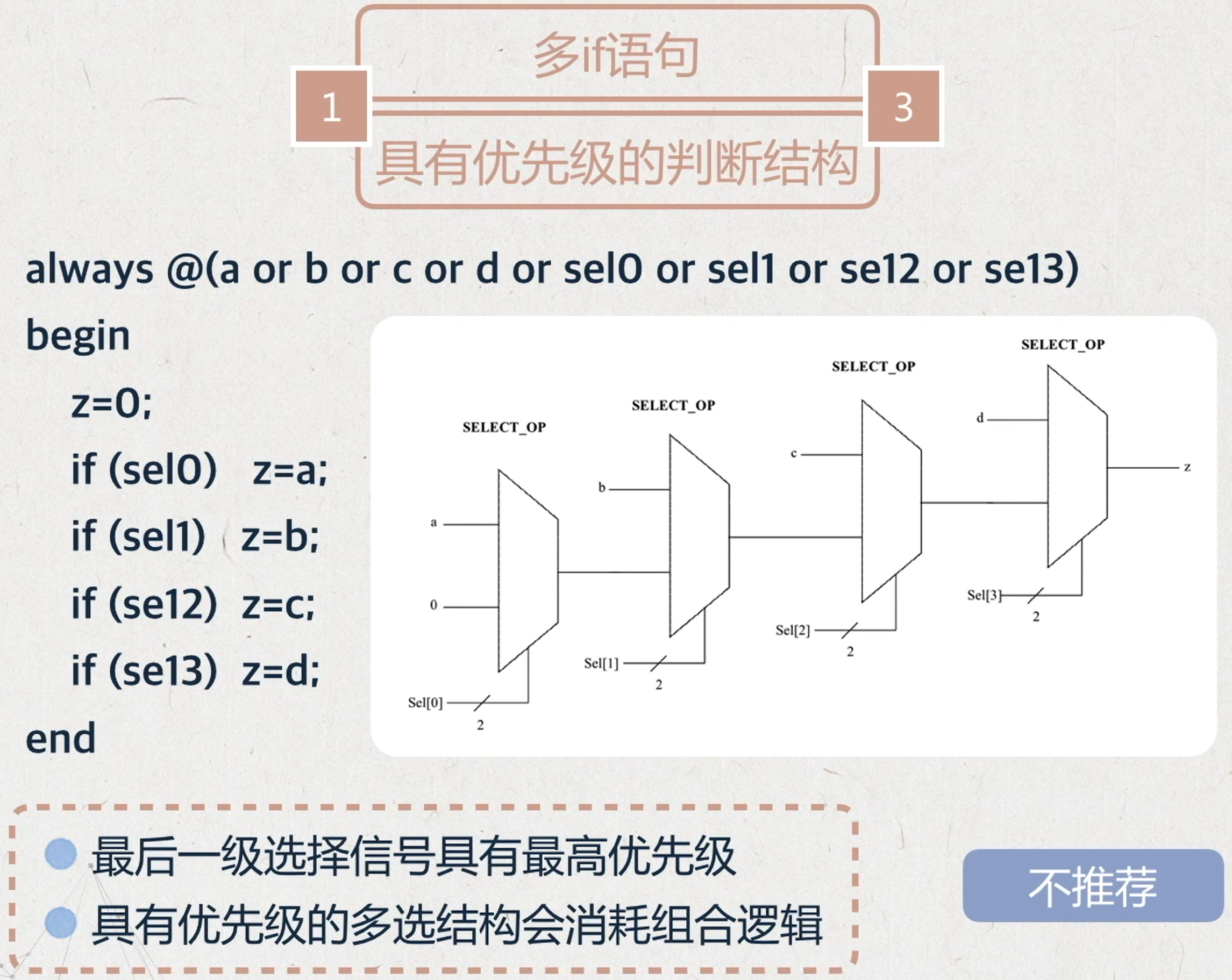

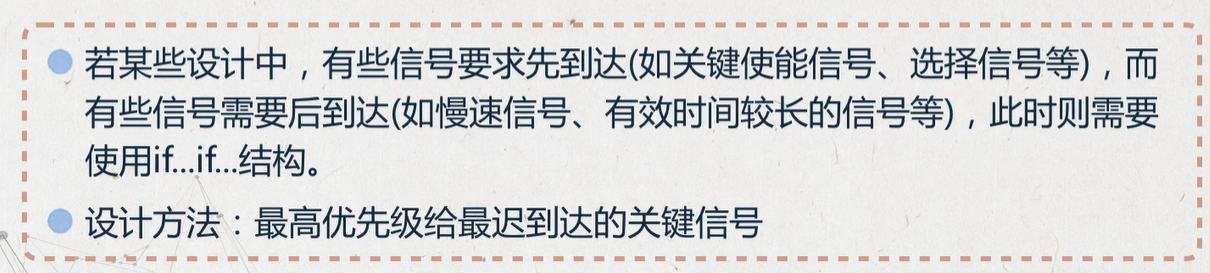

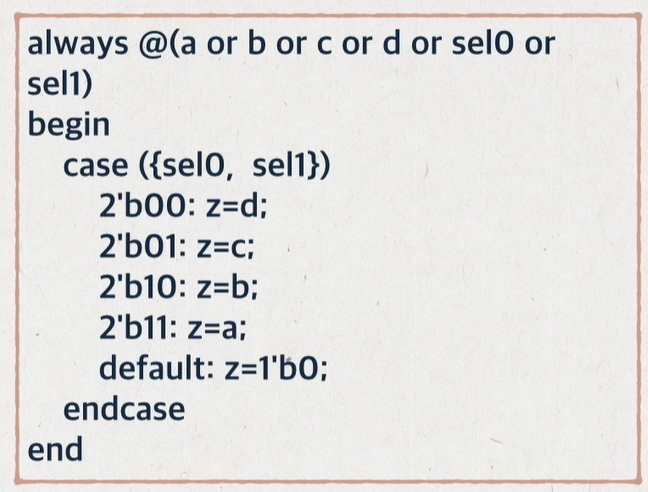

多if语句:具有优先级的判断结构

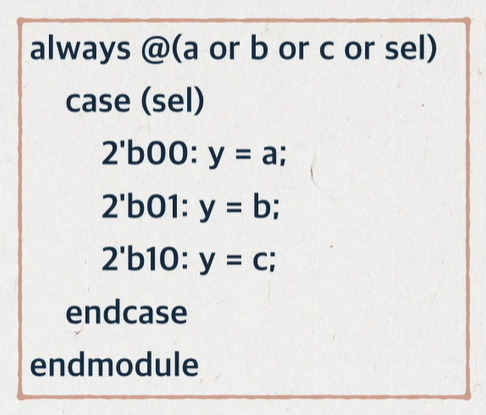

case :无优先级的判断结构

与单if语句的区别:条件互斥 多用于指令译码电路

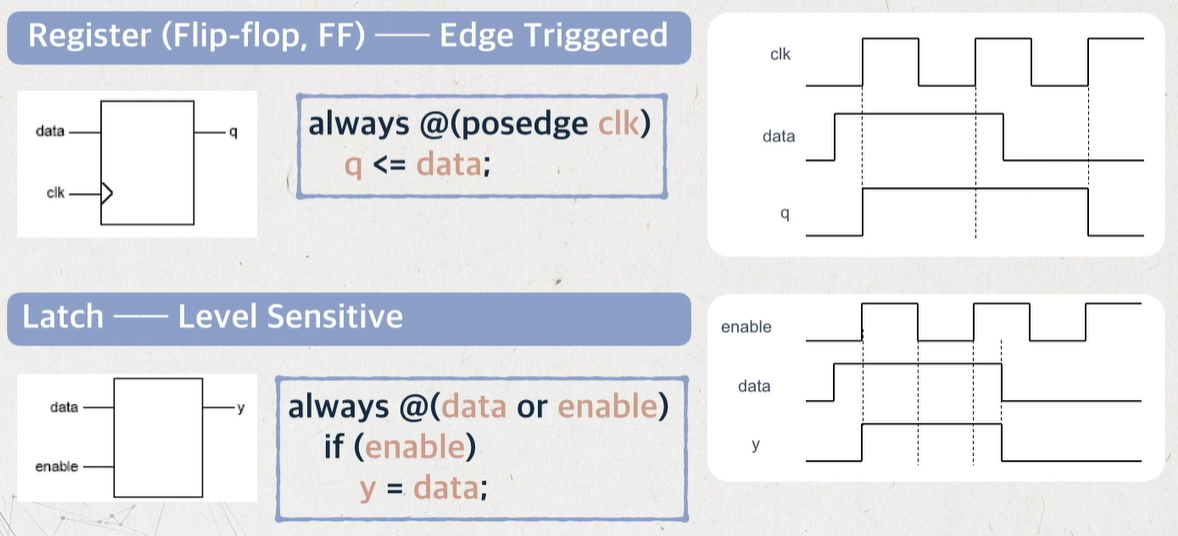

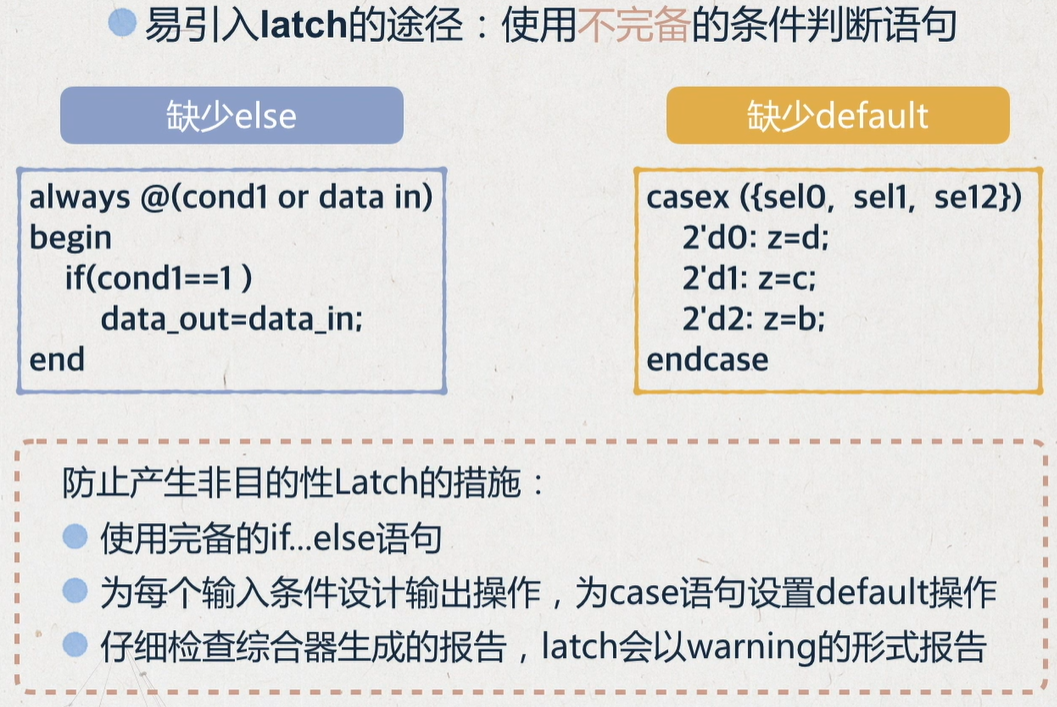

Latch 谨慎使用

综合器很难解释latch,因此,除非特殊用途,一般避免引入latch.

latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时 latch保持输出状态。DFF由时钟沿触发,同步控制。

latch容易产生毛刺(glight),DFF则不易产生毛刺。

latch将静态时序分析变的极为复杂。

一般的设计规则是:在绝大多数设计中避免产生latch。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以只要能用D触发器的地方,就不用latch。

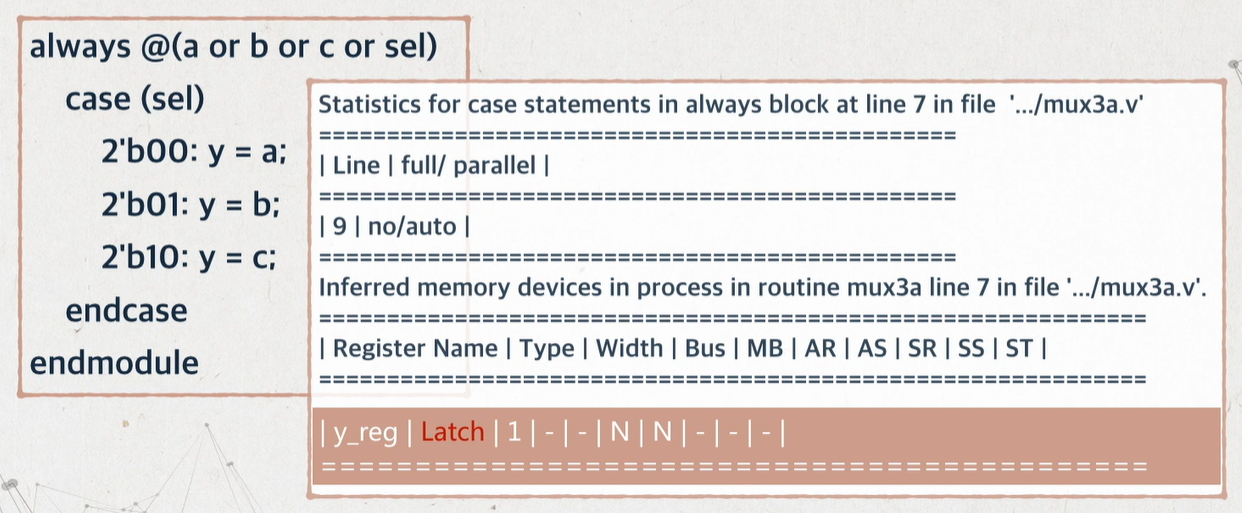

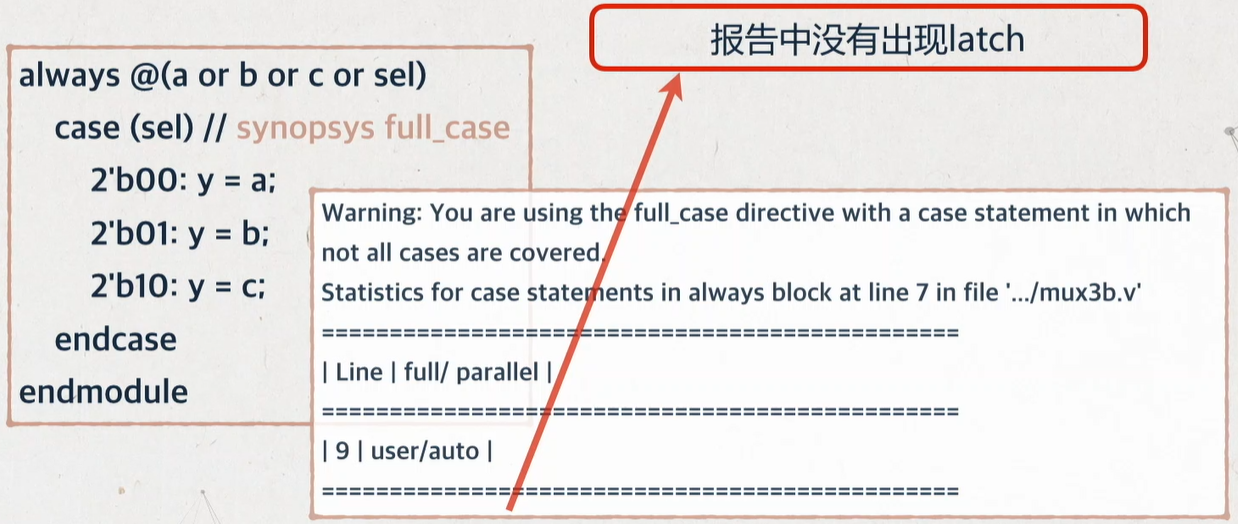

综合器的full-case和parallel-Case指令(除电路结构设计本身外,我们还可以通过控制综合器对电路结构进行指定)

第一种问题:

实例:交通控制红绿灯,只有红、绿、黄三种情况,不会出现第四种

红绿灯只有三种情况,但是两比特的位数可以表示四种情形:一种情况没有结果,分支赋值不完备情况

使用full case :告诉综合器,当前case结构所列条件已完备

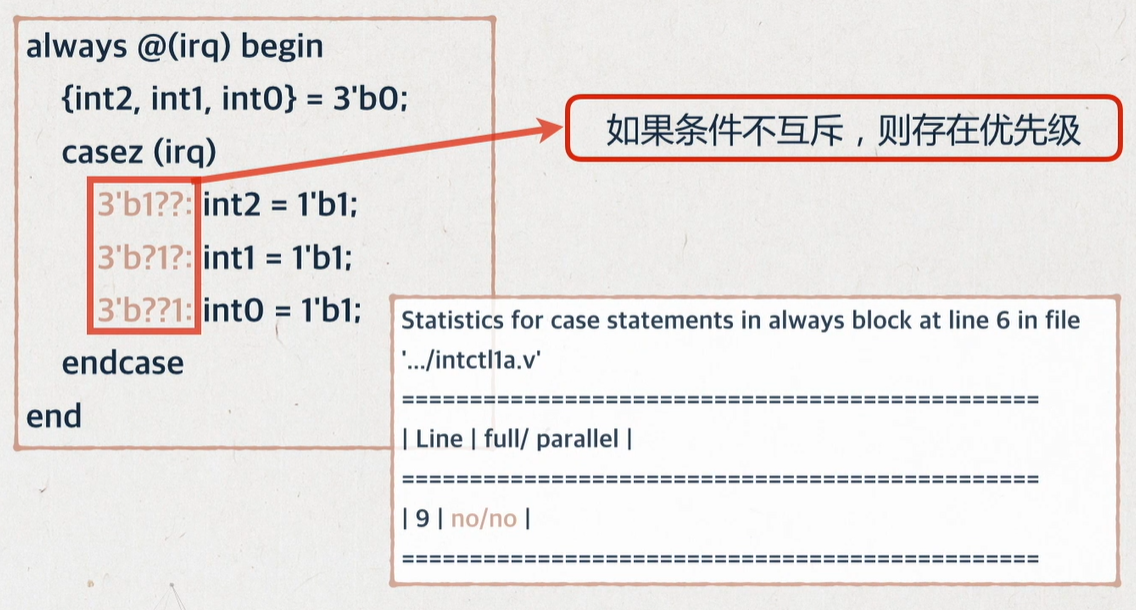

第二种问题:三位比特,可以表达8种情形,但是代码中只需要三类case,存在可能的互斥问题(重复)

casez并不是并行的分支电路。

使用Parallel-Case:告诉DC,所有的条件均是互斥,且并行,无优先权

报告中显示:电路为用户指定的并行分支结构

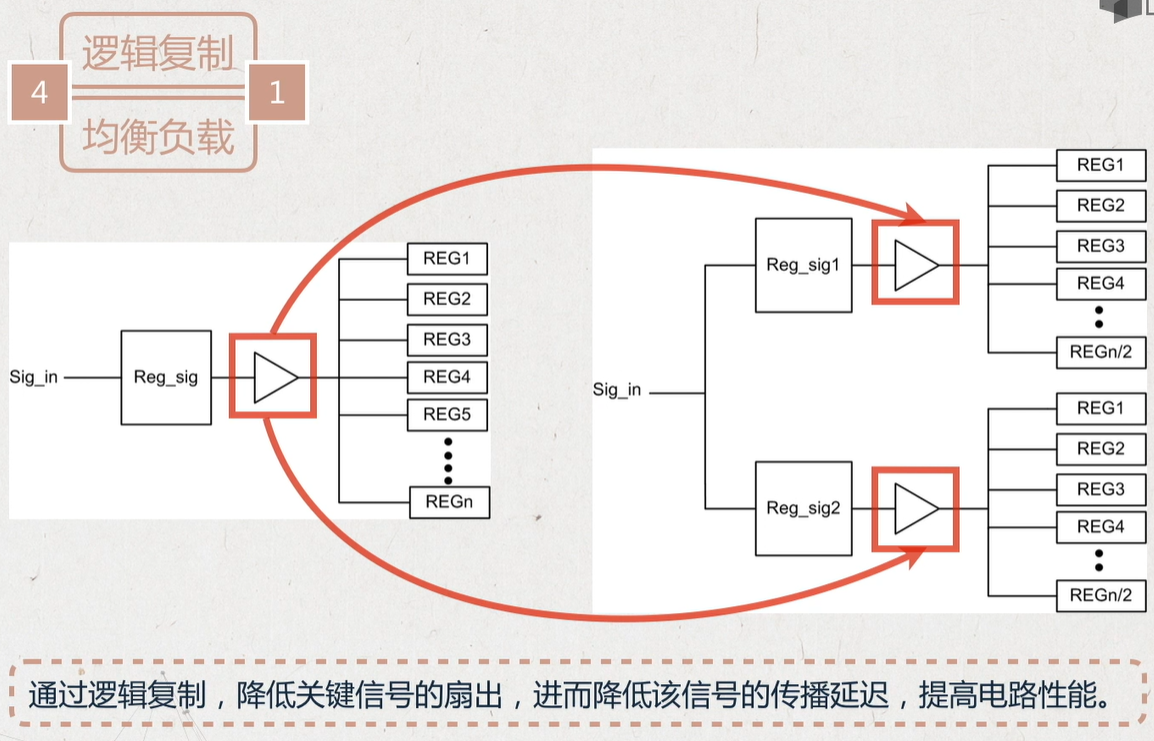

逻辑赋值与负载均衡

发现某个电路的逻辑负载比较重,可以通过

发现电路中存在较多的公共单元,通过资源共享,减少面积

但是共享会导致性能下降,所以要根据性能和面积进行取舍。

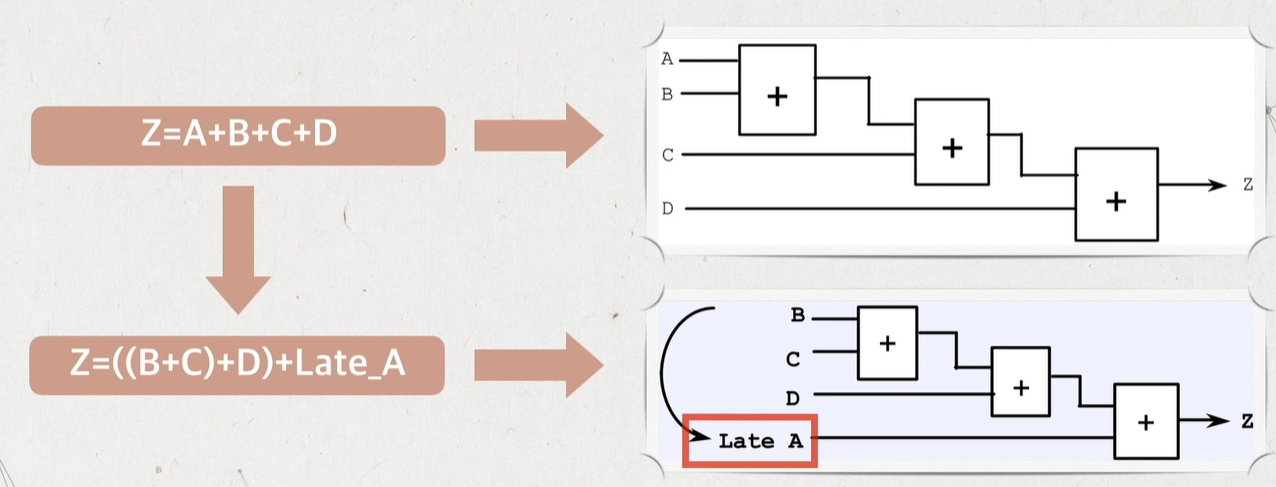

资源顺序重排与降低传播延时

根据延迟进行数据的重排,A信号到来较晚,可以根据延迟把它放到后面,隐藏其延迟

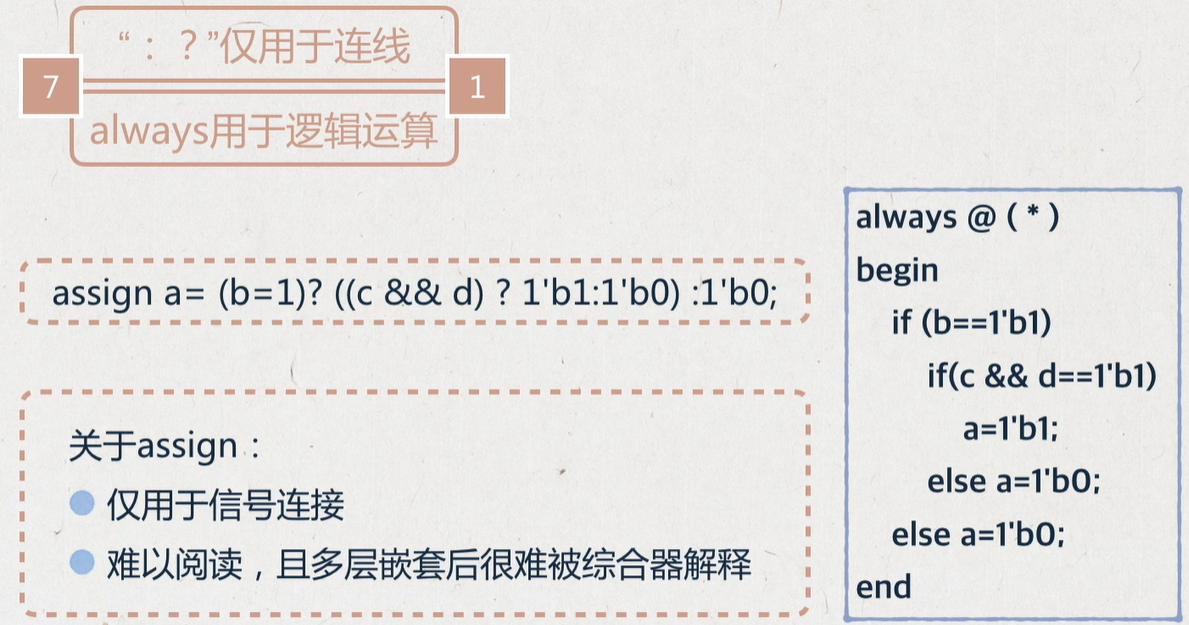

在代码书写过程中尽可能的使用always块来描述电路,

assign仅用来实现连线,少用:?这种形式,难以阅读,很难被解释。

可综合风格

1、完整的always敏感信号列表

所有的组合逻辑或锁存的always结构必须有敏感信号列表。这个敏感信号列表必须包含所有的输入信号。

原因:综合过程将产生一个取决于敏感列表中左右其他值2的结构,它将可能在行为仿真和门级仿真间产生潜在的失配。

2、每个always敏感信号列表对应一个时钟

在综合过程中,每个Verilog always敏感信号列表只能对应一个时钟。

原因:这是将每一个过程限制在单一寄存器类型的要求。

3、不允许Wait声明和#delay声明

Wait声明语句,不论是清楚还是含糊,都不能用于可综合设计。

原因:从RTL级转换到gate级的综合工具一般都不支持Wait声明和#delay声明,为了有效的综合,这些语句应该避免。

例外:在不需要进行综合的行为模块中,如测试模块、表示行为的虚拟器件模块中可以使用。

4、在时序电路中必须使用非阻塞赋值(<=),组合逻辑电路必须使用阻塞赋值(=)。

模块划分

1、分开异步逻辑与同步逻辑

建议分开异步逻辑与同步逻辑

原因:避免综合时的问题,讲话约束和编码难度。

例外:不可应用于非综合模块中(例如:总线模块,总线监视器或是模拟模块)除非他们被设计用来综合仿真。

2、分开控制逻辑和存储器

建议控制逻辑和存储器逻辑分成独立的模块

原因:便于高层的存储器模块的使用和便于重新描述为不同的存储器类型。

总结:

初学者误区:-verilog代码当作程序,把电路设计当成编程。

如何书写高性能Verilog HDL:牢记并理解可综合“四大法宝”所应对的硬件结构

写前,确认电路指标是什么:性能?面积?

硬件思维方式,代码不再是一行行的代码而是一块一块的硬件模块。

对所需实现的硬件电路做到“胸有成竹”;