正确的开发流程:

1、设计定义

2、设计输入

3、分析和综合(检查语法等的错误,不严谨问题)

4、功能仿真(modelsim-altera版)

5、布局布线(代码布局到对应芯片中)

6、时序仿真(门级仿真)(modelsim-altera)

7、时序约束

8、IO分配以及配置文件的生成

9、配置(烧写FPGA)

10、在线调试

例子:

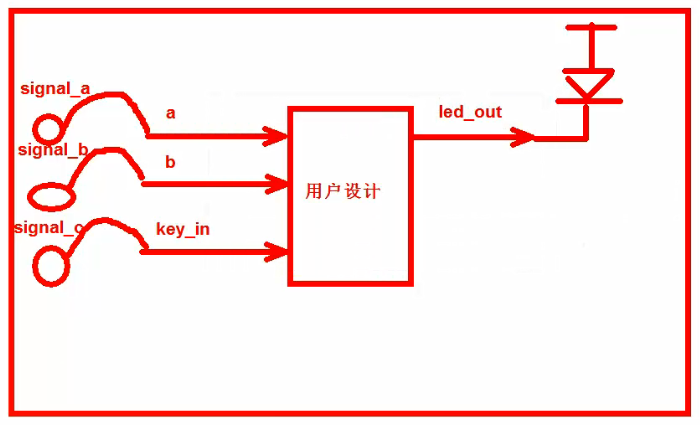

1、设计定义 通过按键控制LED灯的亮灭(二选一多路器)

两个输入IO,a、b。可以是高电平,也可以是低电平

输入按键按下时,LED灯与a端口状态保持一致。

输入按键释放时,LED灯与b端口状态保持一致。

2、设计输入

led_test.v

1 module led_test(a,b,key_in,led_out); //待测试模块 2 3 input a;//输入端口A 4 input b;//输入端口B 5 6 input key_in;//按键输入,实现输入输出通道的选择 7 8 output led_out;//led控制端口 9 10 //当key_in == 0 , led_out = a 11 12 assign led_out = (key_in == 0) ? a : b; 13 14 endmodule

3、进行分析和综合,检测逻辑和语法错误

testbench

led_test_tb.v

1 `timescale 1ns/1ps 2 3 module led_test_tb; 4 5 //激励信号定义,对应连接到待测试模块的输入端口 6 reg signal_a; 7 reg signal_b; 8 reg signal_c; 9 10 //待检测信号定义,对应连接到待测试模块的输出端口 11 wire led; 12 13 //实例化待测试模块 14 led_test led_test0( 15 .a(signal_a), 16 .b(signal_b), 17 .key_in(signal_c), 18 .led_out(led) 19 ); 20 21 //产生激励 22 initial begin //三个输入信号的八种组合状态 23 signal_a = 0; signal_b = 0;signal_c = 0; 24 #100; //延时100*1纳秒 25 signal_a = 0; signal_b = 0;signal_c = 1; 26 #100; //延时100*1纳秒 27 signal_a = 0; signal_b = 1;signal_c = 0; 28 #100; //延时100*1纳秒 29 signal_a = 0; signal_b = 1;signal_c = 1; 30 #100; //延时100*1纳秒 31 signal_a = 1; signal_b = 0;signal_c = 0; 32 #100; //延时100*1纳秒 33 signal_a = 1; signal_b = 0;signal_c = 1; 34 #100; //延时100*1纳秒 35 signal_a = 1; signal_b = 1;signal_c = 0; 36 #100; //延时100*1纳秒 37 signal_a = 1; signal_b = 1;signal_c = 1; 38 #200; //延时200*1纳秒 39 $stop; //停止仿真系统 40 end 41 42 endmodule

3、进行分析和综合,检测逻辑和语法错误

5、布局布线

6、门级仿真,配置仿真条件 slow慢速 电压1.2V 85°C的条件

8、IO配置

FPGA芯片引脚与电路端口一一配置