PCIe协议和SATA协议都是分层协议,分为物理层,数据链路层,传输层,命令层和应用层。

硬件工程师主要关注物理层、数据链路层和传输层。所有CMD/data由应用层和命令层打下来,每向下走一层,多一层封装和变换,最后通过差分总线传输出去。

PCIe协议:

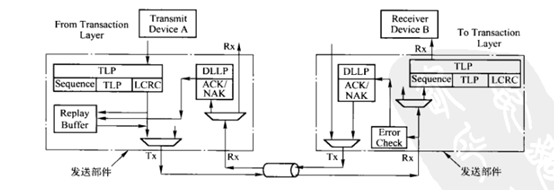

应用层和命令层打下来的CMD/data以TLP的格式封装起来,送给数据链路层,链路层给其加上sequence前缀和CRC后缀,成为一个完整的数据报文结构,送到物理层,经过8b/10b或者128b/130b编码后发送出去。关键点在于数据链路层有一个发送buffer,这个buffer可以存储一定量的TLP。每个传输层打下来的TLP首先送到这个发送buffer中,然后再发送给物理层。接收端也有一个接收buffer,可以一连串的接收多个TLP。如此,发送端无需等待接收端的回应,就可以先打多个TLP出去,接收端可以一股脑收起来,一个一个处理,如果接收正确,回复一个ACK DLLP(DLLP是另一种数据结构,用来进行一些控制信息的沟通,不用来传递CMD/data,DLLP由数据链路层自动生成,发送给对方的数据链路层,传输层不知道DLLP的存在),发送端收到这个DLLP,可以择机清空发送buffer中对应的TLP。如果接收端接收到错误的TLP,则回复NACK DLLP,发送方看到之后择机将发送buffer中对应的TLP重新发一遍。这带来的好处有以下:

(1) 发送端多个TLP可以pipe起来。一个TLP无需等待前一个TLP传完并收到ACK DLLP回应,就可以先发出去。反正有buffer可以先存着,物理层有空就发。

(2) 两个设备可以同时给对方打TLP,即全双工通信。一个设备发送TLP的时候,另一个设备无需被动等待,它可以发自己的TLP。 总线两端的设备地位是对等的,谁都可以给对方打CMD或者传data。

上图:PCIe的数据链路层结构

SATA协议:

以上说的两个好处,正好对应SATA总线的两个弱点:

(1) SATA总线发送端不存在pipe。host一个FIS(类似PCIe协议中的TLP)打下去之后,只有device端回复收到,并且通过CRC校验之后(通过R_OK原语,类似PCIe的ACK DLLP),host才能打下一笔FIS。

(2) SATA总线两端是不对等的,存在host和device的区别,只能主机给device打CMD,不能device给主机打CMD。而且不论是host还是device,一方发送FIS的时候,另一方只能处于接收状态,不能发FIS出去。这就是半双工通信。假如host正往device里面写data,device不可能在此时给host传data的。所以同一时刻,SATA的Rx和Tx只有一根线上是有效数据(payload)。

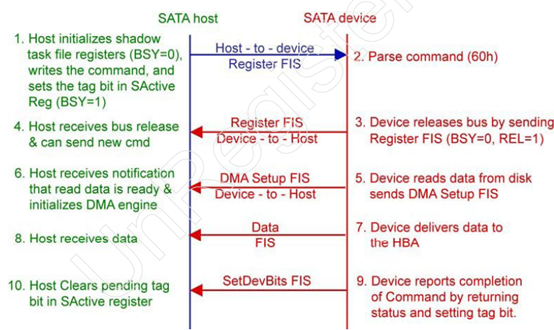

下图是SATA的一笔NCQ read CMD的总线传输。HOST通过Register FIS把CMD打下来,device收到之后,回复一个Register FIS。Device准备好data后,发送DMA setup FIS 告知host,然后发送data FIS,将数据送给host。传完数据,device发送一个set device bits FIS告知host。整个过程中,不论是host还是device,TP层只能一次发一个FIS,也不存在双方同时给对方发FIS的可能。