flash操作不同于sram,sram类似于在使用ram ip核(quartus/vivado)时生成的模块直接对存储操作,flash操作都是基于控制器的指令来的。flash在编程(写数据)之前是需要对芯片擦除(也就是写1),因为编程操作只能把1变成0,而不能把原本是0的位变成1。

基本的命令:擦除命令/编程命令/读取命令(读取命令分为读取数据和读取寄存器)

基本操作格式:命令+[地址]+[数据] //地址和数据是可选的

flash芯片擦除时按扇区来划分的;读取时一般芯片内部有一个buffer(大概几十个字节的大小),也就是说一般每次读取就是这个buffer的大小;program也是一样有一个buffer(具体的大小取决于各个芯片)。

flash芯片还有一些写保护功能(本测试不做验证,测试主要这对操作接口)。

-------------------------------------------------------------

flash分类:

并口flash

串行flash

norflash:容量小但速度快(这里的速度指读取的速度,尤其并口flash的读取和ram读取几乎没有区别)/一般用于存储系统,启动代码,bios之类

nandflash:容量大但速度低于nor/一般用于应用存储数据

-----------------------------------------------------------------

测试使用的cypress的flash芯片:以S25FS128S/S25FS256S为例

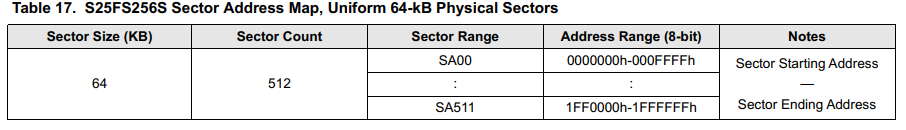

扇区划分模式,选择最简单的一种,便于操作:

注意: 该芯片读取时可以一个字节一个字节自累加读取模式(可以一直读完整个芯片再回到地址0继续循环下去):

另一种QuadIO Read一定要burst模式,也就是只能一组一组读取,地址在组内累加循环。

cypress的芯片一般都有模型可以下载:https://www.cypress.com/verilog/s25fs256s-verilog

这个芯片有多种读写接口模式:命令+地址+数据

1-1-1(默认模式/基本的spi模式)/1-4-4(QuadIO模式)/4-4-4(QPI模式)

【芯片读取数据时还可支持ddr操作,取决于具体的读取命令】

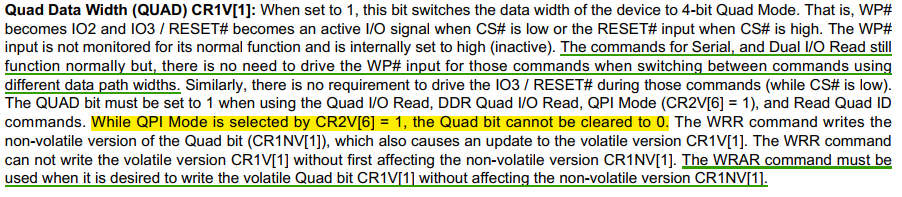

【QPI模式和QuadIO模式的区别:两者都需要开启四线操作(CR1V[1]),但QPI模式还要开启(CR2V[6]);

需要说明,CR2V[6]一旦assert会同时assert CR1V[1],CR1V[1] assert之后除非复位否则不会变为0】

芯片的工作状态由4个8bits配置寄存器控制:CR1V/CR2V/CR3V/CR4V

所有操作要通过SR1V状态寄存的查询结果作为判断成功结束的依据:

-------------------------------------------------------------

注意:spi模式io用了两个,qpi/quadio是4个。

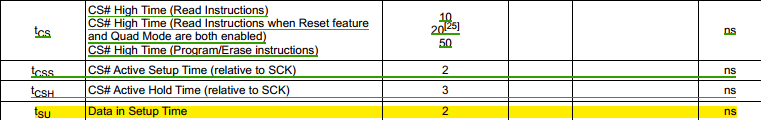

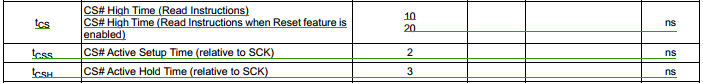

注意:片选信号csn需要提前且滞后时钟信号clk至少一个时钟周期。

SDR 时序:

DDR时序:

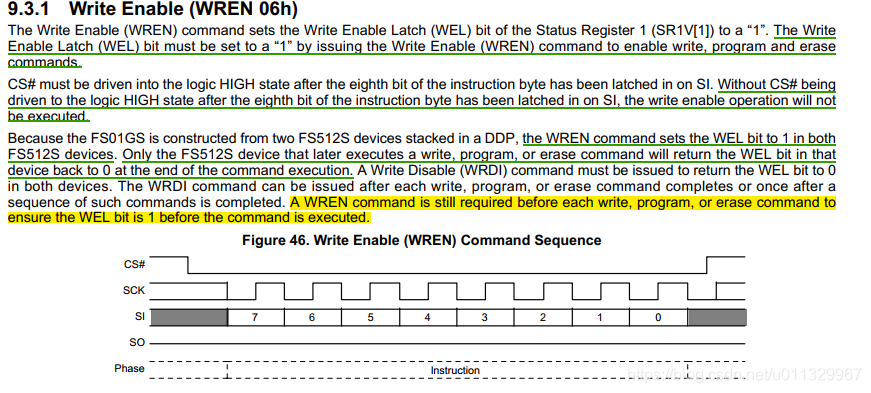

关于写使能是否在每次的擦除、编写前都需要执行一次:

虽然在寄存器定义里只说和WRENWRDI命令有关,但实际还是需要在每次执行擦写前进行一次写使能的。

S25FS128S:

S70FS01GS:

-------------------------------------------------------------

以对一个扇区的操作来验证flash芯片的基本功能,操作流程:

1、上电延时(等待芯片复位)->

2、设置工作模式(使能4字节模式)-> 1-1-1(SPI)

3、读取配置寄存器的默认值(验证基本的读取功能及芯片的工作状态)-> 1-1-1(SPI)

4、写入配置寄存器(需要注意此步骤之前需要先执行写使能操作/否则操作不成功)-> 1-1-1(SPI)

5、在新配置的模式下读取芯片id(验证当前设置是否成功)-> 4-4-4(QPI)

6、芯片指定扇区擦除-> 4-4-4(QPI)

7、第一次读取验证-> 4-4-4(QPI/SDR)

8、指定扇区编程-> 4-4-4(QPI)

9、指定扇区读取及验证-> 1-4-4(QaudIO/DDR)

10、进入芯片低功耗模式(测试完成)(1-1-1/SPI)

整个测试代码分为两部分:

底层的接口驱动(完成读写时序)+测试状态机(完成测试流程)

参考: