2018-2019-1 20165230 《信息安全系统设计基础》第四周学习总结

教材学习内容总结

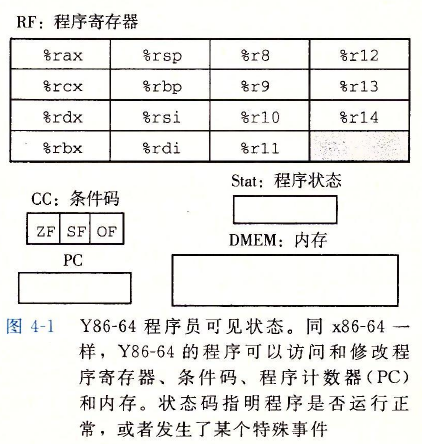

程序员可见状态

- Y86-64程序中的每条指令都会读取或修改处理器状态的某些部分。这

称为程序员可见状态,这里的“程序员”既可以是用汇编代码写程序的人,也可以是产生机器级代码的编译器。在处理器实现中,只要我们保证机器级程序能够访问程序员可见状

态,就不需要完全按照ISA暗示的方式来表示和组织这个处理器状态。 - 内存从概念上来说就是一个很大的字节数组,保存着程序和数据。Y86-64程序用虚

拟地址来引用内存位置。硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地

址,指明数据实际存在内存中哪个地方。

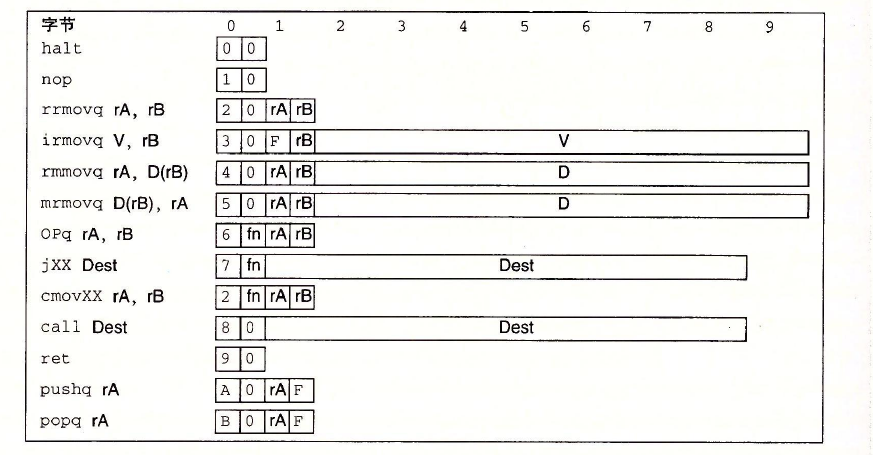

Y86-64指令和指令编码

- 指令编码长度从1个字节到10个字节不等。一条指令含有一个单字节的

指令指示符,可能含有一个单字节的寄存器指示符,还可能含有一个8字节的常数字。字段fn指明是某个整数操作(OPq)、数据传送条件(cmovXX)或是分支条件(jXX)。所有的数值都

用十六进制表示

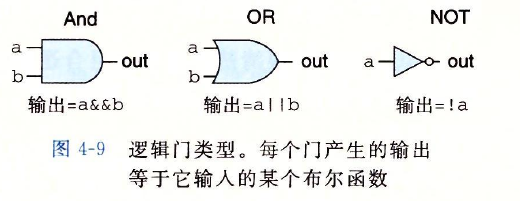

逻辑门

- 逻辑门是数字电路的基本计算单元。它们产生的输出,等于它们输人位值的某个布尔

函数。如图是布尔函数AND, OR和NOT的标准符号,C语言中运算符(2. 1. 8节)的

逻辑门下面是对应的HCL表达式:AND用&. &表示,OR用}l表示,而NOT用!表

示。用这些符号而不用C语言中的位运算符&,}和一,这是因为逻辑门只对单个

位的数进行操作,而不是整个字。虽然图中只说明了AND和OR门的两个输人的版本,

但是常见的是它们作为n路操作,n}2。不过,在HCL中我们还是把它们写作二元运算

符,所以,三个输人的AND门,输人为a.

b和c,用HCL表示就是a&&b&&co

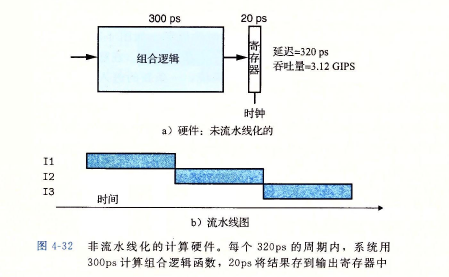

流水线及其实现方式

- 这里的“顾客”就是指令,每个阶段完成指令

执行的一部分。图给出了一个很简单的非流水线化的硬件系统例子。它是由一些执

行计算的逻辑以及一个保存计算结果的寄存器组成的。时钟信号控制在每个特定的时间间

隔加载寄存器。CD播放器中的译码器就是这样的一个系统。输人信号是从CD表面读出

的位,逻辑电路对这些位进行译码,产生音频信号。图中的计算块是用组合逻辑来实现

的,意味着信号会穿过一系列逻辑门,在一定时间的延迟之后,输出就成为了输人的某个

函数。

SEQ

SEQ的实现包括组合逻辑和两种存储器设备:时钟寄存器和随机访问存储器。

组织计算原则:从不回读。处理器从来不需要为了完成一条指令的执行而去读由该指令更新了的状态。

插入流水线寄存器

- 在创建一个流水线化的Y86-64处理器的最初尝试中,我们要在SEQ十的各个阶段之

间插人流水线寄存器,并对信号重新排列,得到PIPE一处理器,这里的“一”代表这个

处理器和最终的处理器设计相比,性能要差一点。PIPE一的抽象结构如图所示。流

水线寄存器在该图中用黑色方框表示,每个寄存器包括不同的字段,用白色方框表示。正

如多个字段表明的那样,每个流水线寄存器可以存放多个字节和字。同两个顺序处理器的

硬件结构中的圆角方框不同,这些白色的方框表示实际的硬件组成。

教材学习中的问题和解决过程

- 问题1:存储器和时钟有什么关系

- 问题1解决方案:

通过学习教材及蓝墨云资源中的视频,学习到:

- 时钟寄存器(简称寄存器)存储单个位或字。时钟信号控制寄存器加载输人值。

- 随机访问存储器(简称内存)存储多个字,用地址来选择该读或该写哪个字。随机访

问存储器的例子包括:1)处理器的虚拟内存系统,硬件和操作系统软件结合起来使

处理器可以在一个很大的地址空间内访问任意的字;2)寄存器文件,在此,寄存器

标识符作为地址。在IA32或Y86-64处理器中,寄存器文件有15个程序寄存器(%

rax一%r14)。

代码调试中的问题和解决过程

暂无

代码托管

https://gitee.com/BESTI-IS-JAVA-2018/20165230/commit/5dd42538867b45b2b037b6d2039c2cf622fd26d9

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第二周 | 30 | 1/1 | 8 | |

| 第三周 | 198/228 | 2/3 | 12/20 | |

| 第四周 | 80/308 | 2/5 | 10/30 | |

| 第五周 |