MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反。在使用这个 MAC IP核之前,首先确认下自己使用的网卡是支持千兆网卡还是百兆网卡,我自己的电脑是百兆网卡,百兆网卡只支持百兆速率的传输,要按照百兆网卡进行管脚配置。

管脚配置

根据数据手册P54、P55进行硬件管脚引出:

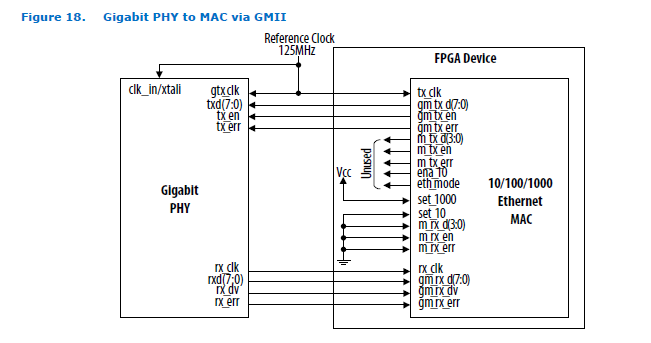

千兆网连接模式

千兆网的PHY芯片数据接收与发送管脚txd与rxd均是8bit,需要用pll倍频125M给PHY芯片的gtx_clk以及MAC IP核的tx_clk,PHY芯片会根据发送速率产生一个随路时钟给MAC IP核的rx_clk。

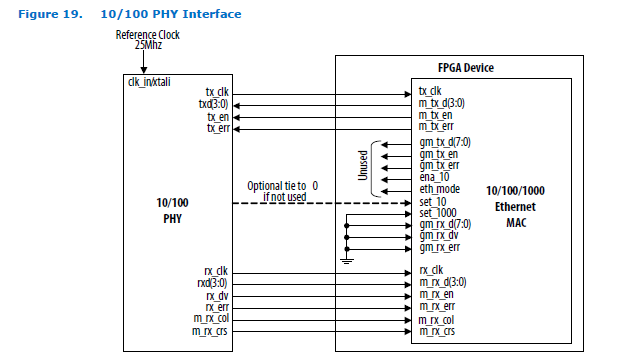

百兆网连接模式

百兆网的PHY芯片数据接收与发送管脚txd与rxd均是4bit,并且只需要给一个Reference Clock 至PHY芯片,PHY芯片就会产生25M的tx_clk与rx_clk至MAC IP核,这里注意要把m_rx_col 与m_rx_crs芯片管脚也引出来作为MAC IP核的m_rx_col 与m_rx_crs输入,要注意的是千兆网PHY芯片的使用是不需要这两个管脚的。

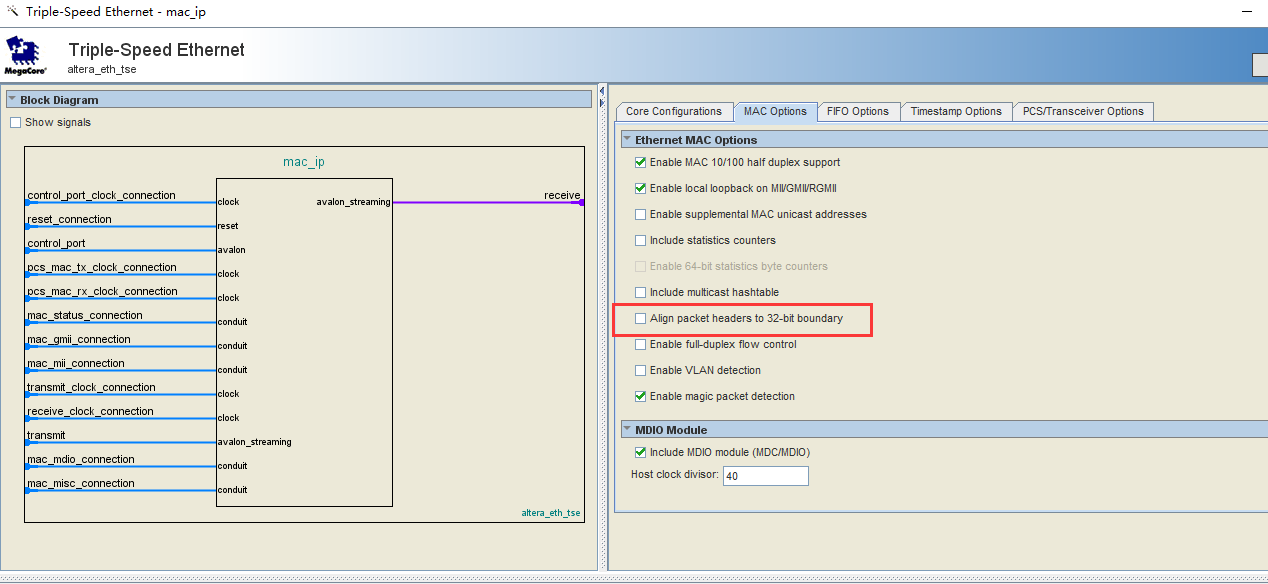

MAC IP核生成注意事项

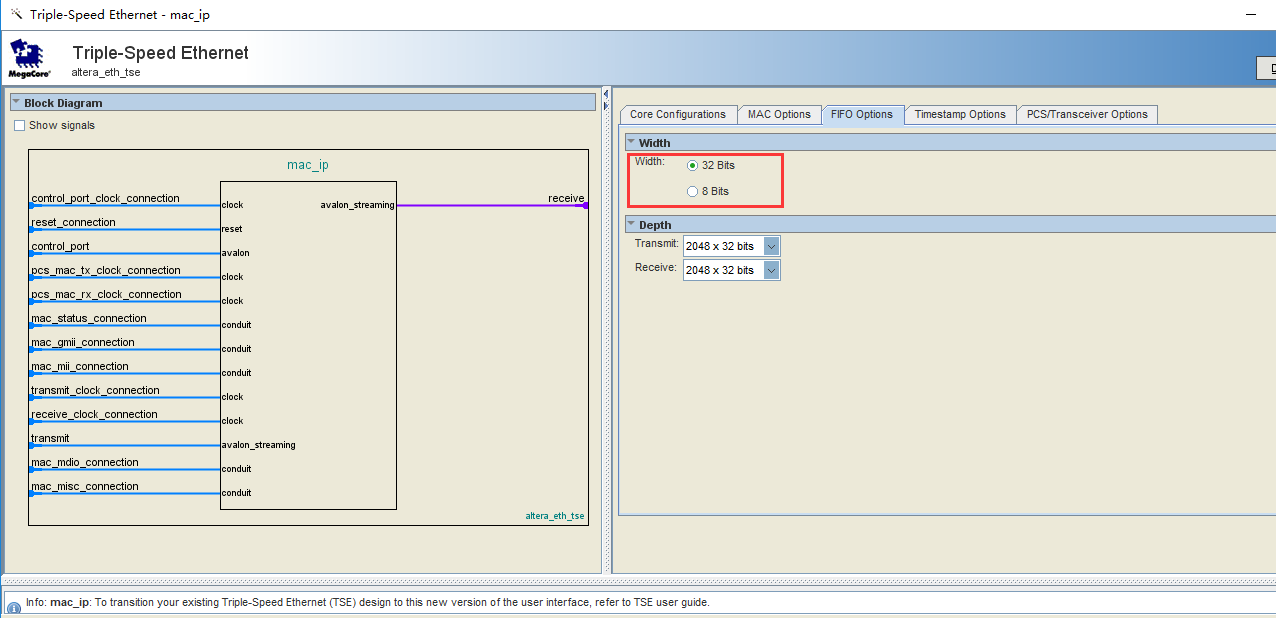

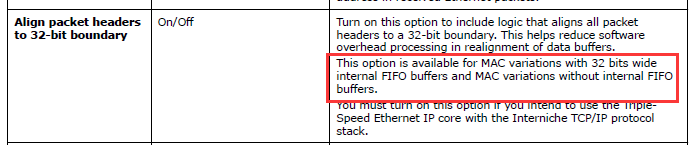

如果选择的是生成32bit数据位宽的内部 FIFO,那么“Align packet headers to 32-bit boundary"就是一个可选择项,具体见数据手册:

特别要注意的是:

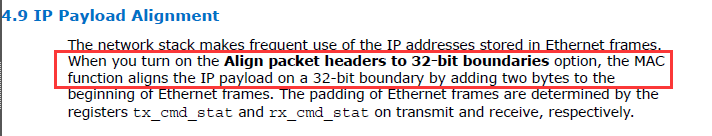

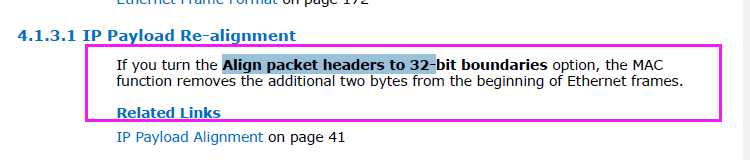

“Align packet headers to 32-bit boundary"这个选项的作用就是为了对齐数据,自动往TX方向/RX方向减少或者增加两个字节。因为按照TX方向发送包文格式:

目的地址(6字节)+源地址(6字节)+类型(2字节)+数据

目的地址(6字节)+源地址(6字节)+类型(2字节)=14(字节),MAC 内部FIFO是32bit,也就是一次发送4byte,14字节不是4的倍数,因此,“Align packet headers to 32-bit boundary"这个选项是为了对齐数据,避免一个时钟周期内地址与数据混合发送,如果不勾选此选项,FPGA与PC端通讯的数据字节数会保持一致。

传输速率要求

1、对于千兆网,只要保证用户侧速率>1G即可;

2、对于百兆网,只要保证用户侧速率>100M即可;

我这里选用32bit的内部FIFO,用PLL分频出10M时钟给MAC IP核的ff_tx_clk 、ff_rx_clk以及clk,这样用户侧速率就是32bit X 10M > 100M,符合速率传输要求。

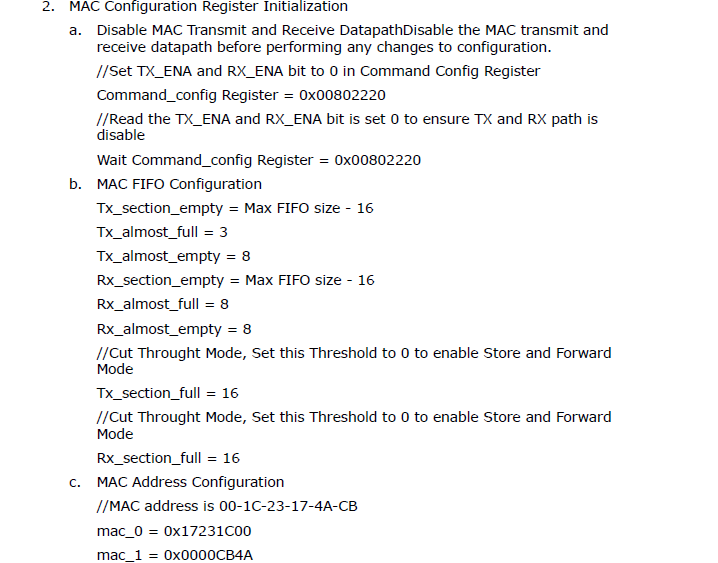

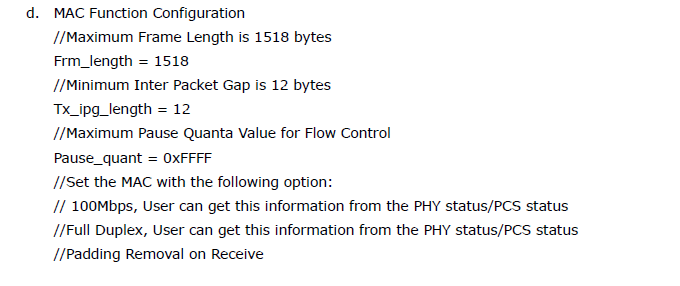

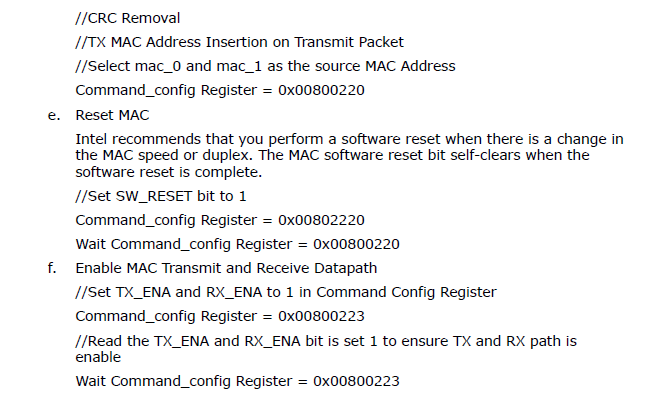

MAC IP核的初始化配置

关于MAC IP核的初始化配置非常重要,如果实在看不懂Command_config Register的配置,请严格按照数据手册P97-P98配置即可

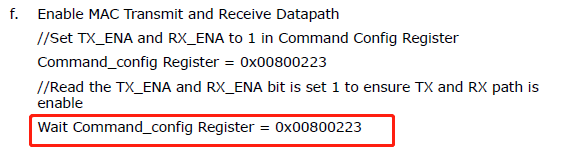

唯一要注意的是最后要保证TX与RX的使能端口已经开启,因此最后要读下16‘h02这个地址,以确保Command_config Register 已经等于0x00800223。

我的初始化配置表如下所示:

parameter REG_NUM = 19 ;

always @(*)begin

case(reg_cnt)

0 :add_wdata = {3'b110,8'h02,32'h00802220};//common

1 :add_wdata = {3'b110,8'h09,32'd2032 };//tx_section_emty

2 :add_wdata = {3'b110,8'h0e,32'd4 };//tx_almost_full

3 :add_wdata = {3'b110,8'h0d,32'd08 };//tx_almost_empty

4 :add_wdata = {3'b110,8'h07,32'd2032 };//rx_section_empty

5 :add_wdata = {3'b110,8'h0c,32'd08 };//rx_almost_full

6 :add_wdata = {3'b110,8'h0b,32'd08 };//rx_almost_emty

7 :add_wdata = {3'b110,8'h0a,32'd16 };//tx_section_full

8 :add_wdata = {3'b110,8'h08,32'd16 };//rx_section_full

9 :add_wdata = {3'b110,8'h03,32'h01020304};//MAC0

10 :add_wdata = {3'b110,8'h04,32'h00000605};//MAC1

11 :add_wdata = {3'b110,8'h05,32'd1518 };//MAX FRAME LENGTH

12 :add_wdata = {3'b110,8'h17,32'd12 };//TX IPG LEGNTH

13 :add_wdata = {3'b110,8'h06,32'h0000ffff};//pause_quant

14 :add_wdata = {3'b110,8'h02,32'h00800220};//..

15 :add_wdata = {3'b110,8'h02,32'h00802220};//common,rst,set SW_RESET bit to 1

16 :add_wdata = {3'b001,8'h00,32'h00010_0000};//wait

17 :add_wdata = {3'b010,8'h02,32'h00800220 };//wait

18 :add_wdata = {3'b110,8'h02,32'h00800223};//common,enable tx and rx //

default:add_wdata = 0;

endcase

end

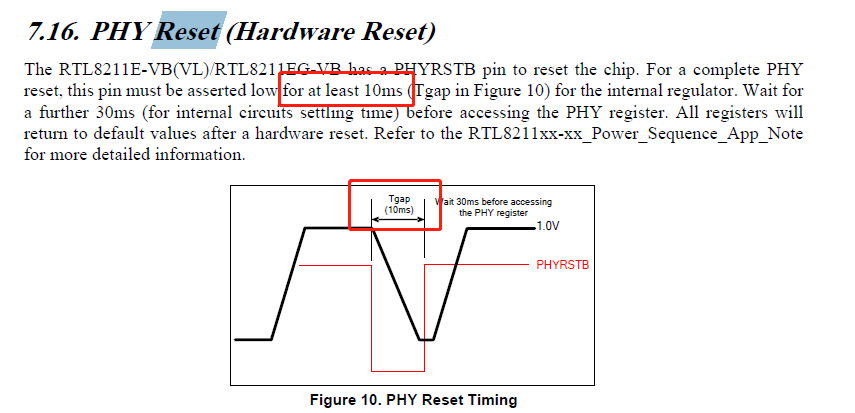

PHY芯片的复位时间

由数据手册可以看到,PHY芯片的上电复位时间至少要维持10ms,以50M输入时钟为例,我的设计如下:

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_phy_reset <= 0;

end

else if(add_cnt_phy_reset)begin

if(end_cnt_phy_reset)

cnt_phy_reset <= 0;

else

cnt_phy_reset <=cnt_phy_reset + 1;

end

end

assign add_cnt_phy_reset = flag==0 ;

assign end_cnt_phy_reset = add_cnt_phy_reset && cnt_phy_reset== 10_00_000 ; //拉低10ms

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

flag <= 0;

end

else if(end_cnt_phy_reset)begin

flag <= 1;

end

end

always @(posedge clk or negedge rst_n)begin //phy_reset

if(rst_n==1'b0)begin

phy_reset <= 1;

end

else if(flag==0&&add_cnt_phy_reset && cnt_phy_reset == 500_000)begin

phy_reset <= 0;

end

else if(end_cnt_phy_reset)begin

phy_reset <= 1;

end

end

测试验证

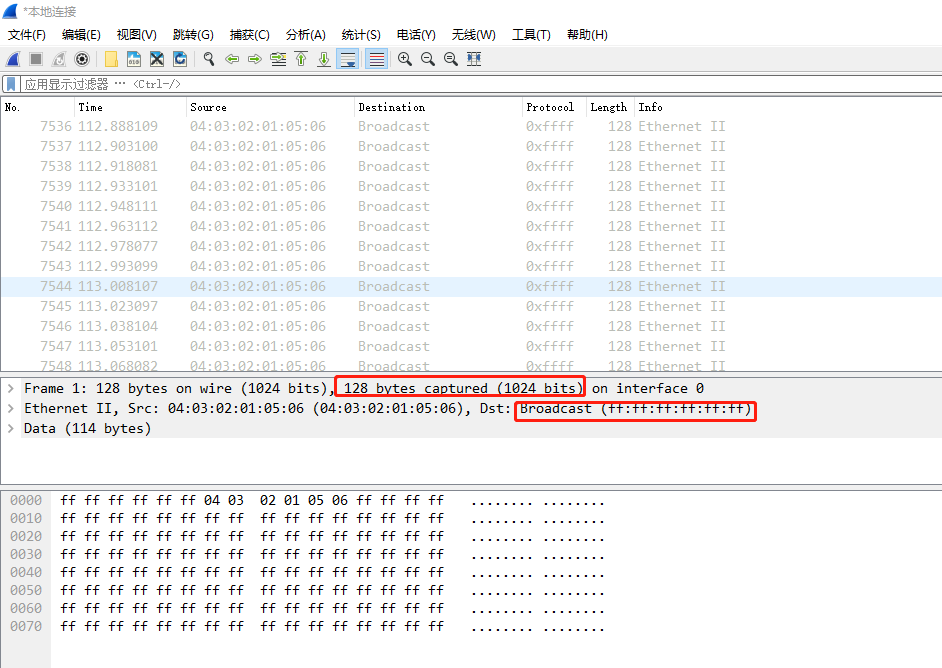

TX 方向: 初始化完成后,自动产生MAC 层包文,经过MAC IP 进行数据链路层处理后,将包文发 给PHY 芯片RTL8211,PHY 芯片经过PHY 层处理后再传给PC,PC 使用wireshark 软件采集包文观察。

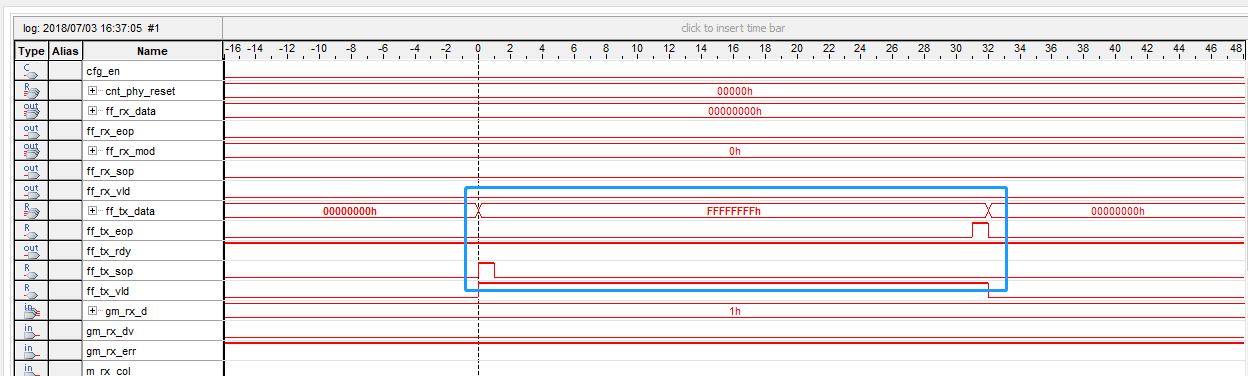

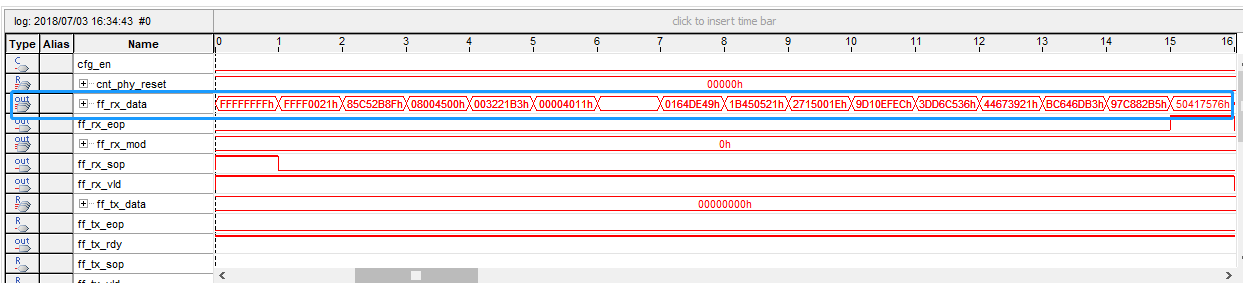

RX 方向: PC 发广播包文给PHY 芯片,PHY 芯片经过PHY 层处理后送给FPGA,FPGA 接到后经过数据链路层处理后,用SIGNALTAP 观测最后的信号。

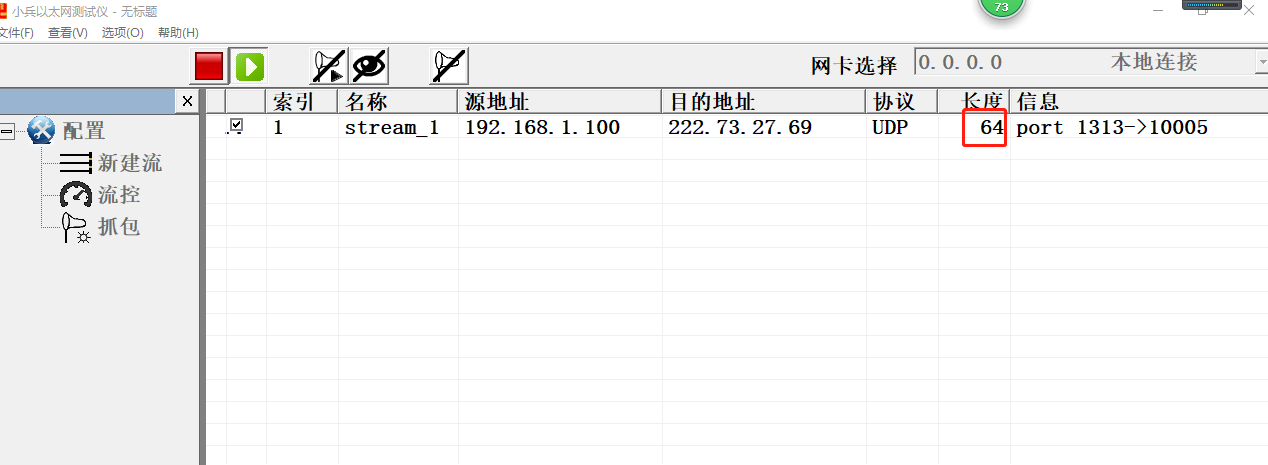

用到的辅助测试软件:

1、小兵发包:往FPGA 发数据

2、wireshark:捕获发送与接收包文

TX方向,FPGA往PC发128字节长度的广播包

PC端收到完好的128个字节的广播包

(2)RX方向

小兵发64字节的广播包

FPGA收到完好的64个字节的广播包

至此,有关该MAC IP核百兆网的设计与使用完毕,有关MAC IP核千兆网的使用与它类似,只需要注意PHY芯片的gtx_clk时钟由PLL倍频得到125M作为输入以及接收/发送数据端口均为8bit即可。

注意:未经允许,禁止转载,违法必究!