-

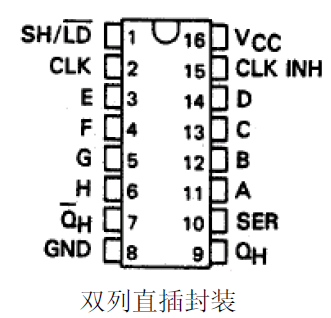

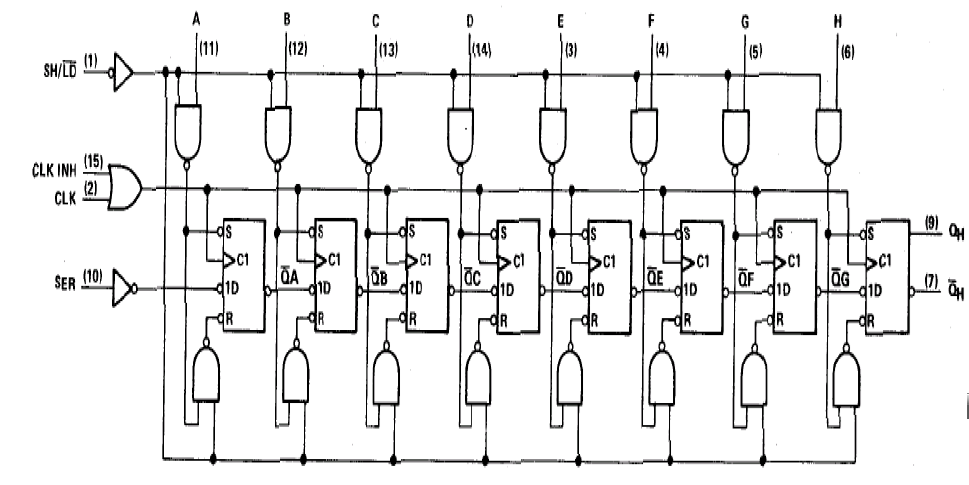

管脚定义与内部逻辑图

注1:其中控制管脚有3个:SH/LD-QH-CLK,CLK INH硬件接VSS,SER和QH'悬空

原理:先拉低SH/LD,A-H置入芯片内部寄存器中,然后拉高SH/LD,锁住A-H输入,然后拉低CLK,读取QH的值,读完后再拉高CLK,读取下一个输入端(A-H),最先读取出来的是H,故将依次读取出来的bit左移组成一个字节。

注2:165级联,父165QH--子165 SER,然后左移位16次,移出来的位先子后父,其中INPUT_BYTEH为父

RLCF INPUT_BYTEH

RLCF INPUT_BYTE

- 实例代码

;-------------------------------------------------------------------------------------------------- ;****************************************************************************** ;74HC165并转串读取 SHIFT_165 BSF P_165PL CALL T4US_DELAY BCF P_165PL CALL T4US_DELAY BSF P_165PL CALL T4US_DELAY MOVLW D'8' MOVWF TMP0_LSB LOOP_165 BCF P_165SCL CALL T4US_DELAY BTFSS P_165SDA BRA LOW_165SDA BSF STATUS,C BRA RIGHT_SHIFT_165BYTE LOW_165SDA BCF STATUS,C RIGHT_SHIFT_165BYTE RLCF HC165BYTE BSF P_165SCL CALL T4US_DELAY DECFSZ TMP0_LSB BRA LOOP_165 ;========================================================== END_SHIFT_165 RETURN