半导体设计的起点正在改变。过去的做法相当直接:根据功耗或性能选择处理器,然后确定需要多少片上和片外内存。现在,情况已经复杂了许多。

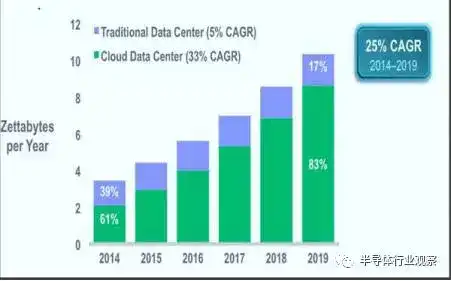

发生这种情况的部分原因是市场开始强调使用特定于应用的硬件和软件解决方案,这些方案之前非常不成熟甚至从未存在过,以至于开发定制解决方案没有利润可言。比如,汽车中的驾驶辅助技术在一两年之前才变成汽车行业的优先发展方向——那时候特斯拉凭借一款可以自动驾驶的汽车震惊了汽车行业。而且过去几年中云计算也实现了显著的增长(见图 1),改变了整个数据流程,让传统的数据中心相形见绌。

图1:基于云储和处理的增长预期。来自 SEMI/Cisco VNI Global IP Traffic Forecast

图1:基于云储和处理的增长预期。来自 SEMI/Cisco VNI Global IP Traffic Forecast

机器学习和人工智能也在迅猛发展,这是一类使用垂直市场算法的水平市场解决方案。IoT/IIot 也在稳步增长,另外还有虚拟现实和增强现实。这些因素加在一起,特定于市场的解决方案就成了行业关注的重心。在许多这些细分市场中,选择某款处理器或内存并不如满足某个市场甚至某个市场的一部分的独特需求更重要。

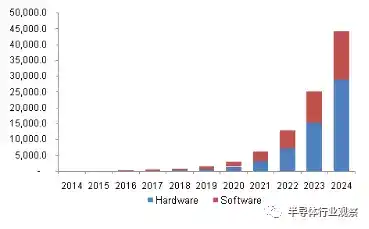

图 2:增强现实市场增长,来自:Grand View Research

图 2:增强现实市场增长,来自:Grand View Research

西门子旗下 Mentor 的总裁兼 CEO Wally Rhines 说:“我们可以看到,针对细分市场的设计多了很多。在标准产品和定制产品中针对细分市场进行开发会改变市场格局,因为它们更能适应特定的行业。。这么做的好处是能在特定细分市场中占据更高的市场份额,也能给半导体公司带来更高的利润。产品基础越多样化,你就越不可能实现35% 到 40% 的营业利润。

其中一些细分市场(尤其是涉及安全的细分市场)有自己的认证要求。其它细分市场则是全新的而且还在发展过程中,所以使用占主导地位的现成部件构建的设计可能不会取得成功。第一批智能手表就证明了这一点,它们曾在几年前如洪水般涌入了消费电子市场。但是,因为这些设备采用的是通用的现成部件,所以这些手表的电池寿命非常有限,导致很多消费者觉得它们用起来太麻烦了,根本算不上是有用的工具。

“不同的市场有不同的起点。”ARM 市场开发高级总监 Bill Neifert 说,“随着汽车电子越来越重要,开发这种技术的公司也在加大力度发展它们的方法,以赶上其它市场。这些公司的需求不同于汽车行业外的公司,其中对定制加速器有很大的需求——要在满足它们的确切需求的同时仍然能使用标准的程序设计。在最前沿总是会有创新,但大多数公司并不在最前沿。大多数公司的目标是利润,所以它们需要更快的速度或更低的功耗。IoT 对此有很大的推动作用。但如果你试图使用通用处理器,那会让你的成本超出可接受的范围。”

另一种方法是开发更定制化的解决方案,但那也有自己的局限性。很多新市场的经济模式并不支持定制化设计。尤其是有的市场中,消费者选择购买的首要考虑因素是设备的价格;还有的市场需要快速推出产品,这需要更多的工程资源和不同的设计方法。

Cadence 的 IP Group 的产品营销组总监 Marc Greenberg 说:“设计师聚集到了两方面。一方面,可用晶体管数量在增长,使用先进工艺完成新设计步骤的需求也在增长。另一方面,市场窗口还是一样。最终结果是人们试图在设计周期中越来越早地实现基于标准的内存和接口 IP。不久之前,没有多少芯片开发经验的新公司还通常不会尝试在先进节点上开发芯片或使用最新的片外接口标准。今天,年轻公司同时尝试先进节点设计和新标准的情况已经很普遍了。”

工艺节点问题

这应该是商业 IP 大展身手的地方。这会逐渐发展,而且并不简单。

“IP 的选择正变得越来越复杂,因为对于很多设计或重新设计而言,IP 还没有得到检验或还没在设计中使用过。”ClioSoft 营销副总裁 Ranjit Adhikary 说,“对于很多这样的公司而言,真正的关键因素是上市时间。这关乎它们将使用哪个节点。但如果内部自己开发 IP 而不是选择第三方 IP,那么他们的 IP 选择可能会受限。使用商业 IP 会增加成本。有些公司可能会先使用商业 IP 攻占市场,然后再通过自己开发 IP 来降低成本。”

这个决策还可以更加复杂。比如,两种 10nm 工艺的代工厂工艺可能就会有很大的不同,使得同一个 IP 模块的表征看起来就相当不一样。而且在某个节点效果最好的方法可能并不是另一个节点的最佳选择。

“在功率和性能的权衡上,你可以有很多选择,但必须符合你使用的每个工艺节点。”Synopsys 产品营销总监 Mary Ann White 说,“所以你总是要有基础 IP,其中包含内存。而且这是由标准单元组成的,可能有很高的密度或很高的性能,但没有低功耗。在那之后,难度就更大了。”

而且可能还根本没有可用的 IP,这种情况正越来越多。代工厂正在争先恐后为新市场提供新工艺,不管是新节点还是已有节点都是如此,从而迫使 IP 供应商选择该向哪里投入资源。对于希望使用最新节点的新设计而取得领先的公司而言,这是一个大难题。

“当你研究一个设计时,你必须确定它的 IP 是不是可用的。”eSilicon 的 IP 营销总监 Lisa Minwell 说,“有什么限制因素?这可能取决于你的目标市场。所以如果这是一种网络设计,又有什么限制因素呢?我们一直在奋力工作,好让我们能控制这一点。你必须要有实实在在可用的 IP。”

整个行业都赞同这一观点。Flex Logix 的 CEO Geoff Tate 说:“如果一个节点变化足够大,几个工程师可能需要六个月才能做出一个可输出的产品。但对于大多数 IP 而言,输出时间要重要得多。我们使用了数字设计规则,所以输出时间要短一点。但我们确实看到客户在其它 IP 上出现问题。举个例子,假设你正在开发一种锁相环(phase-lock loop),成本非常高,你需要一或两个客户才能收回成本。做这件事的唯一方法是坚持使用 16/14nm 和 7nm 这样的主节点,(而尽量跳过) 10nm、12nm 和 22nm 这些中间节点。”

还要将其与先进封装选择结合起来考虑,因为并非所有 IP 都适合 fan-out 或 2.5D 设计,所以选择合适的可用 IP 是很困难的。

基础设施

IP 不是唯一的起点。在一些市场中,芯片制造商已经开始根据电子管道进行设计,并据此开发架构了。

“除非他们明确想做一款通用处理器,否则大多数事情都是从引脚开始的。”ArterisIP CTO Ty Garibay 说,“所以他们可能需要‘这么多’带宽或第 4 代 PCIe 或 DDR3、4 或 5。然后你在上面还需要多少不同的信道以及你从哪里得到这些 PHY?这还可以往内部继续深入。你有‘这么多’数据。你在哪里处理这些数据?你是否需要 GPU 或专用加速器?单一一个市场可能会有某种特定类型的数据。然后你可能会有空闲的处理能力,或者你会用掉一些额外的 CPU 周期来处理你不知道的事情。”

其它公司也观察到了这种情况。 NetSpeed Systems 营销和业务发展副总裁 Anush Mohandass 说他在六个月前第一次看到这种转变的征兆,那时候一家大型客户是从互连方面开始设计的,之后才开始考虑工艺。

Mohandass 说:“你后退一步思考一下,这是有道理的。你需要知道带宽和延迟需求,这样你就可以规划不同元素之间的路径。但当时我还是很惊讶,因为我们之前没见过这种。第一次出现这种事时,我们还以为这是一个例外。但自那以后,这差不多已经变成了一种模式,尤其是在汽车和超大容量存储领域。实际上,我们正见证着设计方式从以 CPU 为中心转向以内存为中心。为此你要给出蓝图,阐述你移动数据的方式以及系统响应所需的时间。找到这些答案是很关键的,因为它决定了传感器发送数据所需的时间。”

安全性至关重要的市场

汽车、航空、工业和医疗行业还有额外的问题。这些行业不仅需要可用的 IP,还需要这些 IP 得到市场相关标准的检验。

在航空电子方面,大公司的解决方案是开发它们自己的 IP,而不是等待商业上现成的(COTS) IP 在特定的节点或工艺上得到验证。Aldec 营销总监 Louie de Luna 说“有一些不同的方法。一是逆向工程 IP、进行更多测试并提供更多文档,以便其满足标准。大型航空电子公司就正在这样做。它们不会购买商业 IP。它们做自己的 IP。但我们现在也看到有一个趋势:IP 供应商开始提供满足 DO-254 标准的 IP。”

商用航空电子 IP 分成三大类:软核(soft IP),即可综合的(synthesizable)的 HDL 源代码;固核(firm IP),基本上就是需要安置和路由的网表;硬核(hard IP),比如带有嵌入式 ARM 核的 FPGA。所有这些都需要大量文档。但航空电子的产品周期平均为 2 到 5 年,开发 IP 的附加成本并不显著。汽车电子则完全不一样。

“我们看到新细分市场中这种转变越来越多,比如汽车、超大容量存储和 5G。”NetSpeed 的 Mohandass 说,“这些都是没有太多传统的新兴细分市场,而且人们认为谁先进入这些市场,谁就将赢得这些市场。”

未知因素

对芯片制造商而言,紧跟所有这些市场绝非易事。一些细分市场很新,汽车行业等已有市场又在快速变化,所以颠覆时有发生。协议和标准几乎在一直不断地演进,这意味着今天开始的芯片设计可能在到达市场的时候就已经过期了。

这一直都是前沿设计的坏处之一,但问题还在扩散。其中之一是很多新市场并不需要先进节点的技术。此外,很多这些设备都在更大的系统互相连接在一起,所以协议和标准的变化并不限于 finFET 层面的工艺。它们甚至会影响使用更旧节点创造的模拟器件。

有一些解决这个问题的方法。一是为芯片增加余量,以应对任何变化。二是为设计加入可定制的编程性,嵌入式 FPGA 市场已经采取了这种方法。

“如果你专注于 5G,那么其数字前端可能会随时间发生很大变化。”Achronix 营销副总裁 Steve Mensor 说,“你知道有什么功能,但你不知道这些过滤器,因为它们仍还在开发中。唯一能有效应对这种情况的方法是使用 FPGA。在机器学习领域也是一样。你知道其中会有大量矩阵乘法运算,但你不知道神经元权重的规格。在此之上,算法也在变化,而且你不知道算法会变成什么样。但如果你有一个卷积神经网络并且要做一个 17×17 的乘法器,那可能就有点过头了。也许你只需要一个 8×8 的。这能让你显著减小尺寸和降低功率。”

另一个问题是如何找到最佳的方法。因为解决一个问题的可能方法非常多,也有解决老问题的新方法出现。ArterisIP 的 Garibay 说:“在自动驾驶和人工智能等市场,我们看到出现了很多新玩家,已有玩家也在提供新方法。新的次级市场正在发展。IP 组合也在快速变化,而且现在也在向通用市场提供。问题是它们如何能与工具链相适应。”

这是非常明显的,即使对于过去一直被认为是标准部件的微控制器也是一样。之前的带有片上内存的 8 位执行器(actuator)已经让位给连接到外部内存的 16 位和 32 位器件。这种外部内存即是之前的 MCU 和 CPU 之间微分器(differentiator)。

Neifert 说:“如果你和 FPGA 公司谈谈他们使用可编程 SoC 的方式,那就可能是嵌入式 CPU 或者可能用在定制 MCU 中。这能提供很强的处理能力和额外的编程选择。开发 MCU 器件的人越来越将其看作是带有自己的生态系统的 CPU。这种发展的一大推动力是希望能让终端客户在上面安装更多软件。在此之上,还有安全性问题。你希望客户能不受安全威胁地运行他们自己的软件。那也需要新工具,因为不使用新工具而增加这些功能是毫无价值的。你需要软件建模功能、编译器和调试器。”

总结

现在整个半导体生态系统都在发生改变,这些改变表明芯片制造商进入市场的方式和对他们而言重要的因素都在发生根本性转变。其中有以下几大力量:

- 行业渐渐认识到,赢得一个市场的最好方法并不一定要使用最快或最有功率效率的通用处理器。这促使行业转向更加异构的处理、先进封装以及关注采用什么方式在什么地方处理不断增多的数据。

- IP 供应商在选择工艺节点上越来越谨慎,它们希望确保有足够多的利润,从而收回他们投入的资源,因为现在每一种产品都很不一样,不能简单地就从一种代工厂工艺转换成另一种。

- 在终端市场也有很多不确定性,架构师正在重新思考如果设计需要为协议或标准变化或市场需求而进行调整,怎样才能给设计带来的影响最小。

总而言之,这些都代表了公司的设计方法的重大转变,并且它们最终会对工具、IP 选择和设计的架构本身产生重大的影响。