对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容。

1.FPGA内部结构及基本原理

FPGA是可以编程的,必须通过了解FPGA内部结构才能很好地理解为什么FPGA是可以编程的。学习FPGA不能像学习其他CPU芯片一样,看到Verilog或者VHDL就像看到C语言或者其它软件编程语言一样。一条条的读,一条条的分析。要冲破软件编程的思想。

那么FPGA为什么是可以“编程”的呢?首先来了解一下什么叫“程”。启示“程”只不过是一堆具有一定含义的01编码而已。编程,其实就是编写这些01编码。只不过我们现在有了很多开发工具,通常都不是直接编写这些01编码,而是以高级语言的形式来编写,最后由开发工具转换为这种01编码而已。对于软件编程而言,处理器会有一个专门的译码电路逐条把这些01编码翻译为各种控制信号,然后控制其内部的电路完成一个个的运算或者是其它操作。所以软件是一条一条的读,因为软件的操作是一步一步完成的。而FPGA的可编程,本质也是依靠这些01编码实现其功能的改变,但不同的是FPGA之所以可以完成不同的功能,不是依靠像软件那样将01编码翻译出来再去控制一个运算电路,FPGA里面没有这些东西。图1.5是Cyclone IV代芯片内部结构。

图1.5 Cyclone IV内部结构

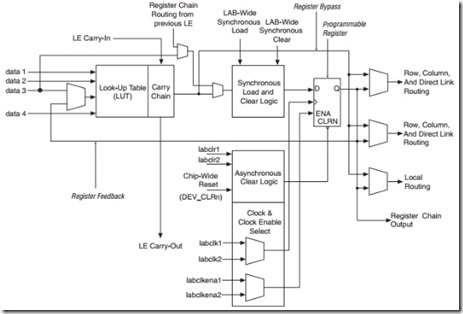

FPGA内部主要三块:可编程的逻辑单元、可编程的连线和可编程的IO模块。可编程的逻辑单元是什么?其基本结构某种存储器(SRAM、FLASH等)制成的4输入或6输入1输出地“真值表”加上一个D触发器构成。任何一个4输入1输出组合逻辑电路,都有一张对应的“真值表”,同样的如果用这么一个存储器制成的4输入1输出地“真值表”,只需要修改其“真值表”内部值就可以等效出任意4输入1输出的组合逻辑。这些“真值表”内部值是什么?就是那些01编码而已。如果要实现时序逻辑电路怎么办?这不又D触发器嘛,任何的时序逻辑都可以转换为组合逻辑+D触发器来完成。但这毕竟只实现了4输入1输出的逻辑电路而已,通常逻辑电路的规模那是相当的大哦。那怎么办呢?这个时候就需要用到可编程连线了。在这些连线上有很多用存储器控制的链接点,通过改写对应存储器的值就可以确定哪些线是连上的而哪些线是断开的。这就可以把很多可编程逻辑单元组合起来形成大型的逻辑电路。最后就是可编程的IO,这其实是FPGA作为芯片级使用必须要注意的。任何芯片都必然有输入引脚和输出引脚。有可编程的IO可以任意的定义某个非专用引脚(FPGA中有专门的非用户可使用的测试、下载用引脚)为输入还是输出,还可以对IO的电平标准进行设置。总归一句话,FPGA之所以可编程是因为可以通过特殊的01代码制作成一张张“真值表”,并将这些“真值表”组合起来以实现大规模的逻辑功能。图1.6是Cyclone IV的FPGA内部LE示意图。不了解FPGA内部结构,就不能明白最终代码如何变到FPGA里面去的。也就无法深入的了解如何能够充分运用FPGA。现在的FPGA,不单单是有前面讲的那三块,还有很多专用的硬件功能单元,如何利用好这些单元实现复杂的逻辑电路设计,是从菜鸟迈向高手的路上必须要克服的障碍。而这一切,还是必须先从了解FPGA内部逻辑及其工作原理做起。

图1.6 Cyclone的LE结构

2.正确理解verilog/VHDL语言以及和硬件结构的关系

HDL语言的英语全称是:Hardware Description Language,注意这个单词Description,而不是Design。为什么要用Description这个词而不是Design呢?因为HDL确实不是用用来设计硬件的,而仅仅是用来描述硬件的。描述这个词精确地反映了HDL语言的本质,HDL语言不过是已知硬件电路的文本表现形式而已,只是将以后的电路用文本的形式描述出来而已。而在编写语言之前,硬件电路应该已经被设计出来了。语言只不过是将这种设计转化为文字表达形式而已。但是很多人就不理解了,既然硬件都已经被设计出来了,直接拿去制作部就完了,为什么还要转化为文字表达形式再通过EDA工具这些麻烦的流程呢?其实这就是很多菜鸟没有了解设计的抽象层次的问题,任何设计包括什么服装、机械、广告设计都有一个抽象层次的问题。就拿广告设计来说吧,最初的设计也许就是一个概念,设计出这个概念也是就是一个点子而已,离最终拍成广告还差得很远。硬件设计也是有不同的抽象层次,每一个层次都需要设计。

最高的抽象层次为算法级、然后依次是体系结构级、寄存器传输级、门级、物理版图级。使用HDL的好处在于我们已经设计好了一个寄存器传输级的电路,那么用HDL描述以后转化为文本的形式,剩下的向更低层次的转换就可以让EDA工具去做了,这就大大的降低了工作量。这就是可综合的概念,也就是说在对这一抽象层次上硬件单元进行描述可以被EDA工具理解并转化为底层的门级电路或其他结构的电路。在FPGA设计中,就是在将这以抽象层级的意见描述成HDL语言,就可以通过FPGA开发软件转化为FPGA内部逻辑功能实现形式。

HDL也可以描述更高的抽象层级如算法级或者是体系结构级,但目前受限于EDA软件的发展,EDA软件还无法理解这么高的抽象层次,所以HDL描述这样抽象层级是无法被转化为较低的抽象层级的,这也就是所谓的不可综合。所以在阅读或编写HDL语言,尤其是可综合的HDL,不应该看到的是语言本身,而是要看到语言背后所对应的硬件电路结构。如果看到的HDL始终是一条条的代码,那么这种人永远摆脱不了菜鸟的宿命。假如哪一天看到的代码不再是一行行的代码而是一块一块的硬件模块,那么恭喜脱离了菜鸟的级别,进入不那么菜的鸟级别。

3.学以致用

FPGA本身不算什么,一切皆在FPGA之外这一点恐怕也是很多学FPGA的菜鸟最难理解的地方。FPGA是给谁用的?很多学校解释为给学微电子专业或者集成电路设计专业的学生用的,其实这不过是很多学校受资金限制,卖不起专业的集成电路设计工具而用FPGA工具替代而已。其实FPGA是给设计电子系统的工程师使用的。这些工程师通常是使用已有的芯片搭配在一起完成一个电子设备,如基站、机顶盒、视频监控设备等。当现有芯片无法满足系统的需求时,就需要用FPGA来快速的定义一个能用的芯片。

前面说了,FPGA里面无法就是一些“真值表”、触发器、各种连线以及一些硬件资源,电子系统工程师使用FPGA进行设计时无非就是考虑如何将这些以后资源组合起来实现一定的逻辑功能而已,而不必像IC设计工程师那样一直要关注到最后芯片是不是能够被制造出来。本质上和利用现有芯片组合成不同的电子系统没有区别,只是需要关注更底层的资源而已。要想把FPGA用起来还是简单的,因为无非就是那些资源,在理解了前面两点再搞个实验板,跑跑实验,做点简单的东西是可以的。而真正要把FPGA用好,那光懂点FPGA知识就远远不够了。因为最终要让FPGA里面的资源如何组合,实现何种功能才能满足系统的需要,那就需要懂得更多更广泛的知识。

对于我们学过的数字电路和模拟电路,如果连最基本的数字逻辑的知识都有问题,学习FPGA的愿望只是空中楼阁而已。如果不能将数字逻辑知识烂熟于心,养成良好的设计习惯,学FPGA到最后仍然是雾里看花水中望月,始终是一场空。