Makfile

1.用途

- 项目代码编译管理

- 节省编译项目时间(在编译的时候之编译修改过的.c文件,并和之前编译好的.o链接使用)

- 一次编写终身受益

#目标:依赖(条件) #命令 #阶段一 #app:add.c sub.c dive.c mul.c main.c #gcc add .c sub.c dive.c mu.c main.c -o app # #阶段二 #app:add.o sub.o dive.o mul.o #gcc add.o sub.o dive.o mul.o main.o -o app #add.o:add.c # gcc -c add.c #sub.o:sub.c # gcc -c sub.c #dive.o:dive.c # gcc -c dive.c #mul.o:mul.c # gcc -c mul.c #main.o:main.c # gcc -c main.c #阶段三(比较通用,和源代码已经没什么关系了) #$@表示目标,$^表示所有依赖,$<表示依赖中的第一个 #obj=add.o sub.o mul.o dive.o main.o #src=$(wildcard *.c)//找到当前目录下所有以点c结尾的文件名 #obj=$(pathsubst %.c,%.o,$(src))//将src中的所有.替换成同名的.o,仅仅是文件名替换。 #target=app//目标文件变量 #$(target):$(obj) gcc $^ -o $@ #%.o:%.c # gcc -c $< -o $@ #阶段四 CPPFLAGS=-Iinclude//预处理器标志,指定头文件在哪 CFLAGS=-g -Wall//编译时候的参数 LDFLAGS=-L../lib -lmycalc//指定共享库 CC=gcc //指定编译器 src=$(wildcard *.c) obj=$(pathsubst %.c,%.o,$(src)) target=app $(target):$(obj) gcc $^ $(LDFLAGS) -o $@ %.o:%.c gcc -c $< $(CFLAGS)$(CPPFLAGS)-o $@ .PHONY:clean clean: -rm -f *.o -rm -f app

#彻底清除生成过程文件和生成配置文件

distclean:

rm /usr/bin/app

install:

cp app /usr/bin

test: @echo src;

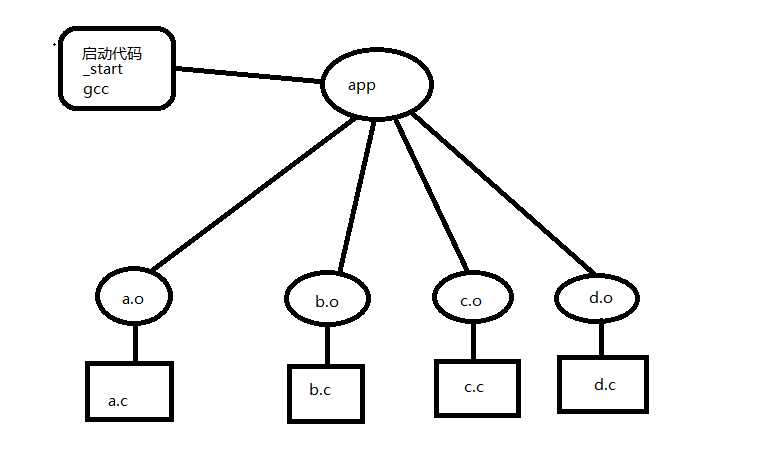

阶段一:先至上而下建立关系树

阶段二:自下而上执行命令

阶段三阶段四都是让变得通用。

只要知道makefile怎么工作就好。

2.基本规则

三要素:

- 目标

- 条件

- 命令

3.Makefile工作原理

- 分析各个目标和依赖之间的关系

- 根据依赖关系自底向上执行命令

- 根据修改时间比目标新,确定更新(之前介绍的那三个时间中的最后修改时间)

- 如果目标不依赖任何条件,则执行对应命令,以示更新

4.clean

- 用途:清除编译生成的中间.o文件和最终目标文件。

- make clean 如果当前目录下有同名clean文件,则不执行clean对应的命令

- 伪目标声明:.PHONY:clean

- clean 命令中的特殊符号

-"-” 此条命令出差,make也会继续执行后续的命令。如:“-rm main.o”

-"@‘’不显示命令本身,只显示结果。如:“@echo” clean done “”

- 其他

-make默认执行第一个出现的目标,可通过make dest 指定要执行的目标

-distclean目标

-install目标

-make -C 指定目录 进入指定目录,调用里面的Makefile