复位信号设计的原则是尽量不包含不需要的复位信号,如果需要,考虑使用局部复位和同步复位。

复位信号根据是否同步,高电平还是低电平使能,复位后的信号为高电平还是低电平可以有多种组合:

异步低电平复位

异步低电平置位

异步高电平复位

。。。

每种情况会被综合出不同的硬件电路,而在Xilinx内部则有4种寄存器可用于实现

FDCE

FDPE

FDRE

FDSE

FD即寄存器,E则是带时钟使能,而

C - clear 异步清零

P - preset 异步置位

R - reset 同步复位

S - set 同步置位

以上4中寄存器都是高电平使能,所以在使用Xilinx时要做高电平复位

Xilinx推荐少使用复位并在必要时使用同步复位,考虑通常使用复位信号来给寄存器赋初值的情况,GSR可以解决这个问题,GSR会在上电初始化时初始化内部所有有记忆功能的单元,除FDPE和FDSE会将寄存器初始化为高电平外,Xilinx FPGA会将内部其他单元初始化为0

基于以上的了解,FDRE应该是最佳的复位方案,但在验证我的想法时,我发现预期之外的结果,比如一下的同步高电平复位代码

module test( input clk , input clr , input din , output reg sync_high_set ); reg rst ; always @(posedge clk) rst <= clr; // synchronous reset always @(posedge clk) begin if(rst) sync_high_set <= 0; else sync_high_set <= din; end endmodule

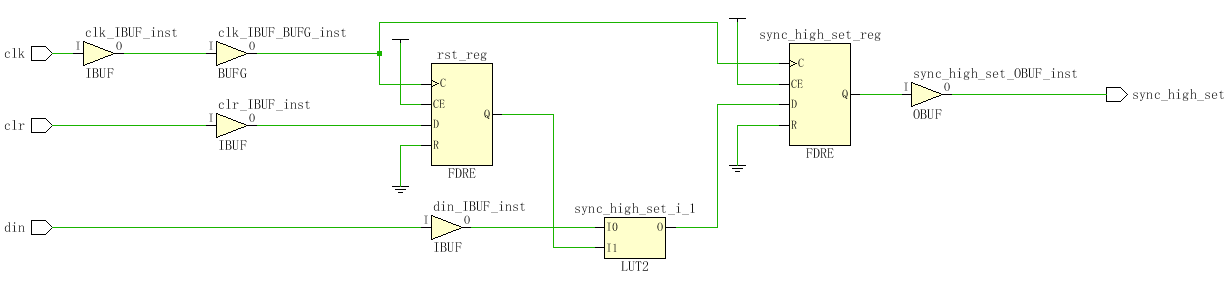

综合出来确实如下的电路

虽然逻辑结果时一样,但这正好与我们的初衷相反,即我们本来是像优化电路,它却使用了更多的不必要的逻辑资源,有两种方法可以达到我们要的效果,

将综合设置里的参数 -control_set_opt_threshold 设置为0

在代码中添加 (* direct_reset = "yes" *)

详细的相关内容可以参见UG949 Vivado Design Methodology中Contol Signals and Control Sets小节

寄存器详细内容可参考UG768 Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs,而更多primitive信息参见UG901 Vivado Design Suite User Guide