Pin Control Subsystem是Linux内核抽象出的一套用于控制硬件引脚的一套子系统。

1、源文件列表

源码位于linux/drivers/pinctrl目录下,源文件列表如下:

| 文件名 | 描述 |

| core.c core.h | pin control subsystem的core driver |

| pinctrl-utils.c pinctrl-utils.h | pin control subsystem的一些utility接口函数 |

| pinmux.c pinmux.h | pin control subsystem的core driver(pin muxing部分的代码,也称为pinmux driver) |

| pinconf.c pinconf.h | pin control subsystem的core driver(pin config部分的代码,也称为pin config driver) |

| devicetree.c devicetree.h | pin control subsystem的device tree代码 |

| pinctrl-xxxx.c | 各种pin controller的low level driver。 |

在pin controller driver文档中 ,我们以2416的pin controller为例,描述了一个具体的low level的driver,这个driver涉及的文件包括pinctrl-samsung.c,pinctrl-samsung.h和pinctrl-s3c24xx.c,具体位于ux/drivers/pinctrl/samsung目录。

2、和其他内核模块接口头文件

很多内核的其他模块需要用到pin control subsystem的服务,这些头文件就定义了pin control subsystem的外部接口以及相关的数据结构。我们整理linux/include/linux/pinctrl目录下pin control subsystem的外部接口头文件列表如下(在4.1内核中已经找不到以下文件):

| 文件名 | 描述 |

| consumer.h | 其他的driver要使用pin control subsystem的下列接口: a、设置引脚复用功能 b、配置引脚的电气特性 这时候需要include这个头文件 |

| devinfo.h | 这是for linux内核的驱动模型模块(driver model)使用的接口。struct device中包括了一个struct dev_pin_info *pins的成员,这个成员描述了该设备的引脚的初始状态信息,在probe之前,driver model中的core driver在调用driver的probe函数之前会先设定pin state |

| machine.h | 和machine模块的接口。 |

3、Low level pin controller driver接口

我们整理linux/include/linux/pinctrl目录下pin control subsystem提供给底层specific pin controller driver的头文件列表如下:

| 文件名 | 描述 |

| pinconf-generic.h | 这个接口主要是提供给各种pin controller driver使用的,不是外部接口。 |

| pinconf.h | pin configuration 接口 |

| pinctrl-state.h | pin control state状态定义 |

| pinmux.h | pin mux function接口 |

pin control subsystem的主要功能包括:

(A)管理系统中所有可以控制的pin。在系统初始化的时候,枚举所有可以控制的pin,并标识这些pin。

(B)管理这些pin的复用(Multiplexing)。对于SOC而言,其引脚除了配置成普通GPIO之外,若干个引脚还可以组成一个pin group,形成特定的功能。例如pin number是{ 0, 8, 16, 24 }这四个引脚组合形成一个pin group,提供SPI的功能。pin control subsystem要管理所有的pin group。

(C)配置这些pin的特性。例如配置该引脚上的pull-up/down电阻,配置drive strength等。

Pin Control Subsystem和GPIO subsystem交互

为何pin control subsystem要和GPIO subsystem交互?

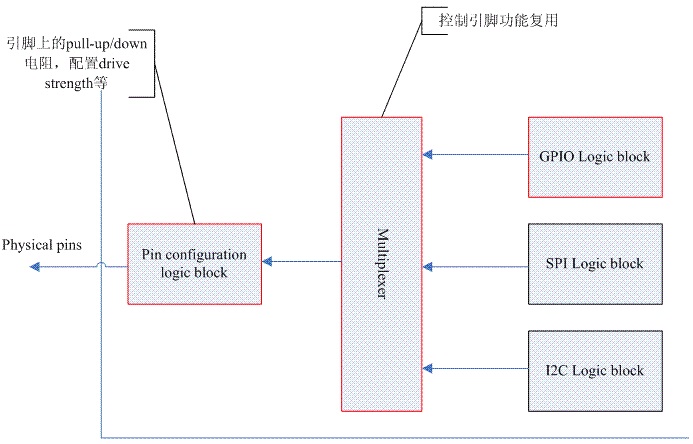

作为软件工程师,我们期望的硬件设计应该如下图所示:

GPIO的HW block应该和其他功能复用的block是对等关系的,它们共同输入到一个复用器block,这个block的寄存器控制哪一个功能电路目前是active的。pin configuration是全局的,不论哪种功能是active的,都可以针对pin进行电气特性的设定。这样的架构下,上图中红色边框的三个block是完全独立的HW block,其控制寄存器在SOC datasheet中应该是分成三个章节描述,同时,这些block的寄存器应该分别处于不同的地址区间。

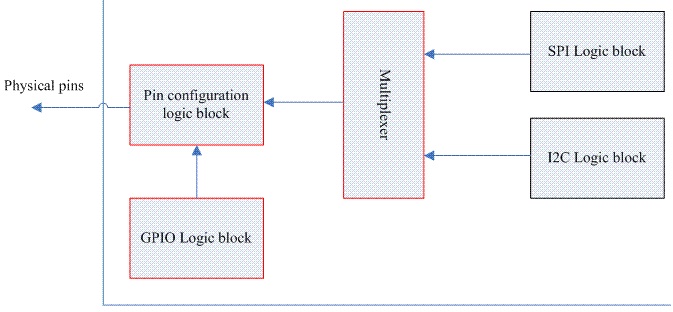

对于软件工程师,我们可以让pin control subsystem和GPIO subsystem完全独立,各自进行初始化,各自映射自己的寄存器地址空间,对于pin control subsystem而言,GPIO和其他的HW block没有什么不同,都是使用自己提供服务的一个软件模块而已。然而实际上SOC的设计并非总是向软件工程师期望的那样,有的SOC的设计框架图如下:

这时候,GPIO block是alway active的,而红色边框的三个block是紧密的捆绑在一起,它们的寄存器占据了一个memory range(datasheet中用一个章节描述这三个block)。这时候,对于软件工程师来说就有些纠结了,本来不属于我的GPIO控制也被迫要参与进来。这时候,硬件寄存器的控制都是pin controller来处理,GPIO相关的操作都要经过pin controller driver,这时候,pin controller driver要作为GPIO driver的back-end出现。

Reprinted From:http://www.wowotech.net/gpio_subsystem/pin-control-subsystem.html