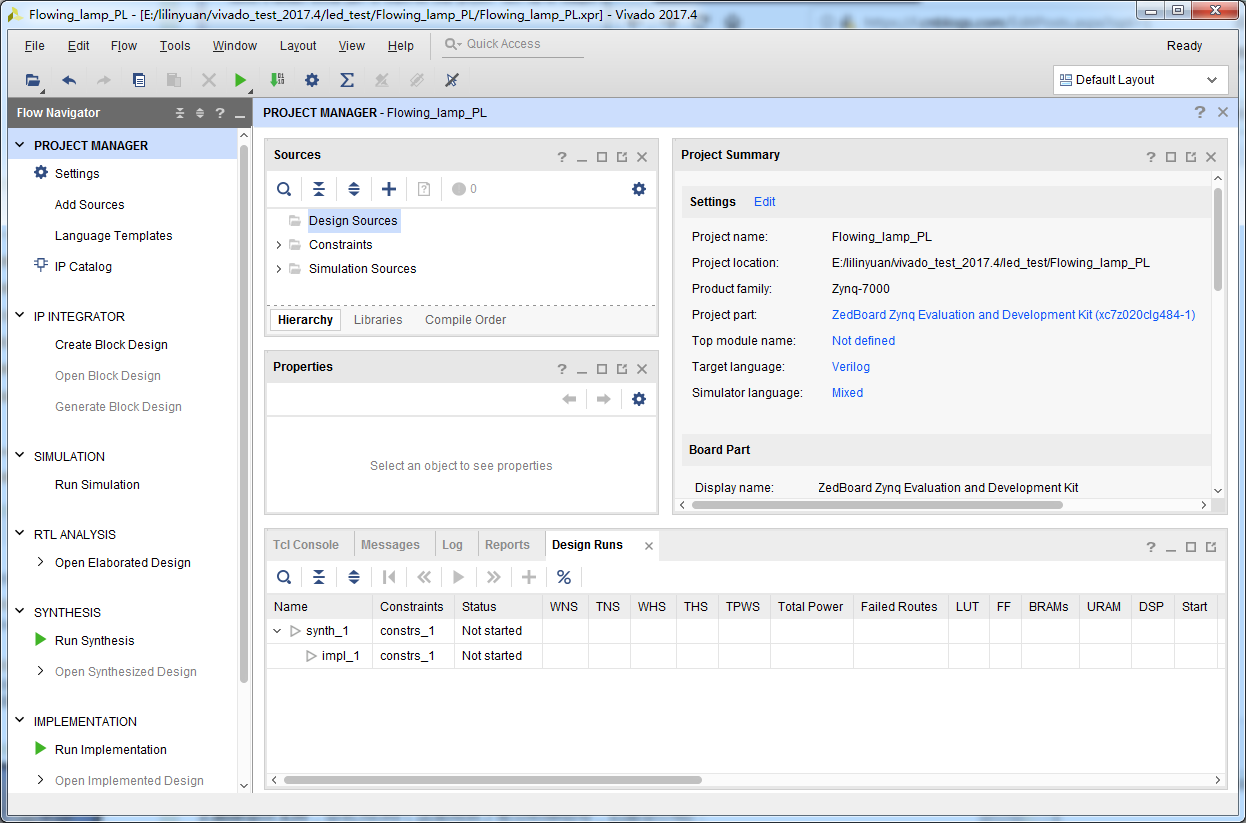

环境:vivado 217.4

开发板: zedboard ver.d xc7z020clg484-1

1.打开Vivado新建一个RTL工程。

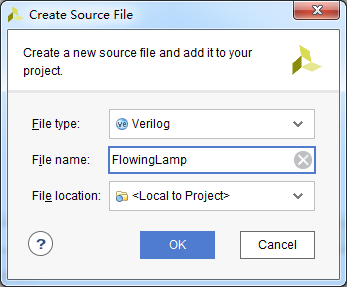

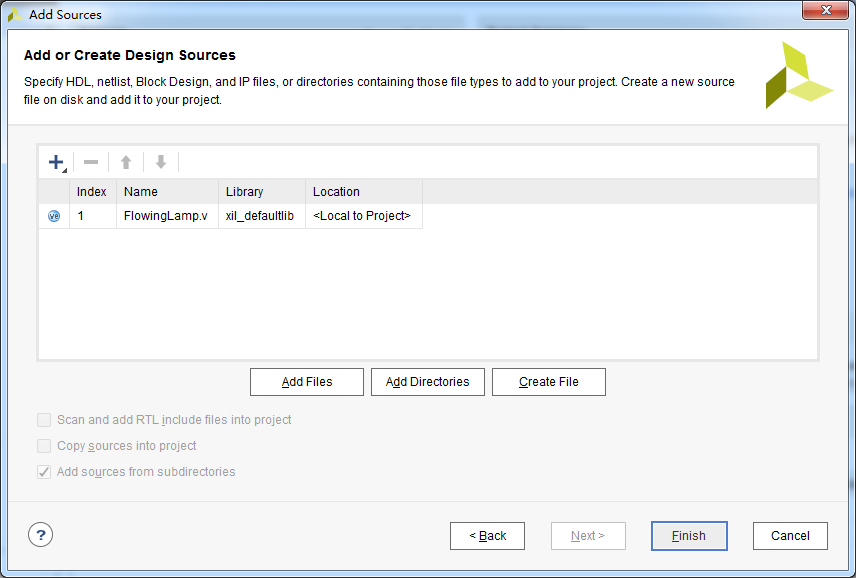

2.add source->add/create design resouce->create ->finish

3.写入内容。

1 module FlowingLamp( 2 input wire GCLK, //PL 100mhz 3 input wire BTNU, //low 4 output wire [7:0] LED 5 ); 6 wire clk_100m; //clk 100mhz 7 wire rst; //reset 8 reg clk_2hz; //0.5s 9 reg [7:0] led_reg; 10 reg [31:0] delay_cnt; 11 12 assign LED = led_reg; 13 assign clk_100m = GCLK; 14 assign rst = BTNU; 15 16 //clk_2hz 17 always@(posedge clk_100m or negedge rst) 18 begin 19 if(rst)begin 20 clk_2hz <= 1'b0; 21 delay_cnt <= 32'h0; 22 end 23 else begin 24 if(delay_cnt == 32'd25_000_000 - 32'd1)begin 25 delay_cnt <= 32'h0; 26 clk_2hz <= ~clk_2hz; 27 end 28 else begin 29 delay_cnt <= delay_cnt + 1'b1; 30 end 31 end 32 end 33 34 //led_reg 35 always @(posedge clk_2hz or posedge rst) 36 begin 37 if(rst) 38 led_reg <= 8'h01; 39 else 40 led_reg <= {led_reg[6:0],led_reg[7]}; 41 end 42 43 endmodule

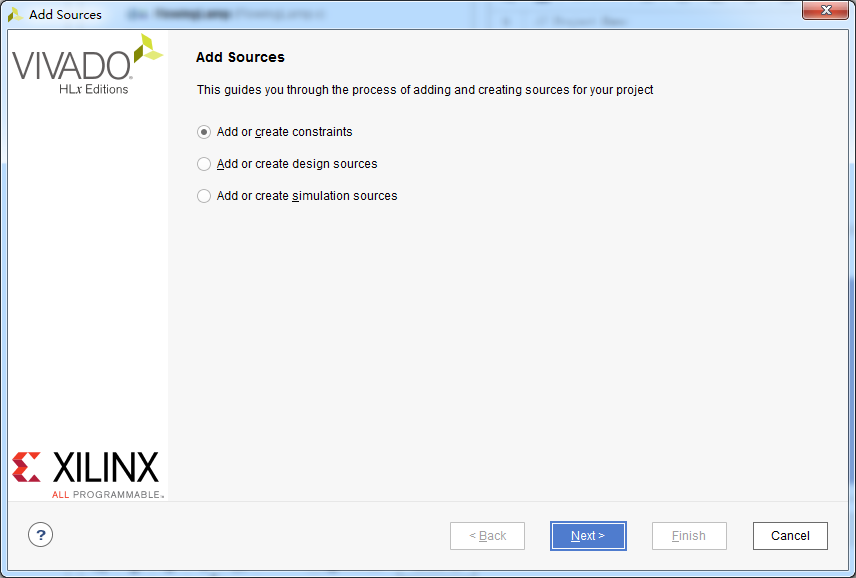

4.添加约束文件,分配引脚。在Constraints下constrs_1 右键 Add Resouce。与添加.v文件相似。

可以直接编写;

5.编写约束文件,可以直接输入,也可生成。

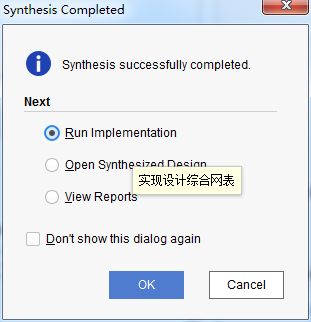

点击SYNTHESIS->Run Synthesis,

Run Implementation.

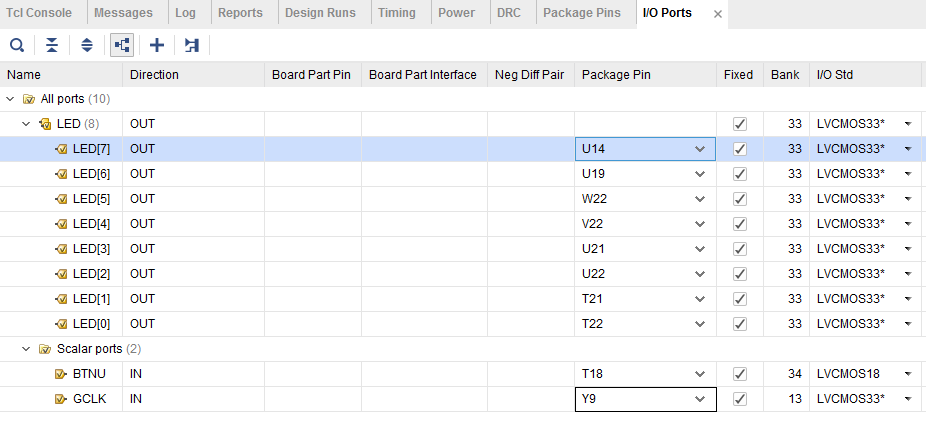

选择Open Implementation Desgin,然后在界面 I/O Planning

在I/O Ports内更改引脚配置,配置如下示:

save,

6.生成.bit文件。

Run Implementation->Genertate Bitstream.

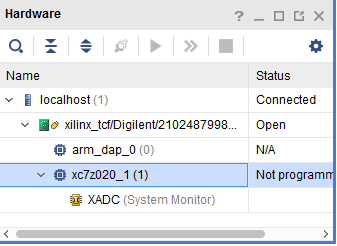

Open Hardware Manager

7.下载。

连接zedboard与pc,

上电,

右键 Program Device ->Done。