找到一篇介绍latch和FF的区别的文章,写的确实是不错。摘抄到这里供参考。

http://www.eefocus.com/blog/link2url.php?link=http%3A%2F%2Fdept-info.labri.fr%2F%7Estrandh%2FTeaching%2FAMP%2FCommon%2FStrandh-Tutorial%2Fflip-flops.html

Latches and flip-flops

In the same way that gates are the building blocks of combinatorial circuits, latches and flip-flops are the building blocks of sequential circuits.

While gates had to be built directly from transistors, latches can be built from gates, and flip-flops can be built from latches. This fact will make it somewhat easier to understand latches and flip-flops.

Both latches and flip-flops are circuit elements whose output depends not only on the current inputs, but also on previous inputs and outputs. The difference between a latch and a flip-flop is that a latch does not have a clock signal, whereas a flip-flop always does.

Latches

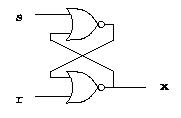

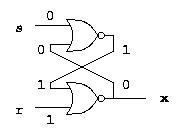

How can we make a circuit out of gates that is not combinatorial? The answer is feed-back, which means that we create loops in the circuit diagrams so that output values depend, indirectly, on themselves. If such feed-back is positive then the circuit tends to have stable states, and if it is negative the circuit will tend to oscillate.A latch has positive feedback. Here is an example of a simple latch:

This latch is called SR-latch, which stands for set and reset.

It is not practical to use the methods that we have used to describe combinatorial circuits to describe the behavior of the SR-latch. Later, we will show a method for describing flip-flops and clocked sequential circuits. For now, we just rely on our intuition to describe how latches work.

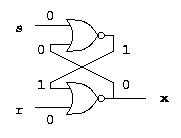

The SR-latch is meant to have at most one of its inputs equal to 1 at any time. When both of its inputs are 0 it has two different stable states possible. Either x is 0, in which case we have the following signal values:

or else x is 1, in which case we have the following signal values:

The actual value depends on the history of input values as we will show next.

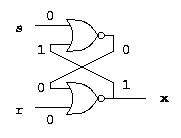

Now suppose that s is 1 (and therefore r is 0 since we allow at most one input to be 1 at any time). We get the following signal values:

The 1 on the s input makes sure the output of the upper nor-gate is 0, and the two 0s on the input of the lower nor-gate make sure the x output is 1.

Now suppose the s input goes from 1 to 0, while the r input remains at 0. The second input of the upper nor-gate is 1, so the transition from 1 to 0 of the s input, does not make any difference. The x output remains at 1. In this case, if the s and r inputs are both 0, there is only one possible stable state, the one that gives x the value 1.

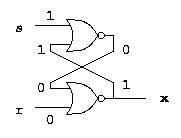

Conversely, suppose that r is 1 (and therefore s is 0 since we allow at most one input to be 1 at any time). We get the following signal values:

The 1 on the r input makes sure the x output is 0, and the two 0s on the input of the upper nor-gate make sure the output of the upper nor-gate is 0.

Now suppose the r input goes from 1 to 0, while the s input remains at 0. The second input of the lower nor-gate is 1, so the transition from 1 to 0 of the r input, does not make any difference. The output of the upper nor-gate remains at 1. In this case, if the s and r inputs are both 0, there is only one possible stable state, the one that gives x the value 0.

From the discussion above, we conclude that the SR-latch is able to remember the last state of the inputs, in the sense that it remembers which of the two inputs, s or r, last had the value of 1.

When we need to draw an SR-latch, we use the following symbol:

Flip-flops

Latches are asynchronous, which means that the output changes very soon after the input changes. Most computers today, on the other hand, are synchronous, which means that the outputs of all the sequential circuits change simultaneously to the rhythm of a global clock signal.A flip-flop is a synchronous version of the latch. To complicate the situation even more, there are several fundamental types of flip-flops. Here, we shall only consider a type called master-slave flip-flop.

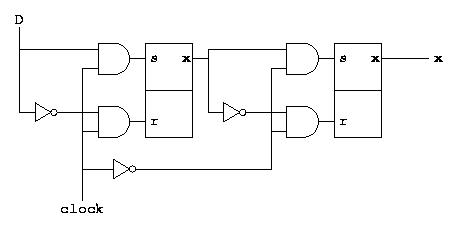

In addition to the fundamental types of flip-flops, there are minor variations depending on the number of inputs and how they control the state of the flip-flop. Here, we shall only consider a very simple type of flip-flop called a D-flip-flop. A master-slave D-flip-flop is built from two SR-latches and some gates. Here is the circuit diagram:

The leftmost SR-latch is called the master and the rightmost is called the slave.

Let us first consider what happens when the clock signal is 1. In this case, the two and-gates in front of the input of the master are open, i.e., they let the value of the D-input through to the s input of the master, and the inverse of the D input to the r input of the master. Thus, the value of the D input will go straight trough the master to the x output of the master. But the two and-gates of the slave re closed, i.e., their outputs are always 0, so the slave keeps its old value.

When instead the clock signal is 0, the reverse is true, i.e., the and-gates at the input of the master are closed, whereas the ones at the input of the slave are open. In this case, the flip-flop is completely insensitive to changes in input.

Now, let us consider what happens when the clock goes from 1 to 0. For this to work, we have to assume that the input remains the same during a brief period from right before to right after the clock signal changes. The first thing that happens is that the and-gates at the input of the master turn off, i.e., they become insensitive to further changes in input. The value of the x output of the master is now the value of the D input right before the clock started changing. A brief moment later, the clock signal transition has traversed the inverter and reaches the and-gates of the slave. These gates open, allowing the x output of the master to be propagated to the x value of the slave. The x value of the slave, and therefore that of the entire flip-flop now contains the value of the D input right before the clock started changing. We can say that the clock transition copied the input to the output of the flip-flop. But at no point in time is there a direct path from input to output. The output changes only as a result of clock transitions from 1 to 0.

Finally, let us see what happens when the clock goes from 0 to 1. First, the and-gates of the master open, letting the value of the D input into the master. By the time the D value reaches the master, the clock signal transition reaches the and-gates of the slave, and turns them off before the possibly modified output of the master reaches the slave. Thus, the slave keeps its old value. From the outside, nothing seems to happen, since the output does not change. From now on, however, the master is open to changes in the input.

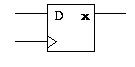

Here is the symbol we use for D-flip-flops:

The little triangle for the clock input indicates that this input is sensitive only to transitions as opposed to levels as described in the previous paragraph. Sometimes we do not draw the clock input at all when it is understood that it is there. Clock signals are boring since they are all just connected to each other. There is therefore little use to draw them all, and thereby clutter the diagram unnecessarily.

Summary

We have shown how to build a D-flip-flop. It copies its input to its output as a result of a clock signal transition from 1 to 0. The value copied is the value the input has immediately before the clock transition. Most of the clock period, the D-flip-flop is insensitive to changes in the input.We shall use this key characteristic of the D-flip-flop to build synchronous sequential circuits.