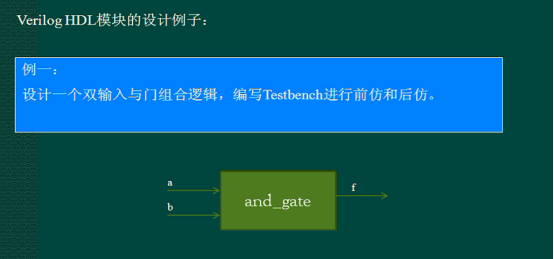

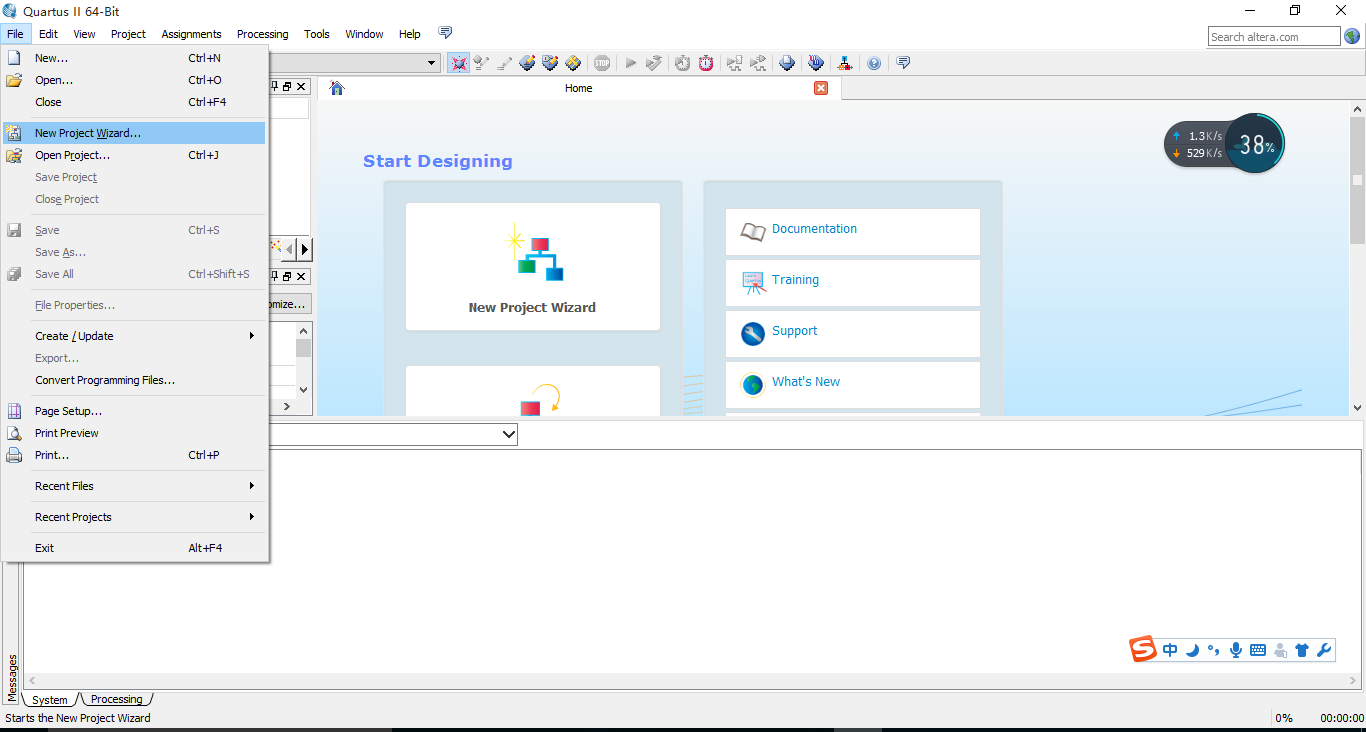

执行菜单命令【File】-【New Project Wizard…】,创建工程向导。

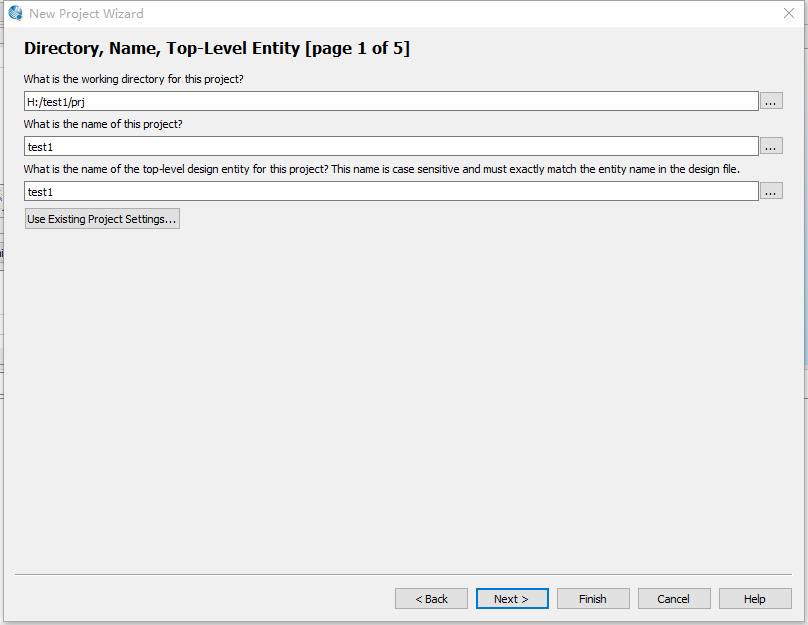

在What is the working directory for this project?下选择项目存储地址工作目录,What is the name of this project?下填写工程名,最后一栏填写顶层文件名。

添加已存在文件(可选),在【File name】下选择已经存在的工程项目,利用【Add】或【Add all】命令添加文件到新工程,点击【Next】

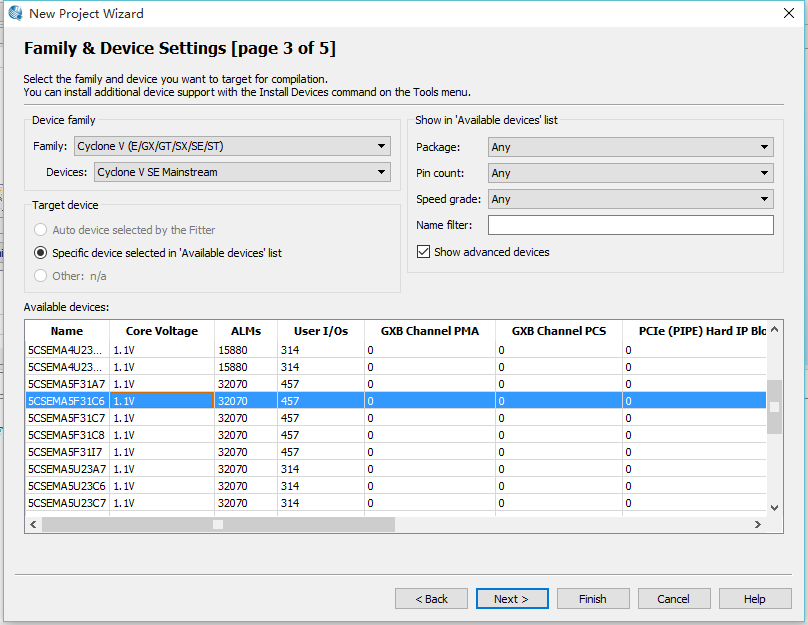

3、选择器件,【Device family】-【Family】下选择你要使用的FPGA芯片系列,这里我选择ALtera公司的CycloneV系列(因为个人用的是友晶的DE1-SOC,芯片型号依个人不同而不同),并在【devices】下选择具体芯片型号,点击【Next】

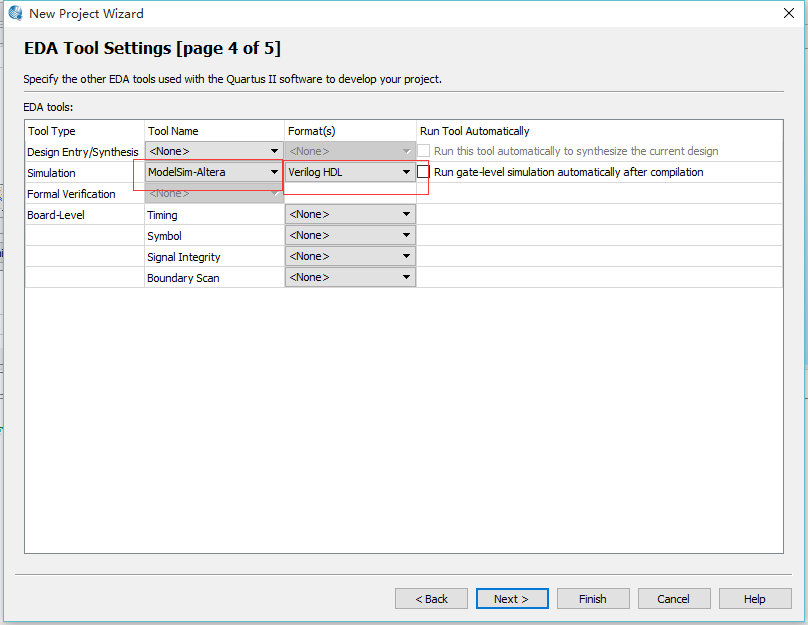

设定第三方工具,【Design Entry/Synthesis】选择逻辑综合工具,这里可以不填,直接使用Quartus默认工具,【Simulation】下选择仿真工具,这里一般需要quartus都配套安装了Modelsim,点击【Next】

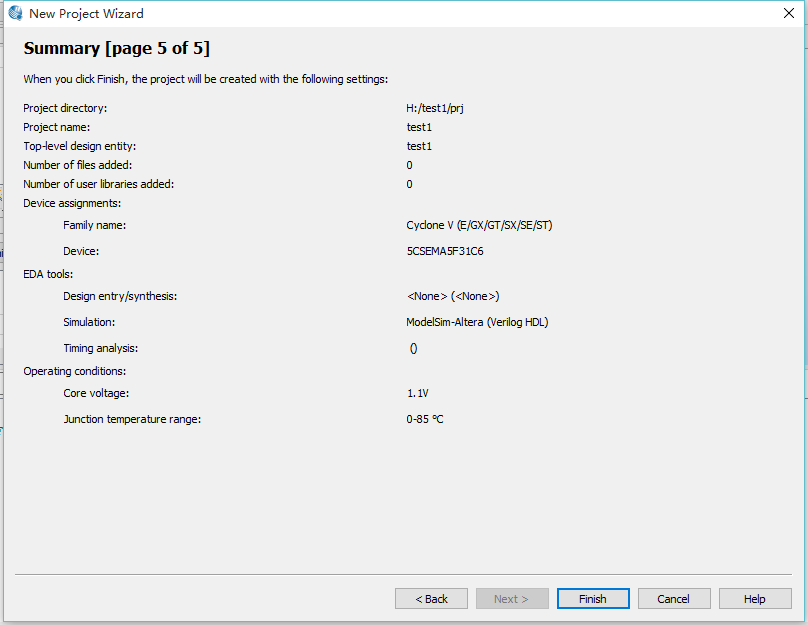

显示设置信息,显示了项目路径,项目名,顶层文件,芯片系列型号等设置信息,在检察符合需要后点击【Finish】,完成向导新建工作。

至此,就完成了一个工程的建立,后面的就是为了工程添加文件。

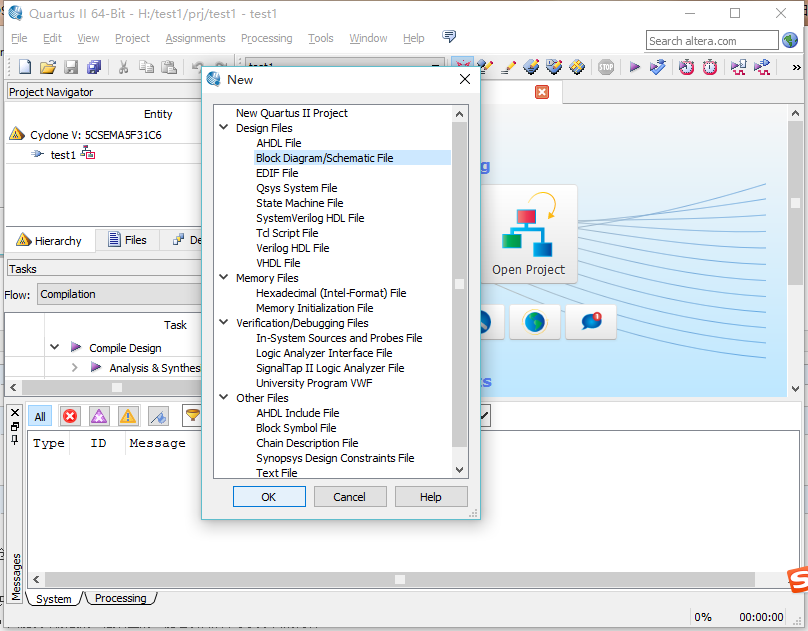

用框图原理图作为文件顶层(此文件可以直接用代码编程完成,此处是借此讲解如何将硬件原理图转化为程序文件)

1、选择文件类型

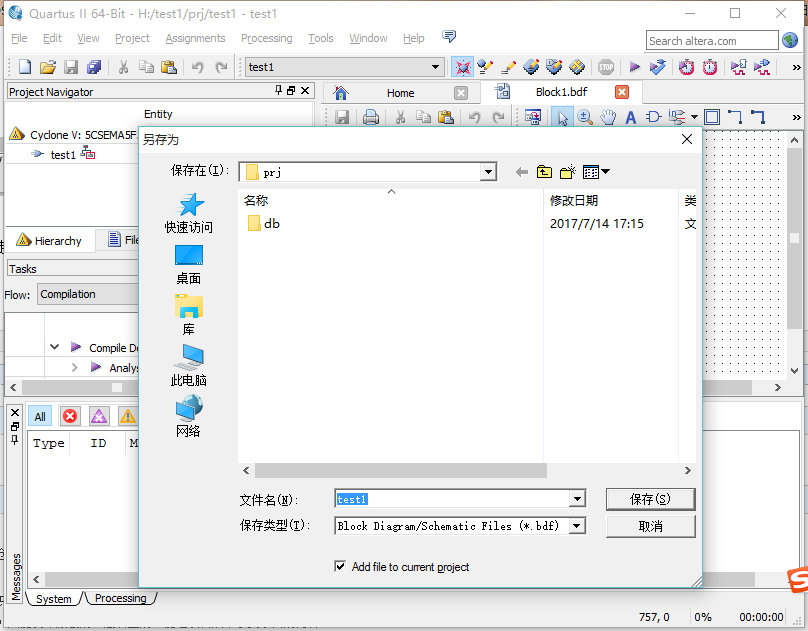

立刻另存为,给顶层文件起名字(这里的名字要和工程名一样)并为它定位

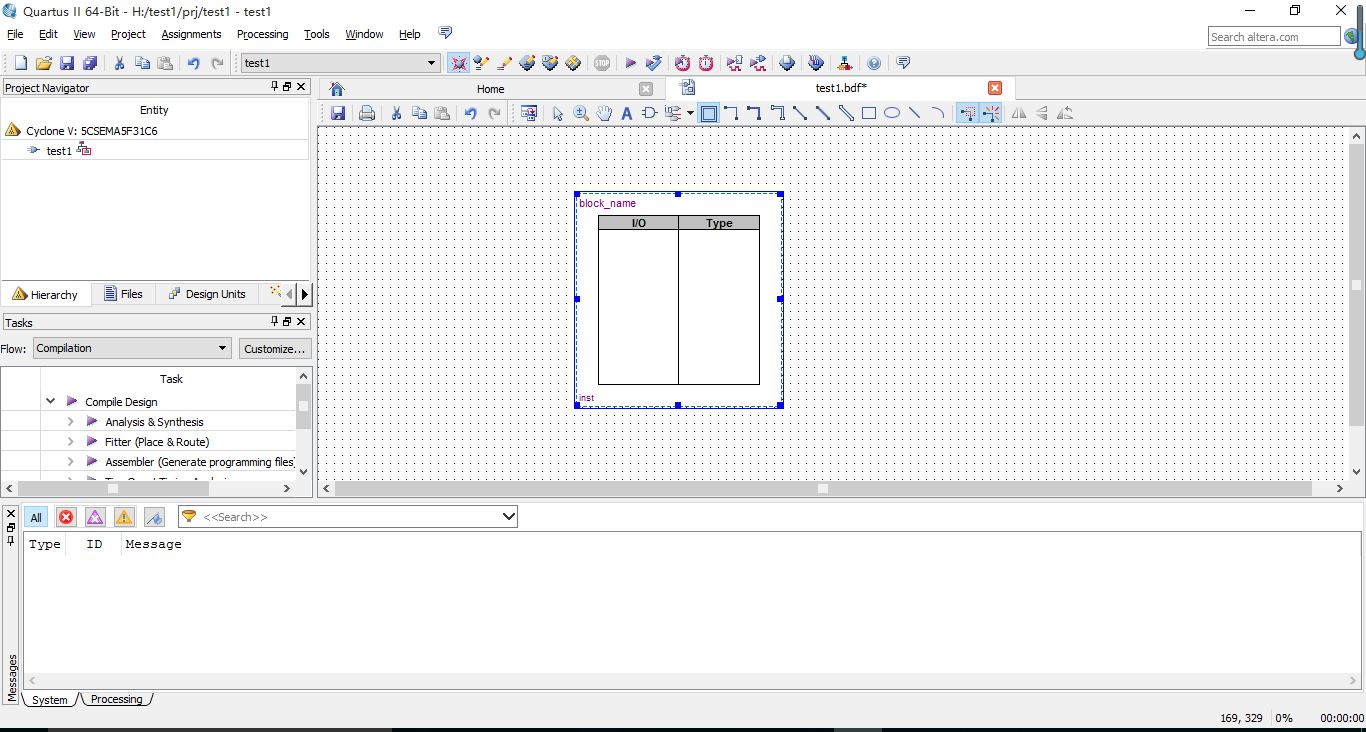

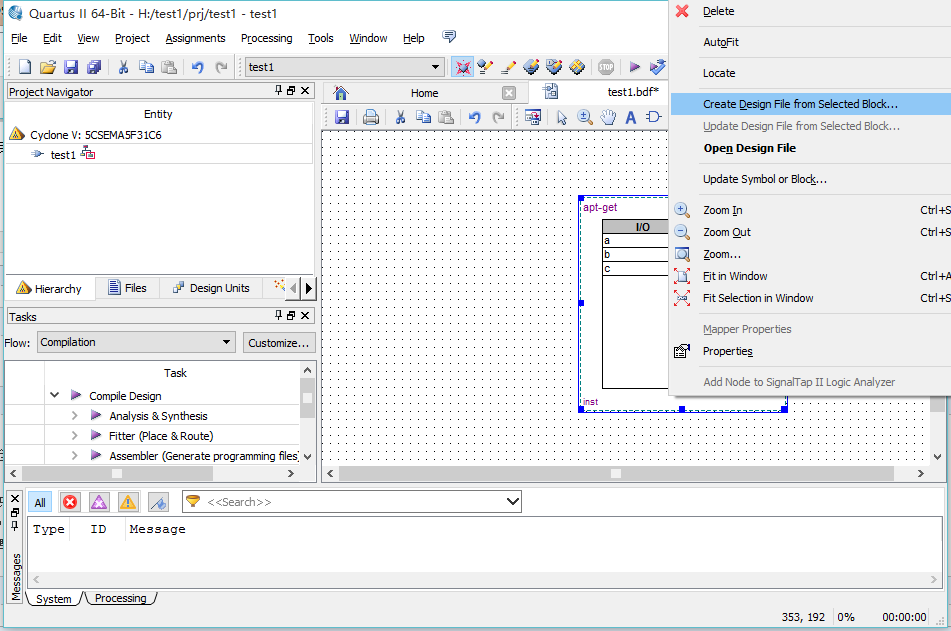

选择BLOCK TOOL,绘制一个block

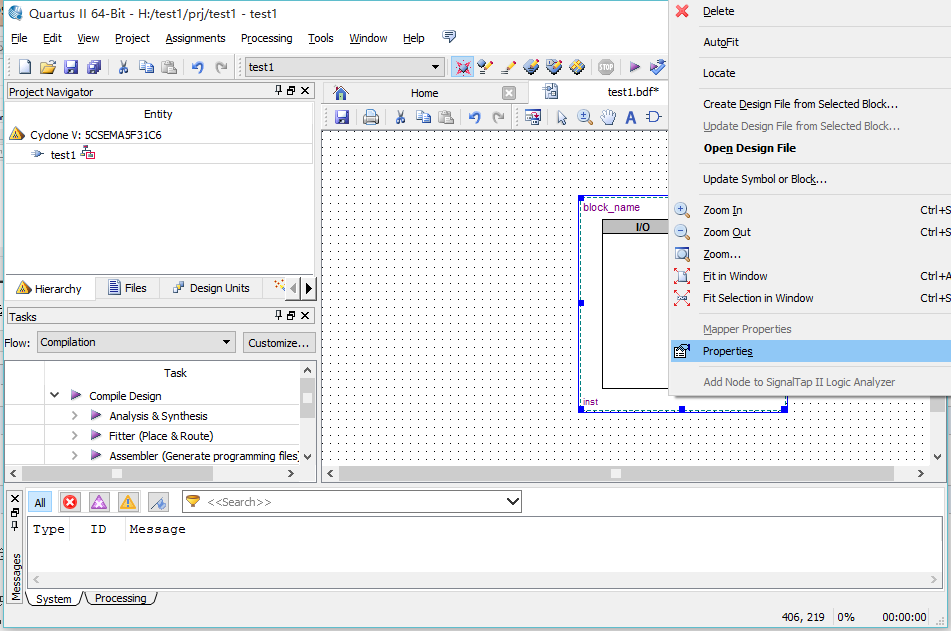

右键绘制出来的block,选择属性

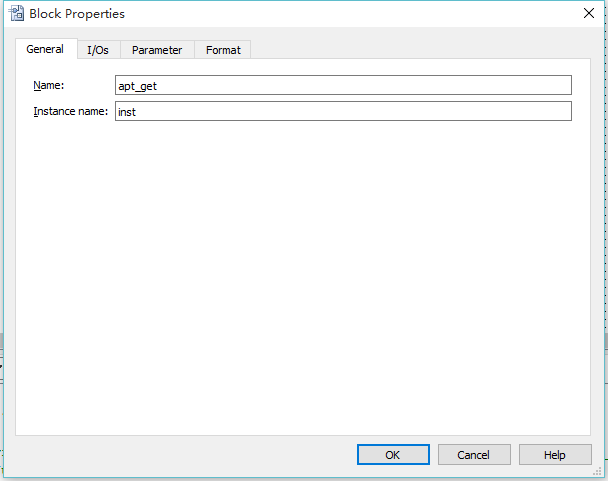

给block命名

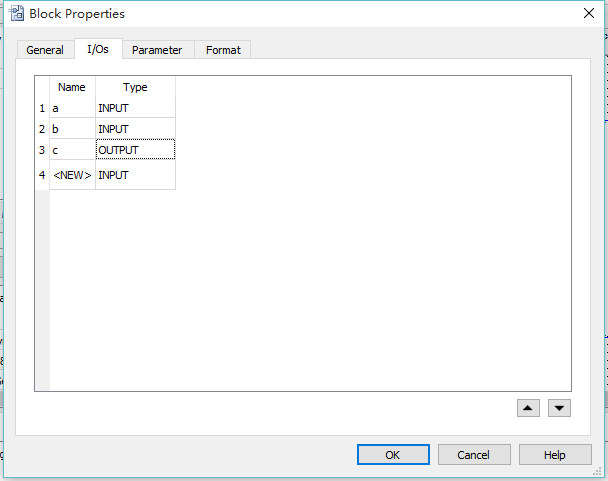

添加定义端口

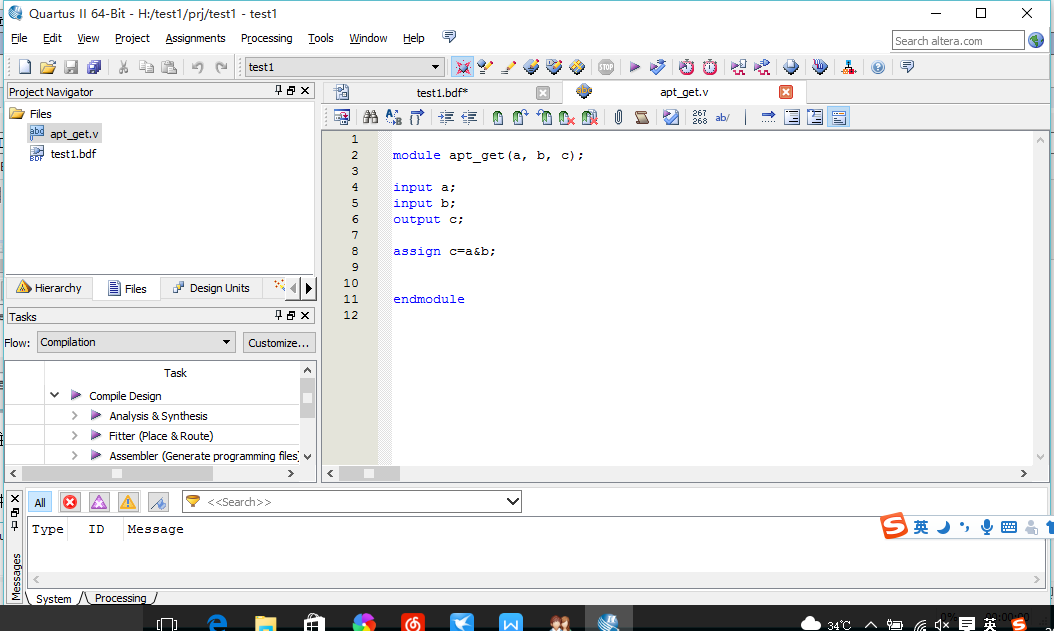

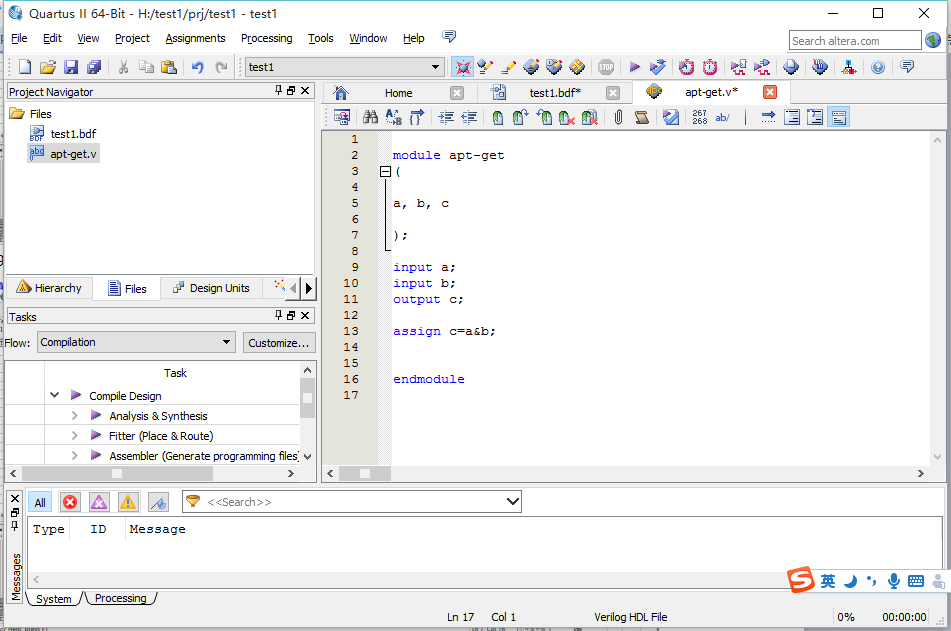

用自带的EDA工具生成一段代码的模板

删掉一些注释,顶层文件就生成了

在生成文件的基础上,添加自己的模块代码

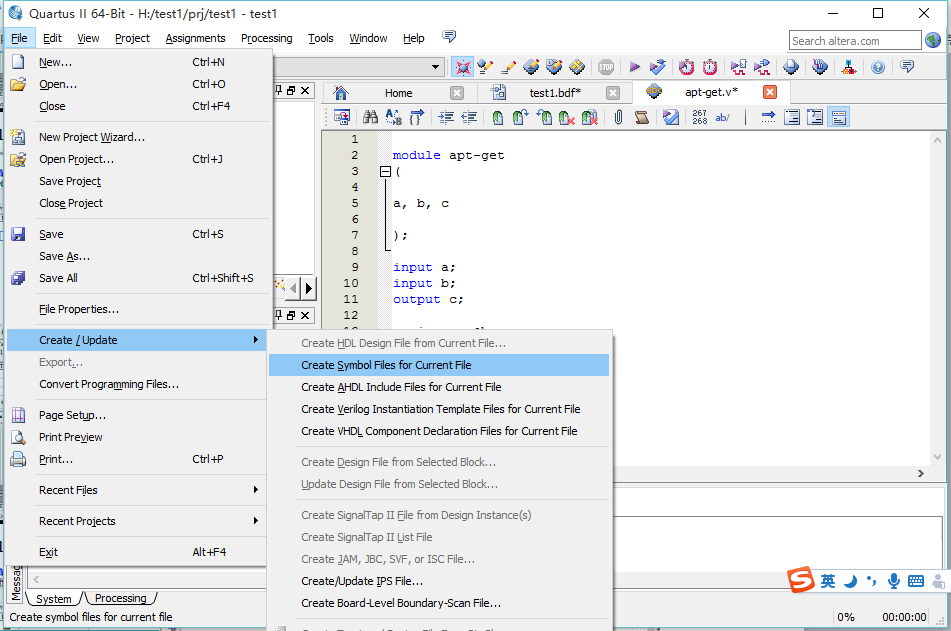

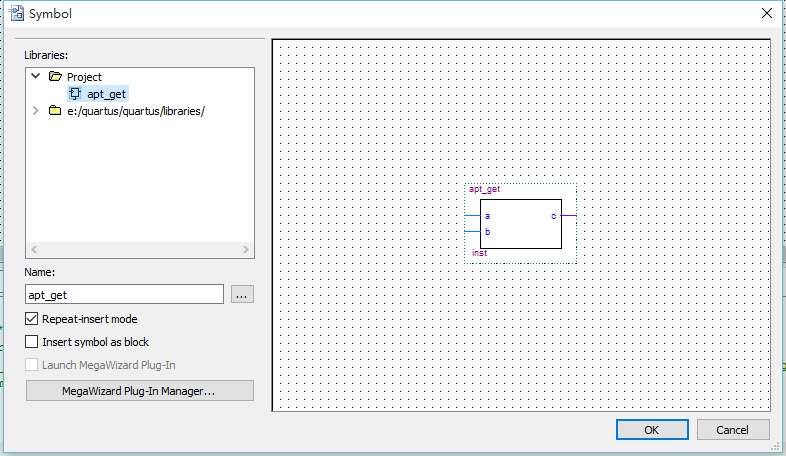

将文件转变为符号

完成后可以在symbol tool看到我们的工程符号

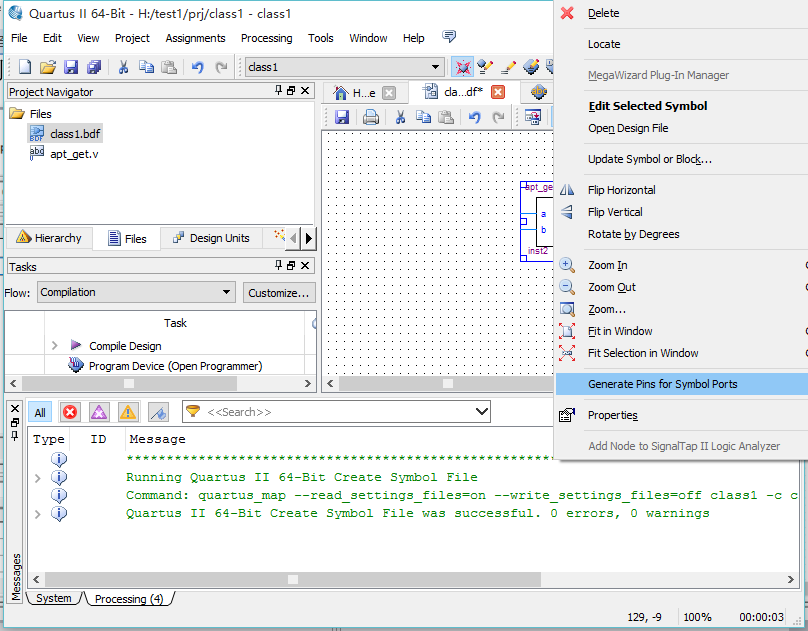

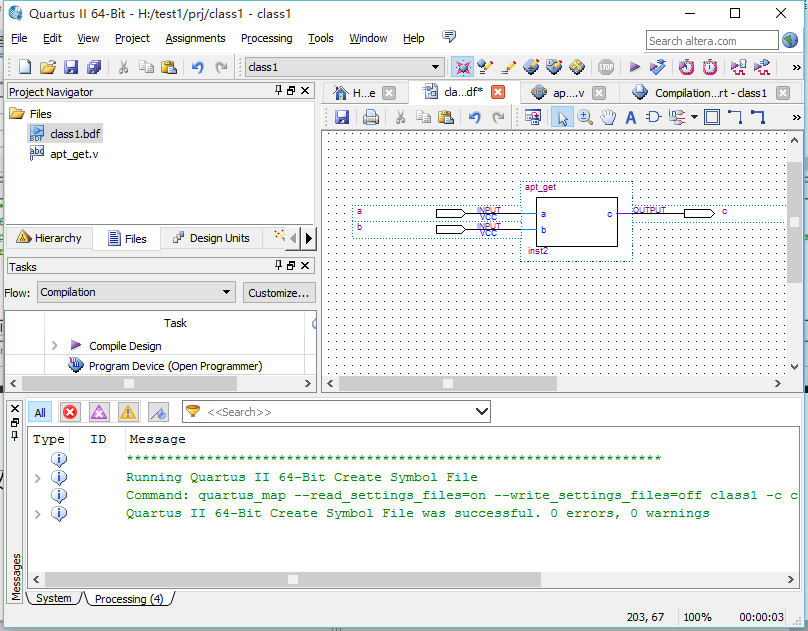

点击生成管脚可以将建立的模型扩展出来

通过 对文件进行编译。

对文件进行编译。

至此一个工程项目就建立完成了。下面就需要编写它的仿真文件,对输出信号进行分析。

编写testbench

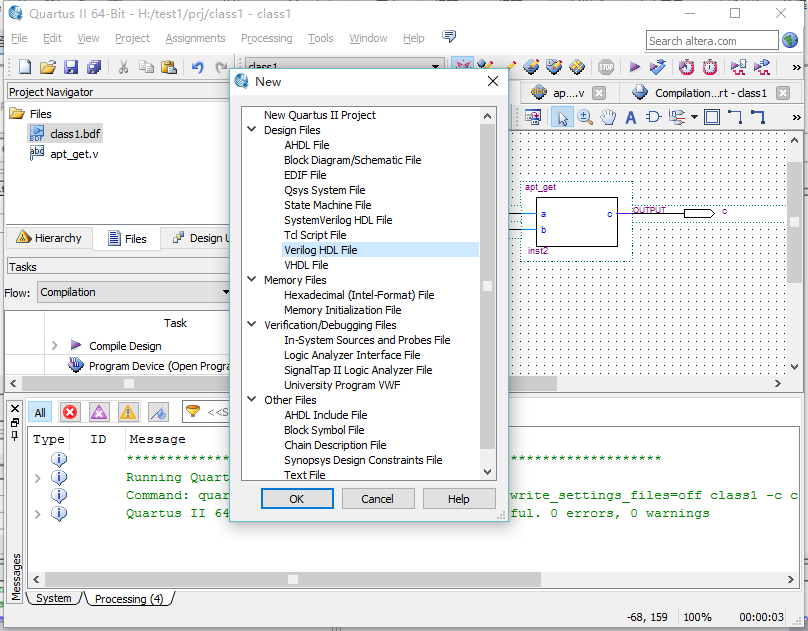

新建verlog文件

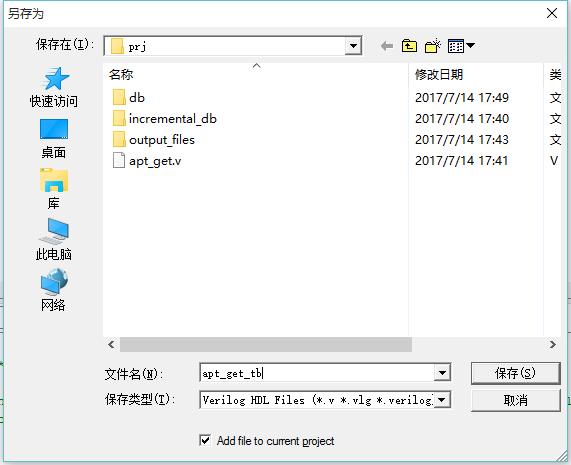

保存,用_tb表示testbench

编写一个时标,时标是有一个分数组成的,分子是当前文件所用的时间单位,分母是分辨率。(最开始的符号是 `,就是esc键下面那个符号)

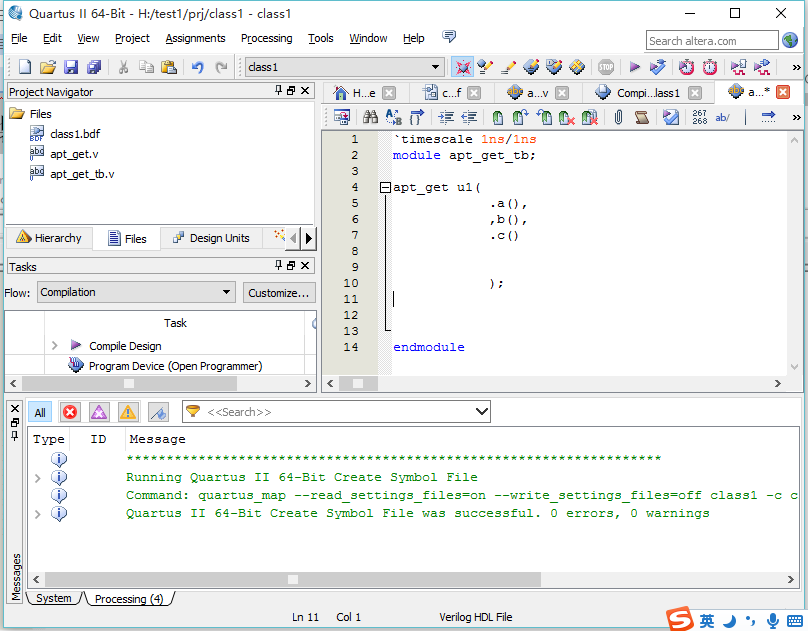

将待测试的模型装载到testbench,将模型的例化头贴到testbench,并为他起一个实例的名称,用.操作符做接口的装配,

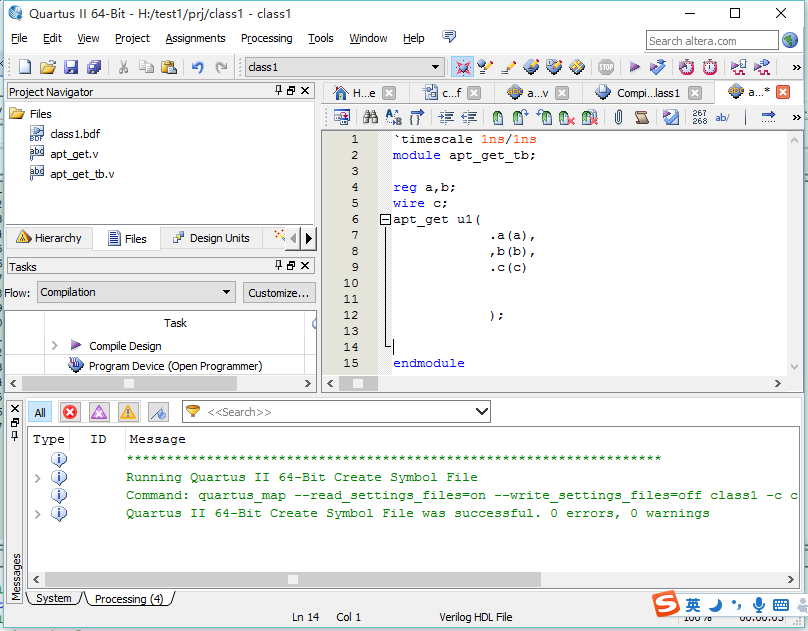

申明要用到的信号,并与电路模型连接

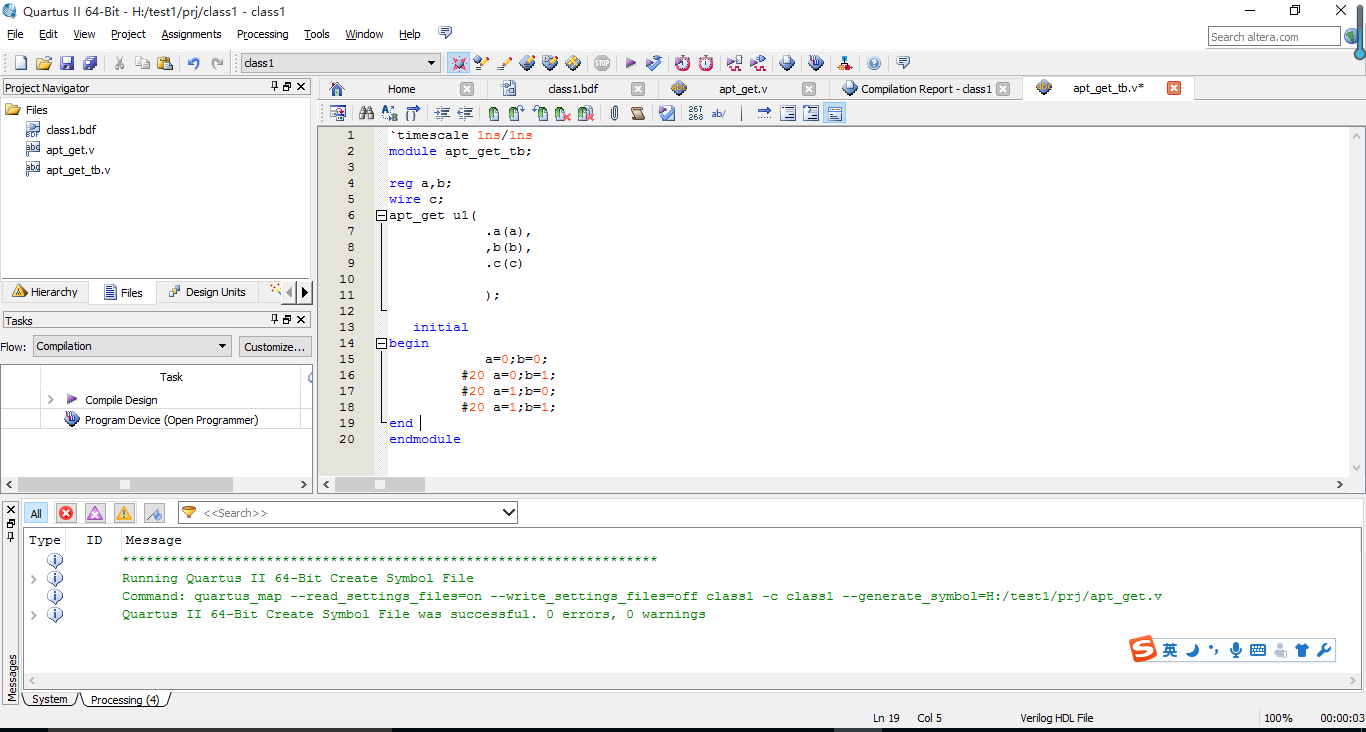

编写测试信号

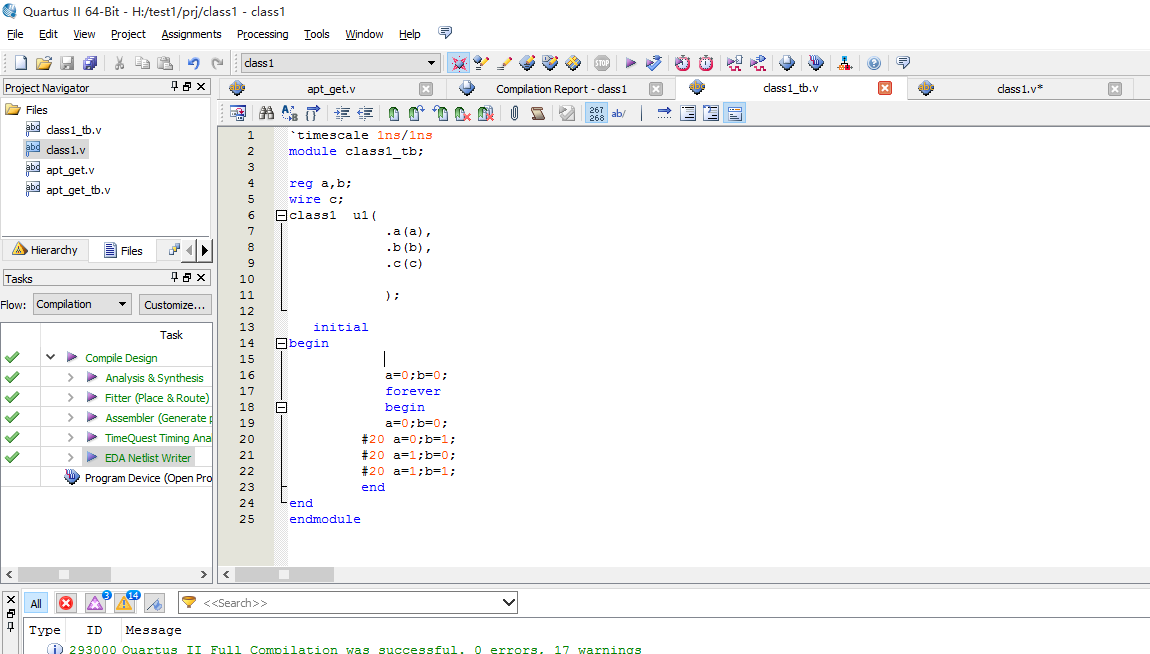

整体代码如下

`timescale 1ns/1ns

module apt_get_tb;

reg a,b;

wire c;

apt_get u1(

.a(a),

.b(b),

.c(c)

);

initial

begin

a=0;b=0;

#20 a=0;b=1;

#20 a=1;b=0;

#20 a=1;b=1;

end

endmodule

至此,测试平台就完成了。

将testbench用modelsim仿真

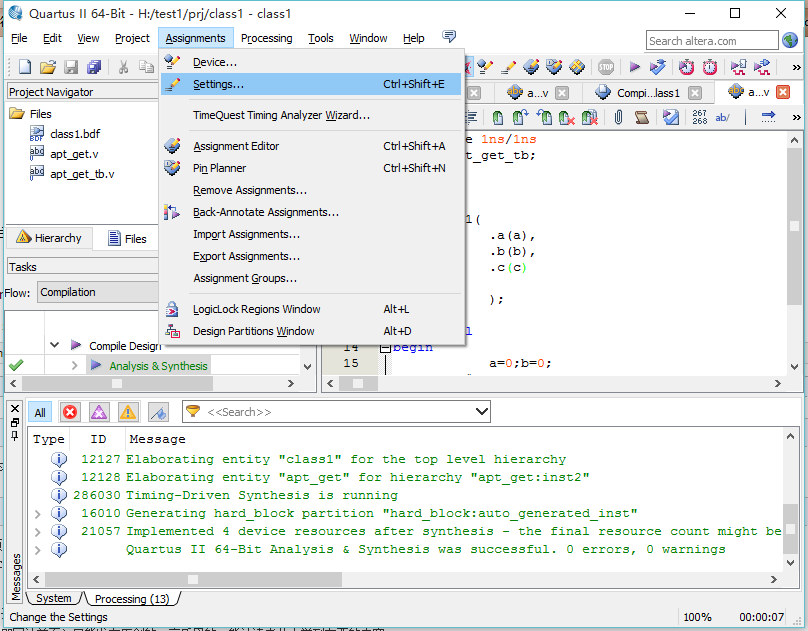

在assignment—setting中对设置进行更改

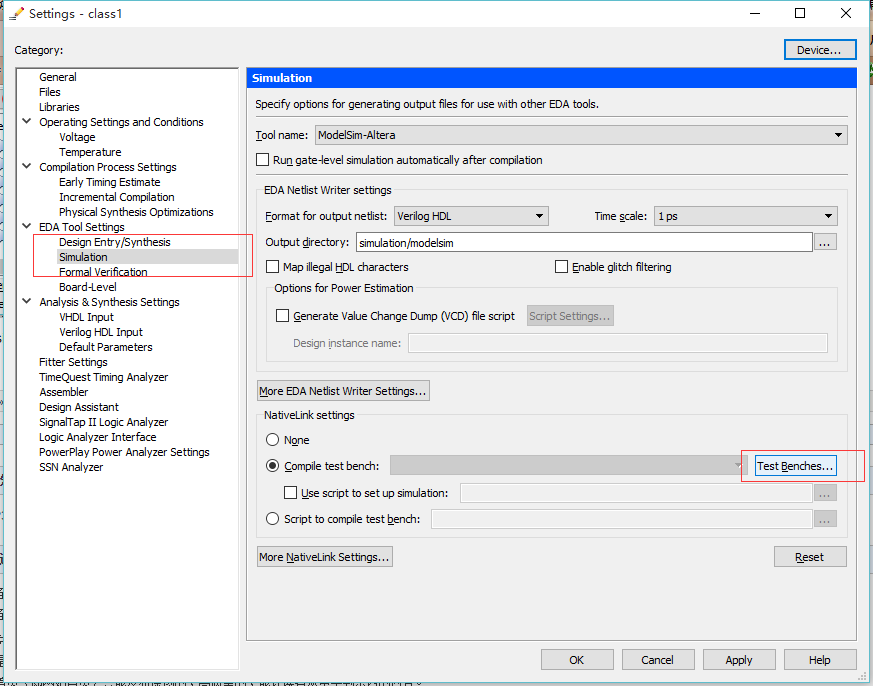

设置中的simulation进行如下设置后点击testbench

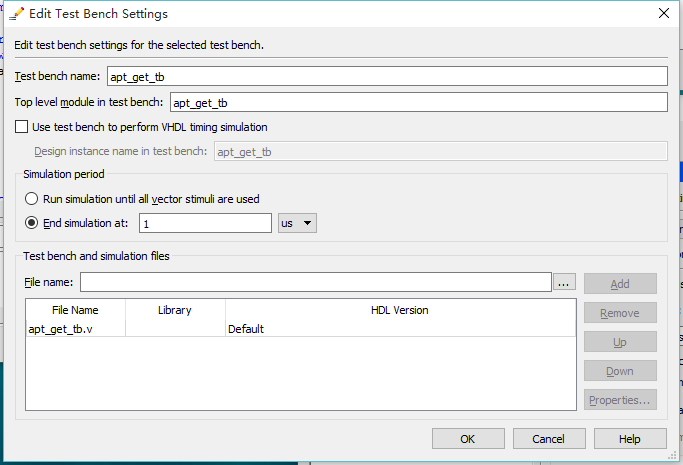

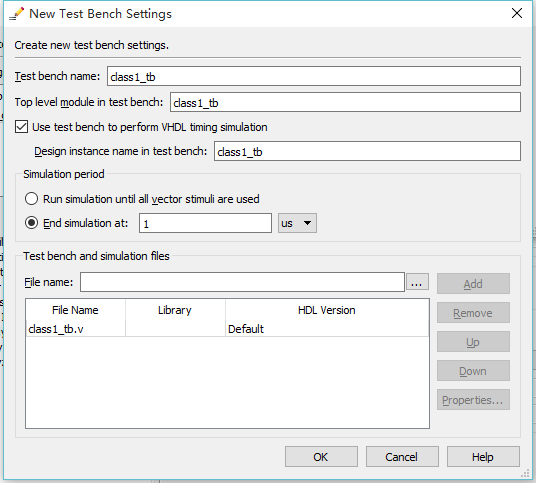

添加testbench及仿真结束时间,(filename里添加的是.v文件不是.bak文件)

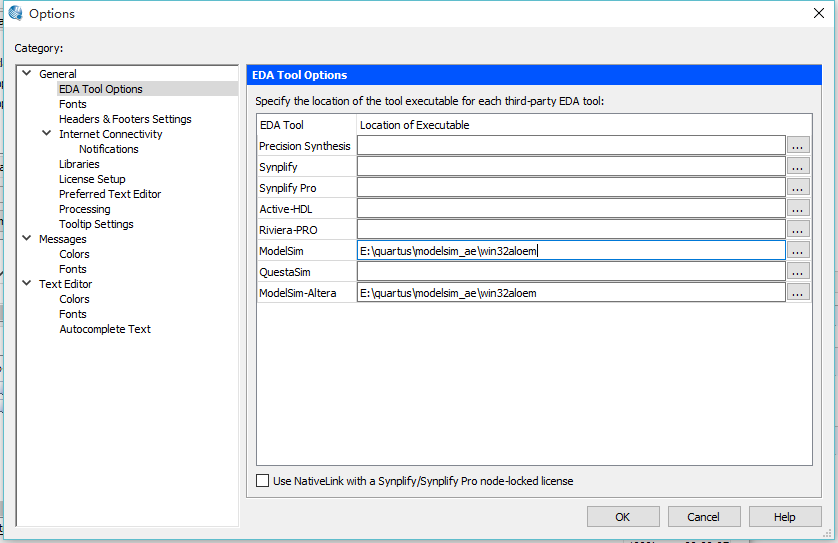

最后在quartus中设置modelsim的路径,quartus->tools->option->EDA tool options ,在右边选择modelsim_altera的安装路径

这里要确保自己的quartus和modelsim都是已经取得了lincense的,否则是调用不了modelsim的

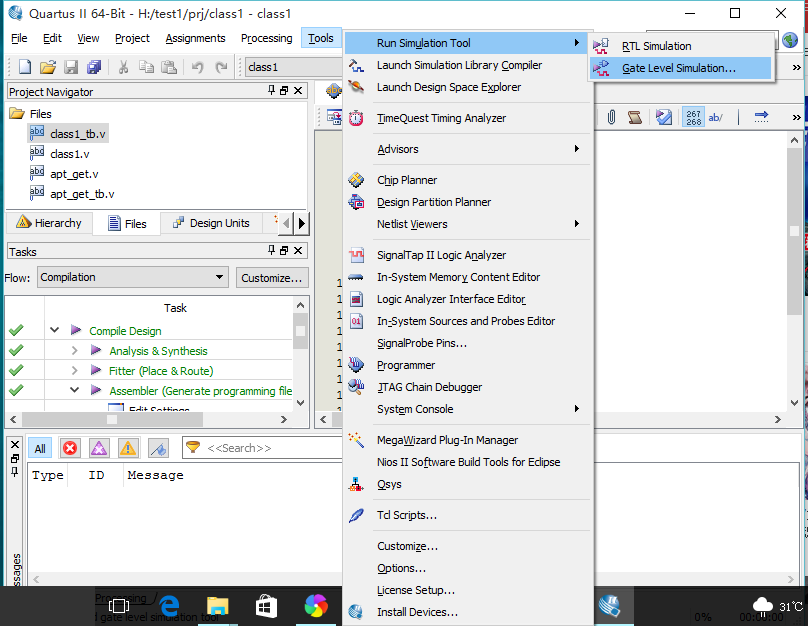

前仿

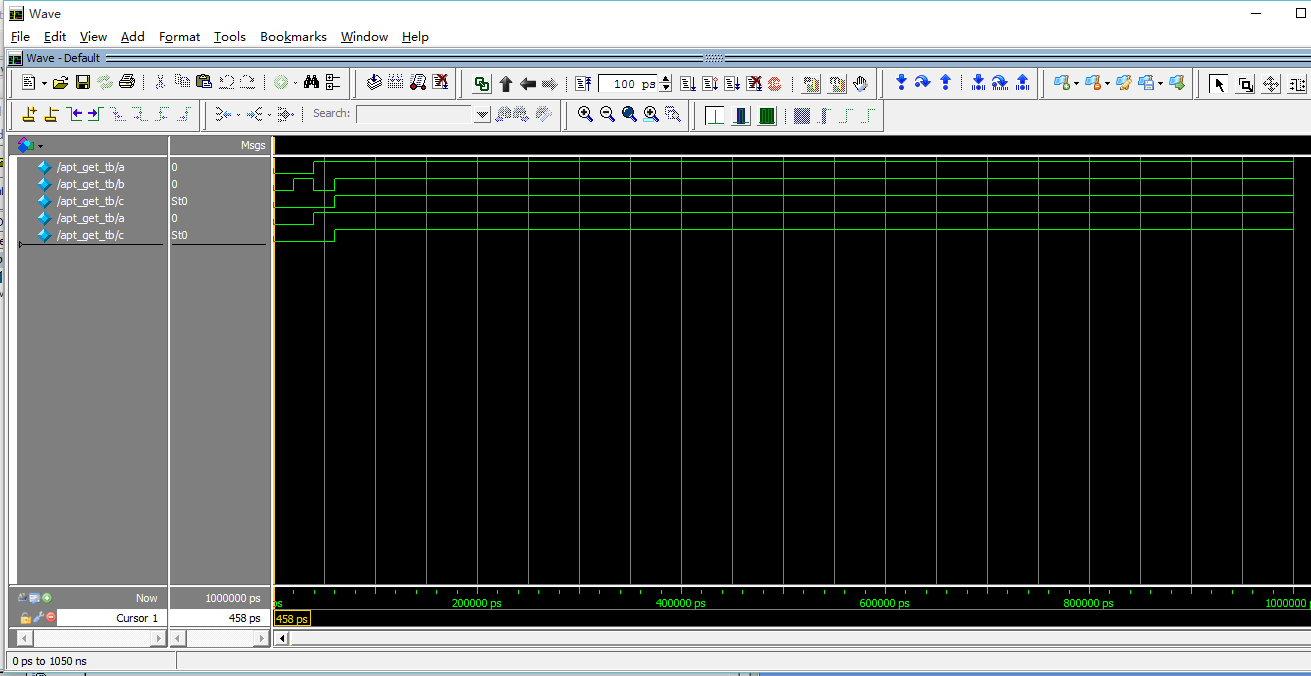

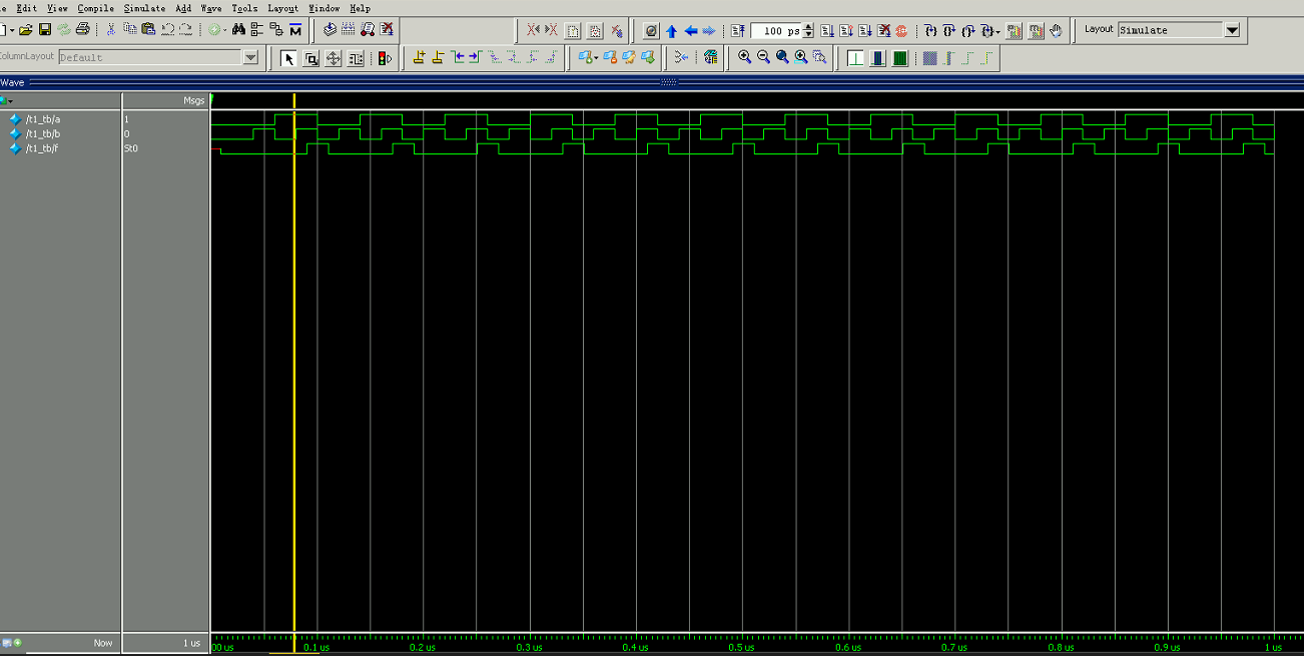

软件自动跳转modelsim生成仿真图形,通过按键盘上的F键可以看他的全局图

修改过的testbench文件保存后,可以按方向键上键,调用用过的.do 文件,即可重新仿真。

至此,前仿的验证完成。

后仿

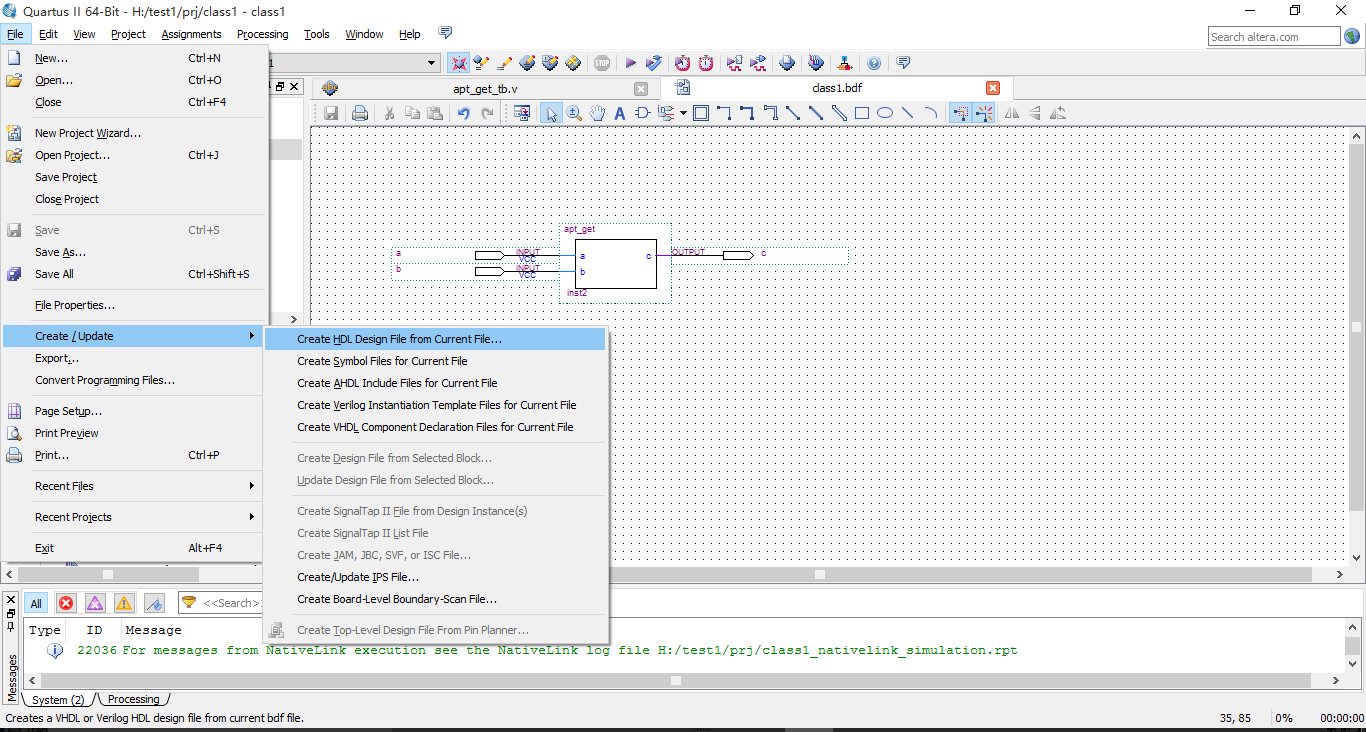

由于框图原理图不能作为一个国际标志在平台中互相传递,所以需要用系统工具将图形改为代码

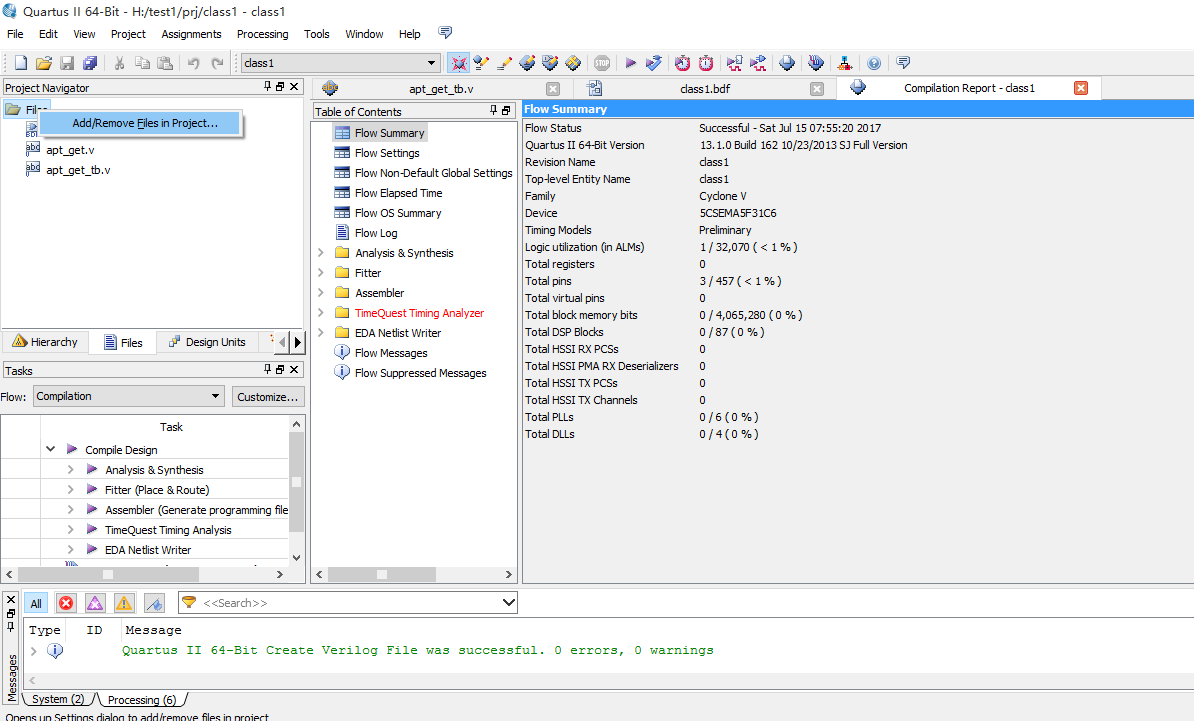

完成后,将生成的文件加入到file中

为顶层的代码编写一个testbench

之后的步骤与前仿相同,但应理解的是此时做的是顶层的仿真,是后仿

综合编译后,就可以做顶层的前仿和后仿了,前仿按照之前的来,这里演示后仿

可以看到后仿与前仿存在着时序上的延迟,这是器件的延迟,这便是一个更真实的仿真结果。

(需要注意的是cyclone V系列的芯片已经不再支持时序仿真了,只能跑功能仿真,如果芯片类型选的是Cyclone V系列的话,它就会一致弹出

)

前仿看到的是逻辑功能间的关系,后仿不仅可以看到逻辑功能间的关系,还能看到他们时序间的关系。