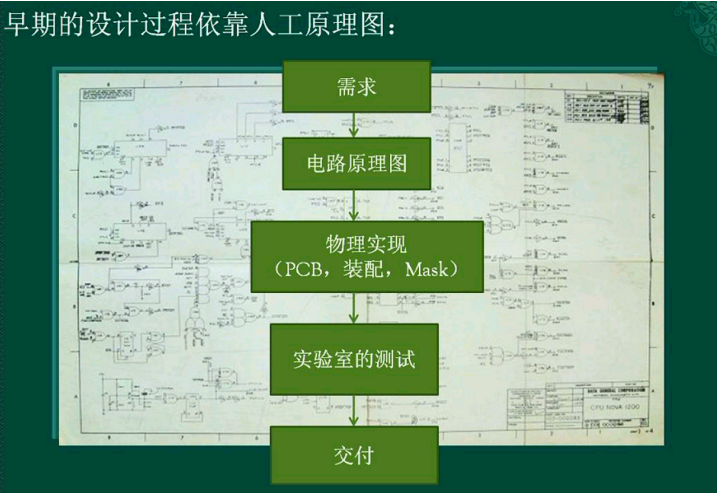

通过了解早期FPGA的发展,理解FPGA究竟是干什么的,FPGA到底在电子设计领域起到了什么样的作用,下面是一张早期的设计过程

早期的设计流程过程中,只有当硬件完成了才能够得到功能的验证,随着集成电路开发的规模来越大,渐渐的需要一种快速有效的开发平台来完成预期的功能设计的验证,减少研发周期及研发成本,由此引入了EDA技术,首先是使用一种语言系统来描述一个硬件模型(即VHDL),其语言着重在描述性上,即重点在建立电路模型的过程上

此处就应该知道电路模型应该具备全部的电路特征:

(1)必要的输入和输出

(2)必要的内部信号

(3)特定的逻辑和时序行为等

这里就是FPGA开发语言与C语言之间本质性的差距(C语言是过程描述语言)。

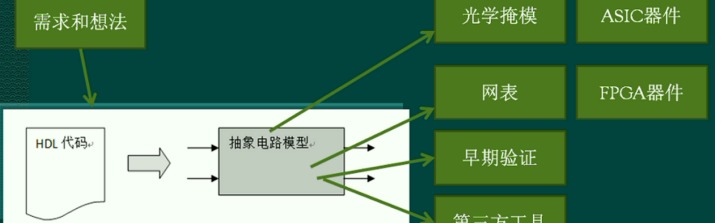

在完成需要与想法后,即完成EDA设计后的一些应用方面如下图

用HDL描述的抽象硬件模型,verilog里面称为Module。

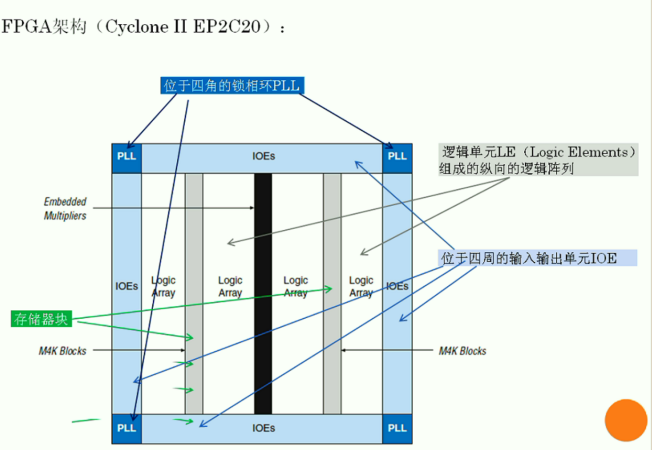

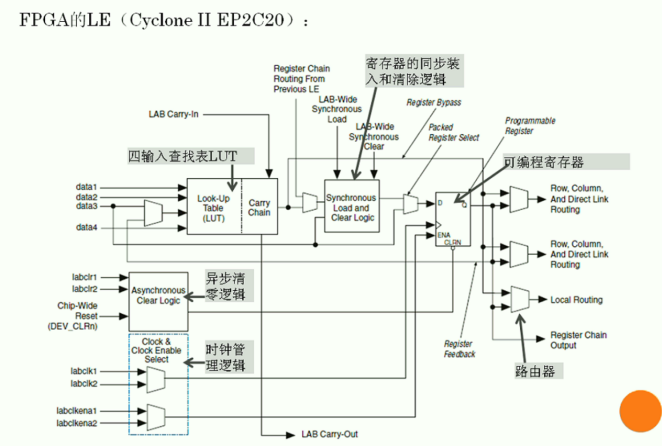

FPGA的verilog设计中,用到是查找表的方式来完成的对任意的组合逻辑的实现。在FPGA内部包含许多单元LUT(查找表),IOE(输入输出单元),Memory(内存)和DSP(乘法器等硬件电路主城)等构成。

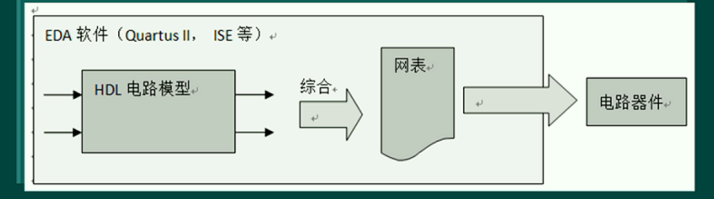

EDA工具如何将我们的语言转化为FPGA可应用的硬件电路。

编译:将HDL 模型转变为基本的门级网表。

映射:为这些基本的门模型分配具体的cell。

映射后的网表即可以直接烧录到FPGA的器件里面。

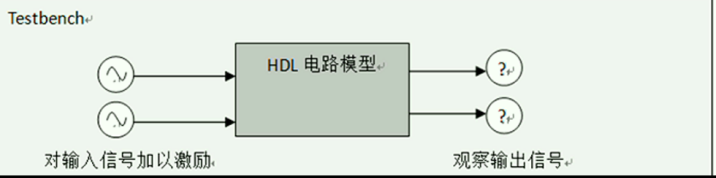

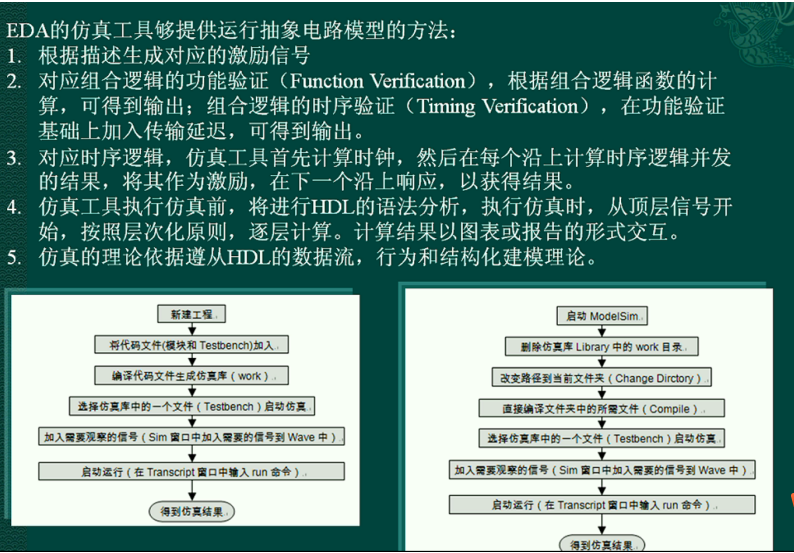

硬件模型代码编写好后,需要对抽象的电路模型进行测试,称之为验证,为了进行验证,需要单独编写一段HDL代码,建立一个用于测试的模型,此模型称为Testbench

由于Testbench是一个真实的仿真平台,所以其本身也是不能运行的,EDA软件会提供一种运行Testbench的方法,这种抽象的方法称之为仿真。

仿真又分为

综合前验证(加载的为RTL模型),主要验证测试模型的逻辑性能。

综合后验证(加载的为网表),主要验证的是设计模型的时序性能。

Quartus II主要用来做设计编译及时序分析,仿真则需要用到ModelSim来进行验证。

(感觉和单片机的KEIL和protues的关系很像。

EDA的仿真工具ModelSim

技术报告大多数是modelsim做的验证,有论文需求和技术文档需求的小伙伴门可以看下,有开发板的貌似可以直接烧录了,不过还是仿真后可以看的更清晰)

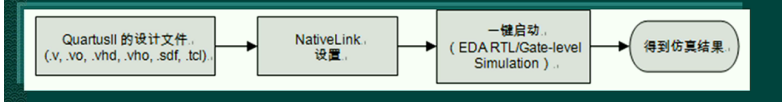

由于仿真过程中需要的调用很多跨平台的文件,Altera提出了一键跨平台的自动化方式,称为NativeLink(使用时要注意层次化设计),这在后面的文章中会详细的讲解到

FPGA的逻辑单元

可编程寄存器是带沿触发的,由此可以构成时序逻辑。

提供路由器可以跟不同的逻辑单元进行来连接。

异步清零逻辑是为了在异步时序逻辑中提供异步清零的逻辑。

因为逻辑单元里面可能会有多个时钟对逻辑单元进行处理,所以需要有个时钟的管理。

查找表原理:任意组合逻辑的乘积项SOP对应n输入多路器实现。

这篇文章旨在讲述FPGA的作用及FPGA的一个基本的开发流程,如何将理论和实际结合起来,最后希望通过这篇文章让大家了解为什么verilog HDL语言和C语言(面向过程)以及JAVA(面向对象)、python(面向逻辑)等语言有本质的不同,因为它是一个并不是一个面向开发过程的语言,它只是一个描述性语言,开发逻辑及开发过程需要通过数电及微机接口的知识来完成,它的作用仅仅是将期望的逻辑用人和FPGA都能够理解的方式表达出来,然后传递到FPGA中让他按照人的意愿来实现相应功能的一门语言。