FPGA&数字IC笔面试常考系列

题目:简述ASIC设计流程,并列举出各部分用到的工具。

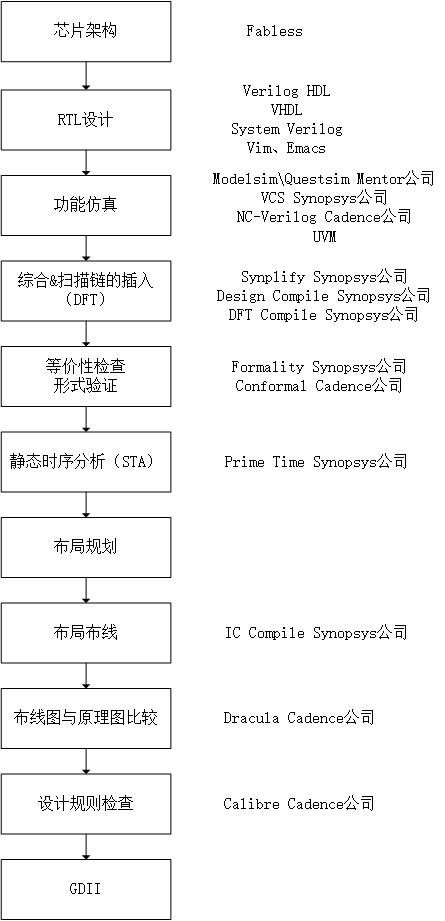

ASIC开发基本流程

芯片架构,考虑芯片定义、工艺、封装

RTL设计,使用Verilog、System Verilog、VHDL进行描述

功能仿真,理想情况下的仿真

验证,UVM验证方法学、FPGA原型验证

综合,逻辑综合,将描述的RTL代码映射到基本逻辑单元门、触发器上

DFT技术,插入扫描链

等价性检查,使用形式验证技术

STA,静态时序分析

布局规划,保证没有太多的内部交互,避免布线上的拥堵和困扰

时钟树综合,均匀地分配时钟,减少设计中不同部分间的时钟偏移

DRC,设计规则检查

LVS,布线图和原理图进行比较

生成GDSII

这整个流程称为RTL2GDSII,利用GDSII来生产芯片的过程称作流片(Tapeout),以上是一个Fabless公司的简易设计流程,最后将GDSII送至Foundry生产芯片。

题目:简述FPGA的开发流程。

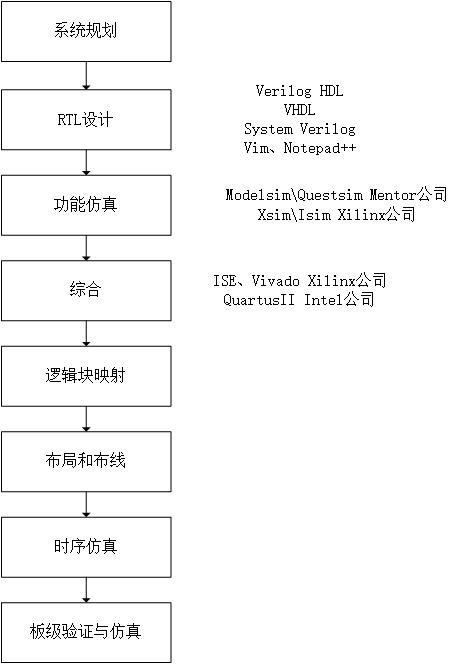

FPGA开发基本流程

系统规划,系统功能,功能模块划分

RTL设计,使用Verilog、System Verilog、VHDL进行描述

功能仿真,理想情况下的仿真

综合、编译、布局布线,FPGA厂商自带工具完成

时序仿真,时序分析约束

板级验证

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan