在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2、4、8、16、32、64等这些以2的整数倍的。

这里说的是奇数倍分频,如时钟是100MHz,需要一个20MHz的输出频率,那么就需要5次分频,那么问题来了,安装2分频的方法:100/2=50,50/2=25,只能等到一个25MHz的频率,显然这种方法是不可行的,那么就需要奇数分频了。

1、做个模为5的计数器,

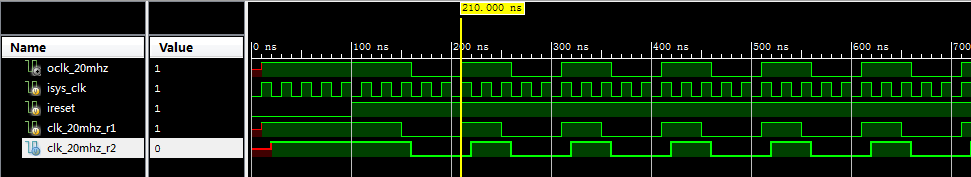

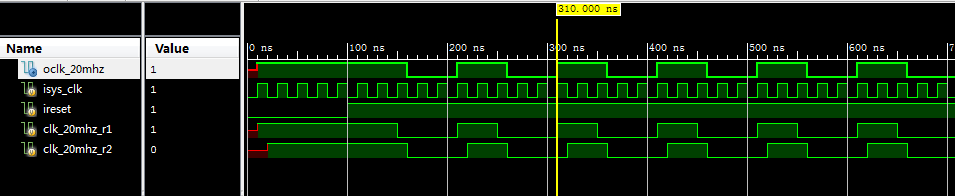

2、做两个个信号a,b。在模1的计数下,前2个周期信号a为高电平,后3个周期信号a为低电平。

3、用时钟的下降沿将信号a延时一个节拍,得到信号b。

4、信号a或b运算输出时钟,即得到占空比为1:1的5分频20MHz时钟频率。

程序中a为clk_20mhz_r1,b为clk_20mhz_r2。

module system_clk

(

input isys_clk,

input ireset,

output oclk_20mhz

);

reg [2:0] cnt_20mhz;

reg clk_20mhz_r1;

reg clk_20mhz_r2;

always @(posedge isys_clk or negedge ireset)

begin

if(!ireset)

cnt_20mhz <= 3'd0;

else if( cnt_20mhz >= 3'd4)

cnt_20mhz <= 3'd0;

else

cnt_20mhz <= cnt_20mhz + 1'b1;

end

always @(posedge isys_clk )

begin

if( cnt_20mhz < 3'd2)

clk_20mhz_r1 <= 1'b1;

else

clk_20mhz_r1 <= 1'b0;

end

always @(negedge isys_clk)

begin

clk_20mhz_r2 <= clk_20mhz_r1;

end

assign oclk_20mhz = clk_20mhz_r1 | clk_20mhz_r2;

endmodule