我们知道dc是为了约束.可是要约束谁? 怎么能把位置描述清楚.?

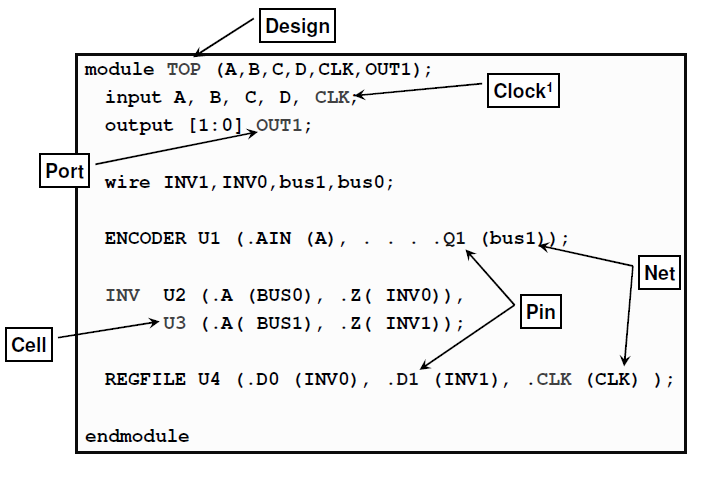

DC在读入所有的verilog文件,link、check_design后,把整个current树分成了一下几个组成:

所有吃进来的module,都称为design. 只有current-design的 in/out 被称为Port

内部所有的例化,统一称呼为cell,cell的in/out称为pin.

剩余的连接线, 统一称呼为net. 通过这些,基本上就能细分了. 至于clock是特殊的一种.先不讲 .

在这幅图中 design 有 { TOP ENCODER REGILE } INV因为是stdcell,不是verilog描述的,所以不能算design

cell有 { u1 u2 u3 u4}

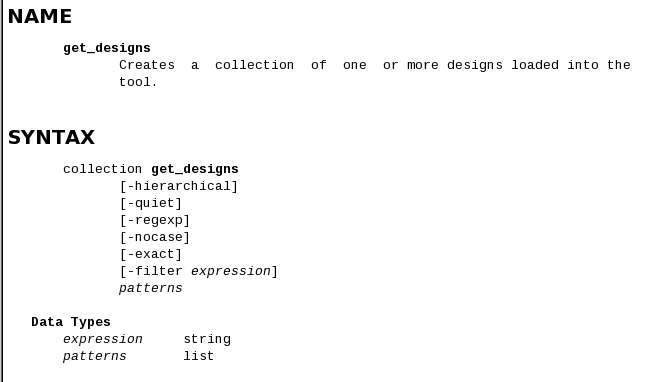

需要详细的了解下: designportcellpin etclock的用法, 以get_designs为例子 这6个有一个共同的称呼: Object 对象.

get_designs

get_designs : 返回所有的design名字。 包括current-design、以及所有吃进去的verilog module

get_designs -h : 把current_design剔除掉,只是其他的designs

-quiet : 压住warning信息不报.

-regexp 进行正则匹配,而不是使用dc内部的简单匹配。

-nocase 不区分大小写

-exac : 貌似是不匹配简单项目,

-filer expression : 先get出结果,然后用expression对所有的结果进行过滤。得到最终的结果

pattern 匹配表达式.

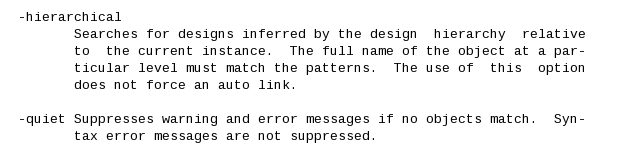

使用 -regexp 选项, 此时使用的是TCL的正则表达式. 最好用 {} 括起来.这个时候 *表示任意数量 . 表示一个字符 ?表示0/1数量。

不适用 -regexp * 代表任意多个字符 ?代表1个任意字符

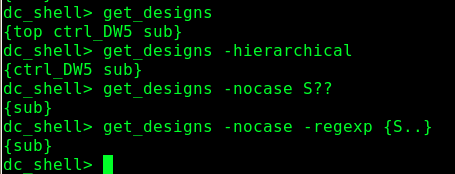

看下下面的例子: get_designs获得所有。

get_designs -h 剔除current_design

-nocase -regexp 选项搭配。

还需要注意一点 , get-designs 返回值不是list. 是一个collection. 本节最后,会将collection到底是什么.

虽然从dc界面上看像是一个list.但其实是一个collection.可以套接在 collection命令上.

常见的collection命令有: add_to_collection remove_from_collection quiet_objects sizeof_collection filter_collection

我们知道 get_* 获得的是collection,然后可以对其使用 add_to_collection remove_from_collection quiet_objects sizeof_collection filter_collection

这些命令进行 更细致的操作,从而得到想描述的object.

set foo [get_designs *]

set foo [ add_to_collection $foo [get_ports *] ] 在foo的基础上增加ports

set foo [remove_from_collection $foo [get_designs *] ] 在foo的基础上剔除掉designs,只剩下ports了

sizeof_collection $foo 得到是ports的个数。

quiery_objects $foo 得到ports的列表.

filter_collection 是依据 collection元素的属性进行筛选的. 简化变成get_* 的 -filter expression选项了。

需要理解一点: collection是集合, 很多元素的集合. 而且这些元素还有不同的属性, dont_touch、is_mapped、is_cell、is_hierarchical等等。

我感觉整个collection是这样的一个结构.

collection由元素组成,元素又有各种不一样的属性。 我们综合时,就是要找到元素,确认其属性,对其增加属性。

DC综合时,也需要去根据我们 设置的属性, 当然 protspindesigncell etcolck自己本身的attribution都不一样。

我们可以使用 list_attribute -class cell 查看cell的attribution。

我们约束的语法: 增加删减 每个attribution,达到我们的综合目的.

后面的章节我们就要学习: 要去设置哪些属性

我理解进行约束的过程,可以分成以下三步

(1) get_* 粗略获得object、

(2) collection命令 微调object、

(3) 对目标object, 增加删减 attribution.

通过这三步,我们就能把约束,添加到目标位置. 达到了精确制导. 所有的语法都是为这个目的服务的.