这是一个实验课.

读入一个vhdl文件,并完成整个dc流程。

实验lab2总结:

复盘: 一开始读入verilog时候,cwd出现了大量的中间文件。 查了read_vhdl也没找到怎么修改存储路径。后来在student guide里面有。

之后读入之后,link时,报错 无法read sc_max.db ,一开始以为是vhdl和verilog不一样呢。 后来才发现 search_path路径写错了,dc找不到这个文件根本。

其实应该在dc invoke的时候就报出来了,没仔细看。

之后读入vhdl、设置current-design、link、check_design、保存一个ddc文件,进行compile,再保存一个ddc。exit退出。

新增实验: 设计一个带有module例化的多层级top,完成对其的dc综合。

复盘:

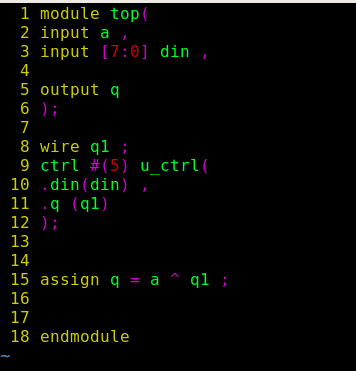

随便写了一个module,需要例化参数的。然后读入 verilog时候,没有报错,执行link时候,报出了如下:

后来看到 student guide 关于analyze的介绍才知道, analyse是唯一的读入带parameter参数的途径。所以以后都得用analyze这个命令了

使用之后,生成了一堆的中间文件,把cwd目录弄得很乱。

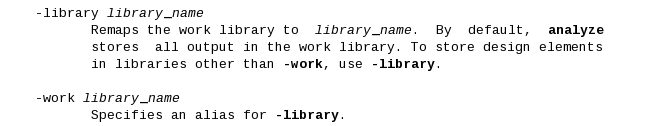

我们先查下analyze的help文档:

我们先挑这4个。

-work : 是为WORK重新制定一个路径,存放中间文件。

-library librname 没看懂。。。。

-define 是为了预编译准备的。

来实验下:

在cwd上新建了一个jjj的目录里面存放了临时文件。

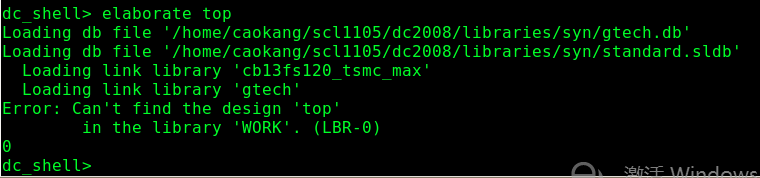

接下来: elaborate top ,既然报错了。

说是 在WORK里面找不到 top。 因为我们重新制定了WORK,所以没有WORK。

我们需要为elaborate指定路径,好,看下图:

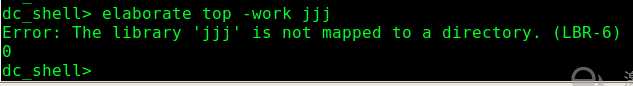

居然报错了,为什么呢? 它好像是说 jjj不是一个路径, 可是jjj明明是一个路径啊.

再看下elaborate的man手册。发现 -library 后面跟的是library_name 我们的jjj只是一个路径,并不是library_name、恰好重名了.

这是因为在没有为一个lib_name指定路径前,默认新建一个name路径,但是两个还没有进行关联。

elaborate的man手册如下图:

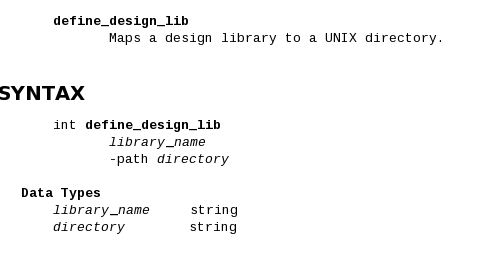

我们得想办法给 路径赋值一个name,这样或许就行了。可以使用define_design_lib命令,语法如下:

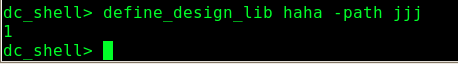

我们给路径jjj,定义一个名字叫haha

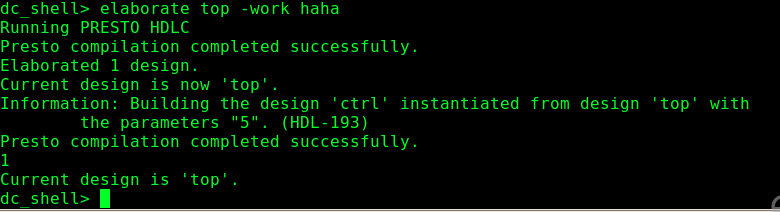

然后我们进行我们再去 elaborate,结果如下图:好像成功了。

最后再综合,保存netlist.v 得到结果:

补充: 想了想, -library的意义. 我们应该先define_design_lib hahaha jjj 即定义了一个hahaha的library_name ,它的路径是 jjj

analyze -library hahaha 其实是想说临时文件不放大work里面了。放到名字叫hahaha的 library_name里面,因为为其指定了

一个路径jjj,自然就放到jjj里面了.

elaborate -library hahaha 表示从名字叫hahaha里面找top。因为我们为hahaha指定了路径jjj。故它会其jjj里面找,就能找到了。

实验了下,可以成功,

所以总结下:

define_design_lib name + 路径: 给路径起一个名字name。

analyze 不指定 -library -work时,默认把临时文件存在WORK下面, 而WORK的默认路径是CWD

-library + name : 把临时文件存在name 所指定的路径下面.

-work+ name : 给WORK起一个新的name .

elaborate -work| -library name 都是去从name 所对应的路径去找,