其实在FPGA的开发中理想情况下FPGA之间的数据要通过寄存器输入、输出,这样才能使得延时最小,从而更容易满足建立时间要求。我们在FPGA内部硬件结构中得知,IOB内是有寄存器的,且IOB内的寄存器比FPGA内部的寄存器更靠近外部的输出管脚,这样就能够得到更小的延时,从而使时序更好。我们可以看到在没有指定的情况下寄存器的映射都是随机的,那么问题来了,如何才能指定寄存器映射到IOB中呢?我们依然用异步复位D触发器的例子来给大家演示。

如图1所示,我们回到工程界面点击“Assignment Editor”图标来约束寄存器映射的位置。

图 1

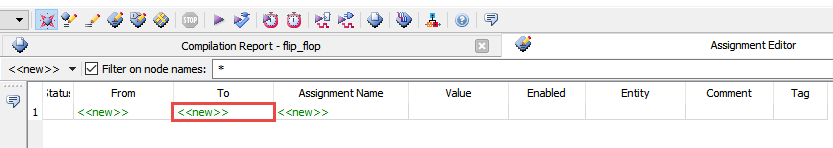

如图2所示,在打开的“Assignment Editor”界面中点击“To”下面的“<<new>>”添加要约束的项。

图 2

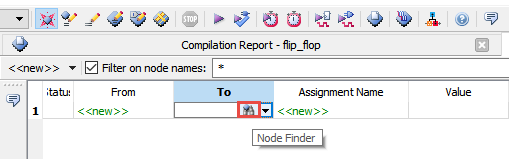

点击如图3所示的望远镜图标,打开“Node Finder”。

图 3

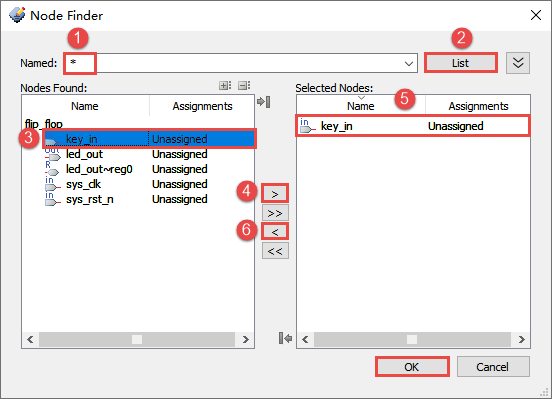

在打开的“Node Finder”界面中我们找到信号的输入key_in,如图4所示,根据序号顺序,在①处的“Named :”选项框中输入“*”,点击 ②处的“List”,在③处的“Node Found :”列表中就会列出名为key_in 的信号,双击③处的key_in 信号或点击图标④,key_in 信号就被添加到⑤处的“Selected Nodes:”中了。如果我们想取消⑤处选择的信号则在“Selected Nodes:”选中该信号后点击图标⑥即可。设置完毕后点击“OK”退出。

图 4

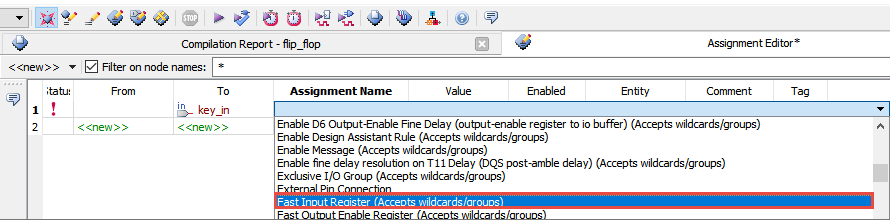

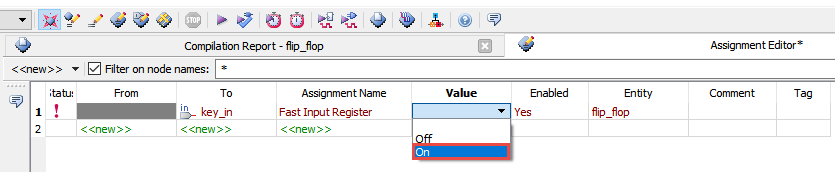

如图5所示,设置“Assignment Name”,下拉列表找到“Fast Input Register(Accepts wildcards/groups)”,这是设置将寄存器映射在输入IOB中的约束,如果设置将寄存器映射在输出IOB中则选择“Fast Output Register(Accepts wildcards/groups)”。

图 5

如图7所示,设置“Value”的值为“on”。

图 6

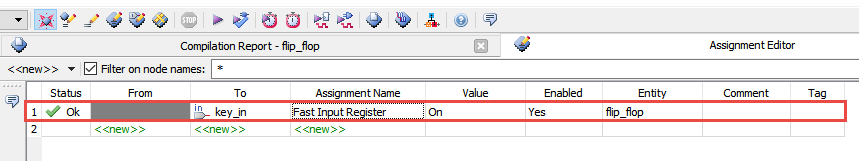

全部设置完成后的结果如图 22-90所示。

图 7

点击“Start Compilation”图标全编译进行布局布线,否则无法重新映射资源。此时会弹出如图8所示的对话框,提示是否要保存更改,选择“Yes”后会执行布局布线。

图 8

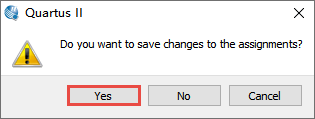

当布局布线重新完成映射后我们再来看看Chip Planner视图,如图9所示,我们发现整个视图都没有什么明显的变化,难道是映射失败了?

图 9

如图10所示,既然不能用肉眼直接看到,那我们可以在Chip Planner界面右上角红色框处的“Find what”处搜索定位信号在版图模型中的位置,如果没有找到“Find what”搜索框,按住键盘“Ctrl + F”就会自动出现。

图 10

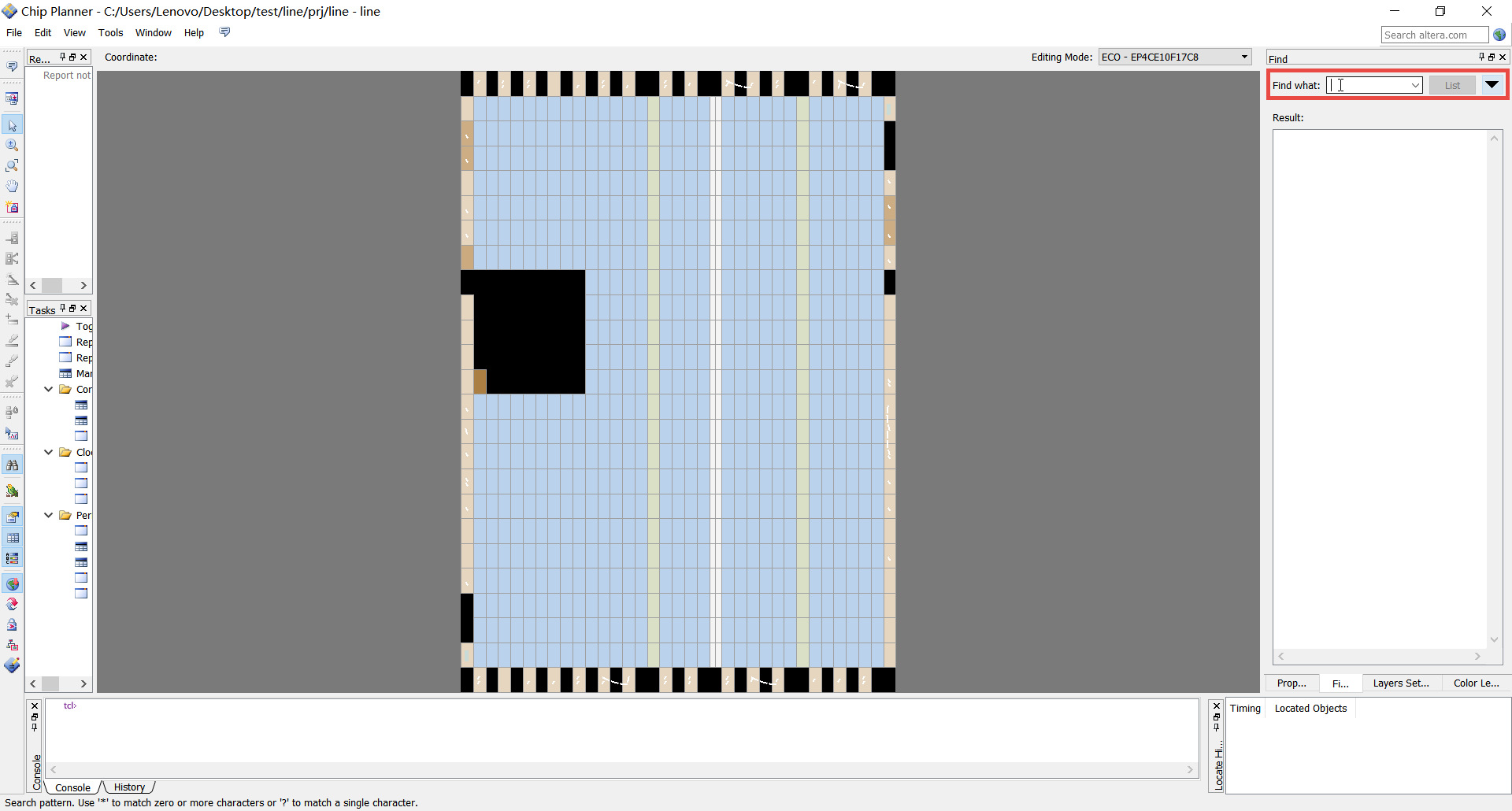

在图11中红色区域中的“Find what”搜索RTL代码中的信号名“key_in”,然后点击“List”。

图 11

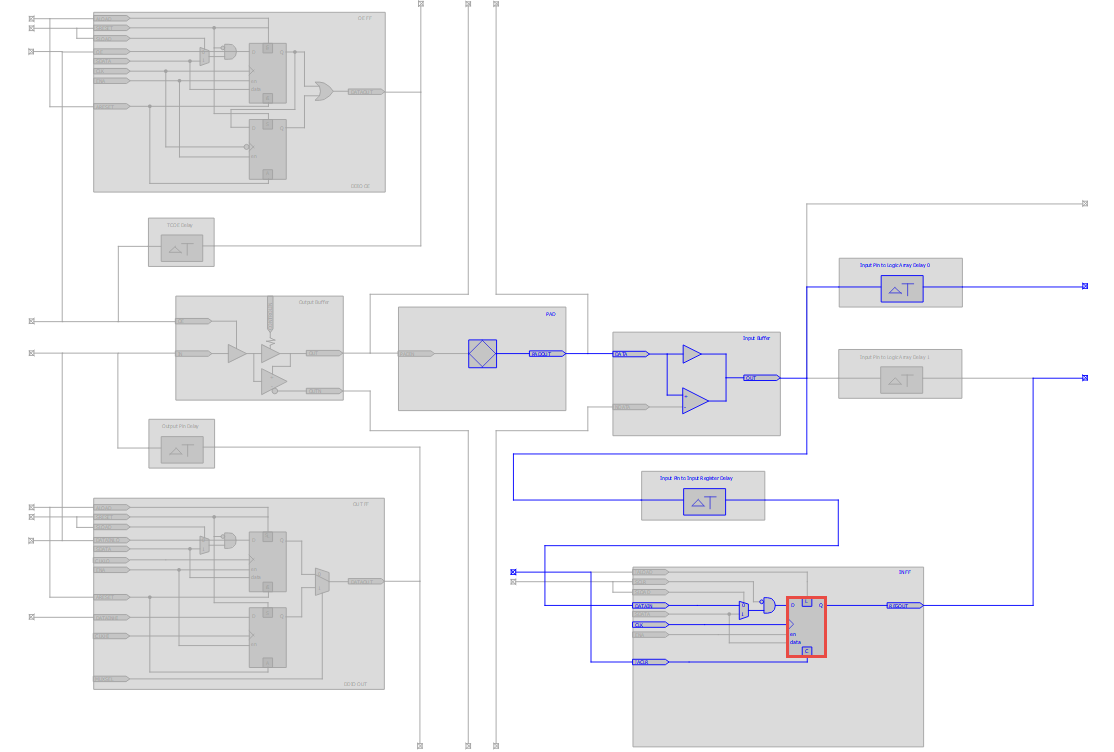

点击图12所示的“key_in”可以看到在版图模型的对应位置高亮显示,这个位置就是FPGA的IOB区域。

图 12

如图13所示,将映射的IOB区域放大,其中①为我们key_in的输入端,而②则是寄存器所映射的新位置。

图 13

如图14所示,我们双击②处的寄存器,观察其内部结构,发现IOB中的寄存器已经高亮显示了,说明真的映射上了,实现了我们的要求。

图 14

欢迎加入FPGA技术学习交流群,本群致力于为广大FPGAer提供良好的学习交流环境,不定期提供各种本行业相关资料!QQ交流群号:450843130