I2S简介

如上图所示:

- SCLK :位时钟,数据单bit反转。 频率=2 * 采样频率 * 采样位宽

- LRCK :帧时钟,左右声道标志位。 频率=采样频率

- SDATA :串行音频数据BIT位。图中表示音频数据为8bit,即采样位宽=8

- sdata在sclk的下降沿变化,上升沿采集。且在lrck发生反转后的第二个上升沿采集音频数据的最高位。音频数据的最低位是lrck再次反转的第一个上升沿。

I2S详介

I2S音频总线协议

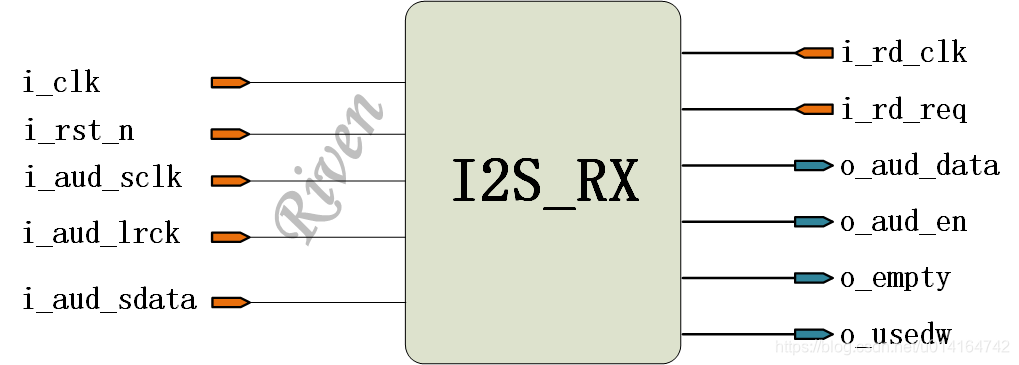

功能简介

- 将串行音频数据转成并行数据后存进FIFO,等待外部模块读取音频数据。

模块端口

接口描述

| signal_name | direction | width | description |

|---|---|---|---|

| i_clk | input | 1 | 系统时钟,频率比i_aud_sclk高偶数倍以上 |

| i_rst_n | input | 1 | 复位信号 |

| i_aud_sclk | input | 1 | I2S串行时钟 (位时钟) |

| i_aud_lrck | input | 1 | I2S左右声道数据 (帧时钟) |

| i_aud_sdata | input | 1 | I2S串行数据 |

| i_rd_req | input | 1 | 外部读取FIFO请求 |

| i_rd_clk | input | 1 | 外部读取FIFO时钟 |

| o_aud_data | output | X+1 | FIFO音频数据 |

| o_aud_en | output | 1 | FIFO音频数据有效标志 |

| o_empty | output | 1 | FIFO空标志信号 |

| o_fifo_usedw | output | 8 | FIFO内部数据个数 |

* 注:

* X为Parameter

* i_aud_lrck = 1 : Left audio || i_aud_lrck = 0 : Right audio

* o_aud_data[MSB]=1 : Left audio || o_aud_data[MSB]=0 : Right audio

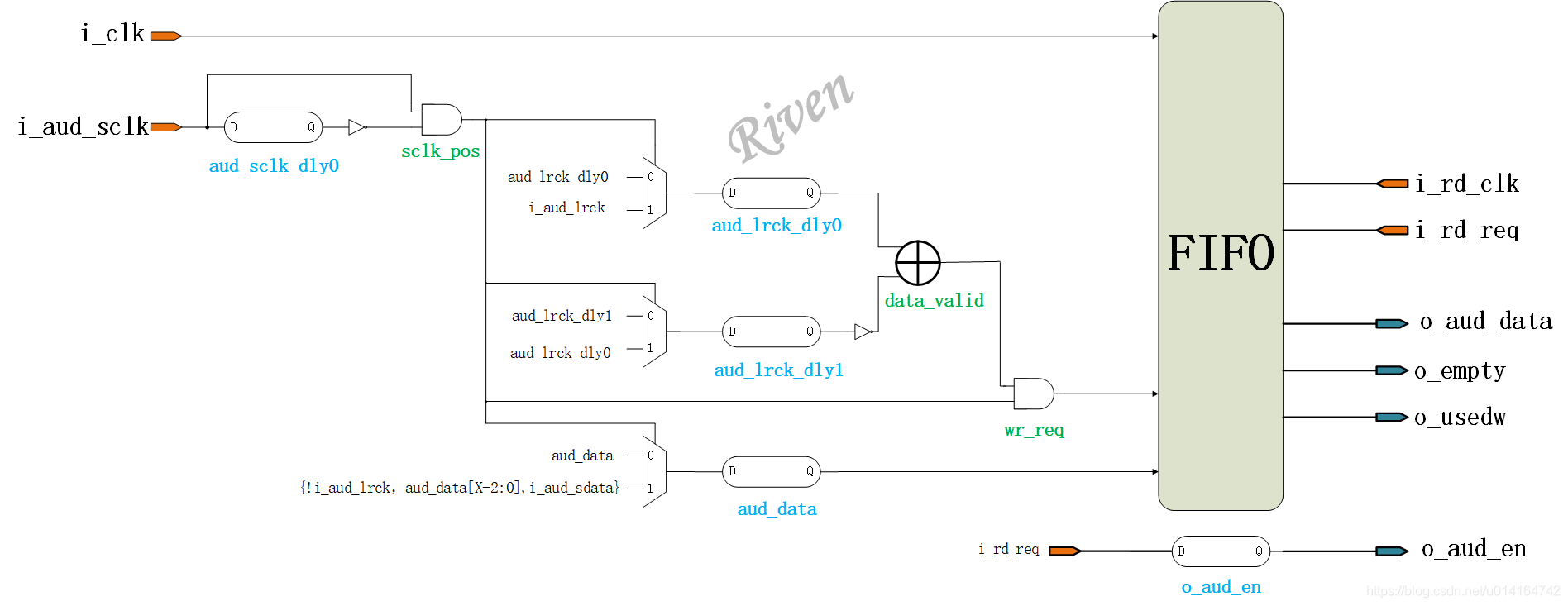

电路图描述

- 绿色代表wire型;蓝色代表reg型;⊕表示异或;

模块用途及优点

* 将I2S信号转成并行数据,以便后级模块对音频数据进行处理、存储、传输等。

* 模块化封装,将音频数据位宽设为参数,可以适用多种需求。

* 模块耗费资源少,功能完善。现拿现用,减少开发时间。

资源占用估计

| 资源 | 类型 | 个数 | 用途 |

|---|---|---|---|

| 寄存器 | 1bit | 4 | 读取控制信号 |

| 寄存器 | X+1 bit | 1 | 声道标志+音频数据 |

| FIFO | 深度、位宽由参数定义 | 1 | 缓存音频数据 |

有问题联系可以我,一起讨论。