Design-for-Testability(DFT)的基本知识点

基础知识

1. CP和FT

-

CP是(ChipProbe)的缩写,指的是芯片在wafer(晶圆)的阶段,就通过探针卡扎到芯片管脚上对芯片进行性能及功能测试,有时候这道工序也被称WS(WaferSort)

-

FT是Final Test的缩写,指的是芯片在封装完成以后进行的最终测试,只有通过测试的芯片才会被出货,详尽的测试。

参考https://blog.csdn.net/lzwsdu/article/details/53502894:

什么情况下需要CP?

-

因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的.而CP阶段则是可选

-

CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目.凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测.一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作.在FT阶段再确认具体的SNR/THD等指标

-

由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选.精细严格的测试放到FT阶段

-

如果封装成本不大,且芯片本身良率已经比较高.可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺

-

新的产品导入量产,应该先完成FT测试程序的开发核导入.在产品量产初期,FT远远比CP重要.等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试

2. 测试工程师需要考虑什么

降低测试成本:

- 从测试规划开始考虑芯片性能要求,ATE,Load Board等,通过减少chain length, memory instance number 来降低成本

- ATPG effciency

- 选择合适的test vectors

3. 什么是DFT

DFT = Design-for-Testability

-

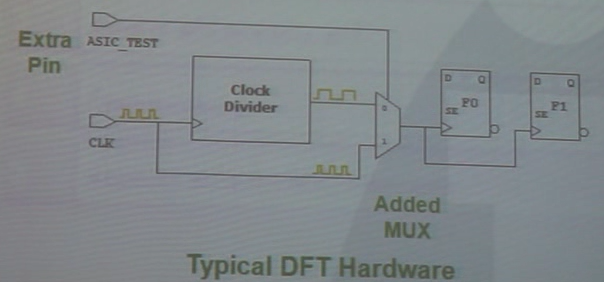

额外的pin

-

会插入或改变原有的逻辑

DFT cost:

- area cost

- performance 降低

- ATPG tool cost 和 pattern debug cost

- ATE testing cost

如何减小DFT cost:

- 合理的test plan, 比如减小chain length, memory concurrent testing

- 减少图形(pattern) 数量

- 增加测试频率

Fault Model

physical fault:

- IO leakage 或 short

- net open

- material pollution

Logic fault:

- signal hard fault

- delay fault

- static current fault

Fault model 就是在physical fault 和 Logic fault之间建立一个桥梁,或者说是一个反应物理fault影响的逻辑模型

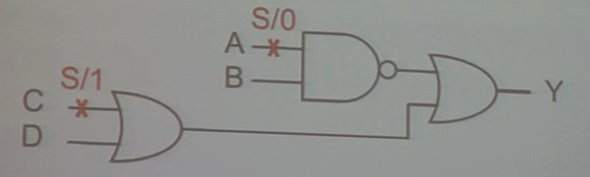

比如下面一个SA fault (static fault):

A pin可能在物理上被短路到了地,因此在建模时相当于将其置为静态的0.

Transition fault: 主要考察speed和timing

- STR: slow to rise

- STF: slow to fall

Path delay fault: 也是反应在速度和时序上,考察整个路径上的延时是否超时,通常是关键路径

IDDQ: 测试CMOS电路在静态时的总电流。

- 在静态时CMOS只有leakage电流或二极管反向电流

- 任何开路,短路都会导致总电流异于常规,导致IDDQ variation

Fault class hierarchy

- DT - Detected

- PT - Possibly detected

- UD - Undetectable

- AU - ATPG untestable

- ND - Not detected

DFT Methods

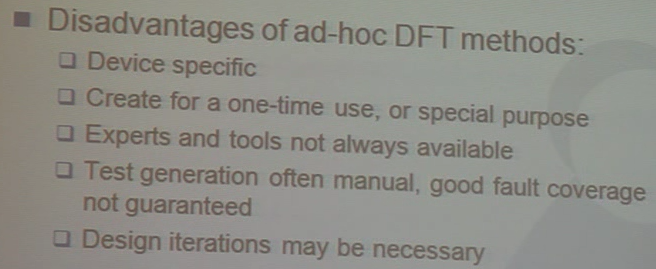

- Ad-hoc (功能点测试)

- Structured (结构化测试):

- Scan

- Built-in self-test (BIST)

- Memory

- Logic

- Boundary scan

Ad-hoc

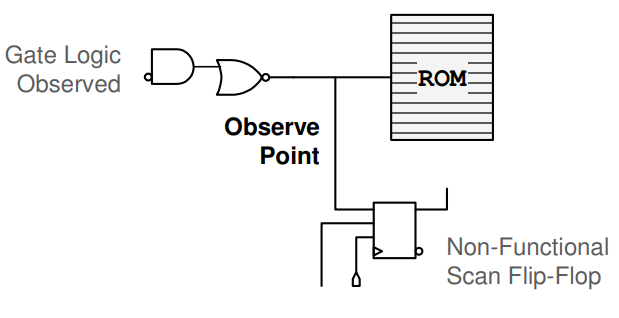

在设计者关注的地方增加可测试逻辑:

- 增加可控制节点和观测节点

- 将大的电路分解为小的测试blocks

例如在下面的ROM前增加一个scan点可以观察进入ROM的数据是否有误。

缺点:

Scan:

将DFF换成带扫描模式的DFF,并将其串起来形成scan chain

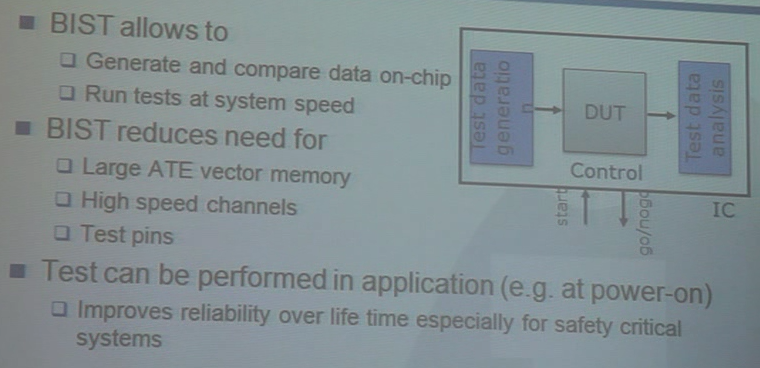

逻辑BIST

BIST = Build in self test

将ATE(自动测试机)的工作(Test data generation, test response evaluation) 放到片上。

另外,可以保护系统的内部数据,因为少了外面的控制和观测,所以对内部节点的信息不可获取。

缺点:

- 开销大

- 较低的fault coverage,较高的测试时间

- Debug 困难,只知道错了,但不知道错在哪

常用于对pin数量要求不大(pin比较少),有安全问题的芯片,例如:公交卡芯片

Boundary Scan

测试多芯片互联。测试板级制造过程的错误,包括使用了错误的元件,pin的错误短路、开路等

- 有独立的子系统(独立时钟)

- 只需要5个pin: TDI, TDO, TMS, TCK, TRST(可以不用) (JTAG)

- 通过将多片的TDO和TDI串联可以测试多片的互联

基本JTAG:

例如,通过TAP模式选择,检测device的身份验证,验证是否时正确的芯片。

DFT-Scan

D算法:

- 选择一个特定的fault point(猜测的有fault的地方)

- 输入驱动值,保证其值到达fault point时产生的理论值跟fault相反

- 传播fault值到最近的输出点

- 记录测试图形,报fault

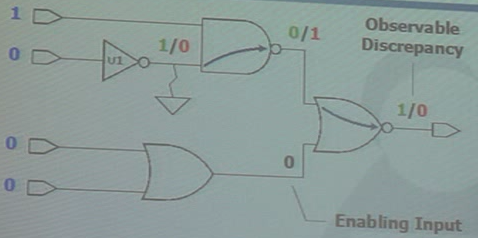

例子:下面的U1单元输出怀疑有static fault(接地短路)

- 首先在U1的输入上给0,如果U1没问题,则输出应该时1(绿色,表示无fault), 否则,输出0(红色,表示static 0 fault)

- 其他pin的输入需要做配合,使得最后的输出pin能够反应U1的值,这样U1的fault就被挪到了输出pin上,判断输出值即可判断U1是否有问题

对于这个例子,有如下几个概念:

- Input Stimulus: 测试激励,这边指 1000

- Expected response: 预期响应,这边指没有fault时的输出值,为1

- Test Vector: 测试向量,即上面两个合在一起10001

- Test pattern:测试图形,为了检测一个目标fault而构建的一个或多个测试向量序列

实际上,我们并不知道U1是否有问题,就算最后输出报了fault,也无法确定是不是U1出错。所以实际上做的时候会迭代多次,根据不同的测试激励逐渐缩小fault点范围,直到排查到fault点。

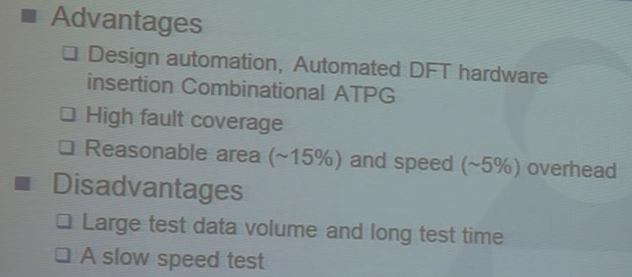

D-算法的优缺点:

- 优点:

- Deterministic: 确定的,是一步接一步做的

- Exhaustive: 穷举的,直到测完或者有undetectable的fault

- 缺点:

- 一次只能测一个fault

- 在每一步都要进行决策

- 对于一些难以检测的fault可能要多次迭代测试

注意:有些fault点是测不到的,比如冗余逻辑。

练习:

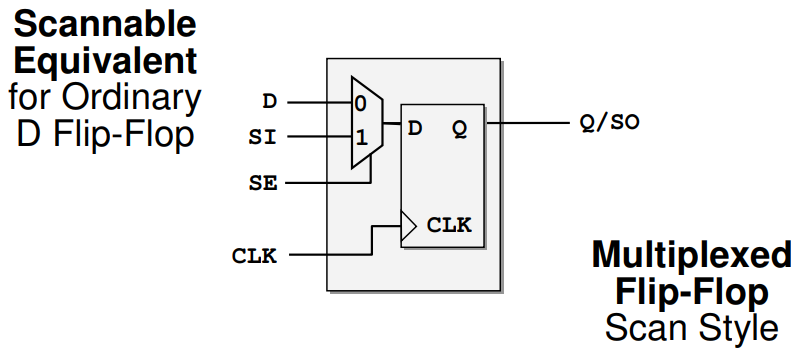

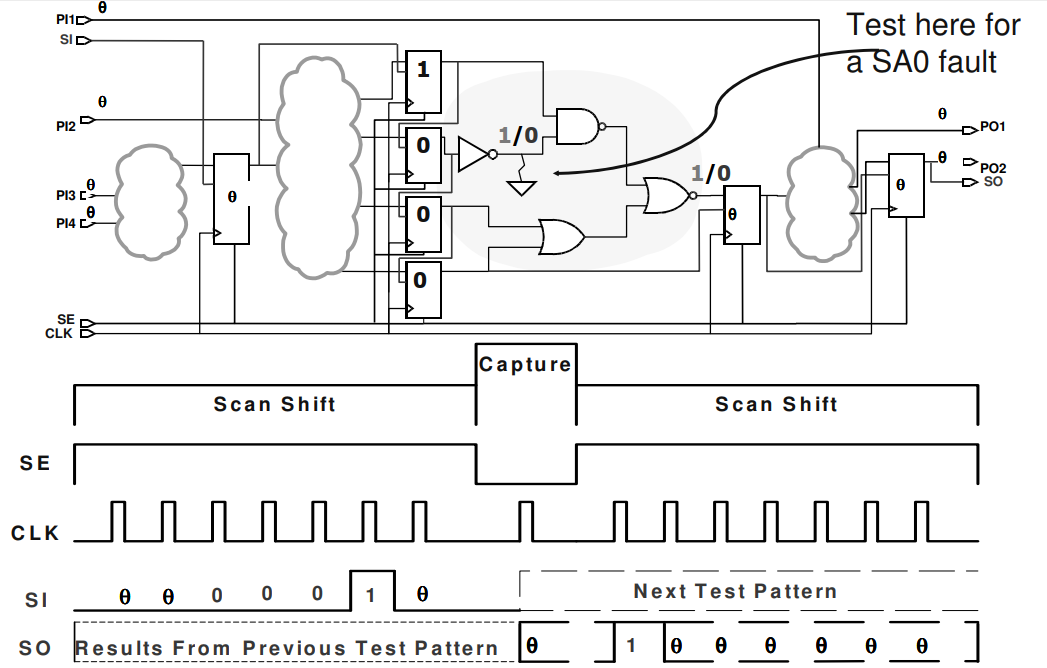

Scannable Equivalent Filp-Flop

上面的方法是测组合逻辑,而要测时序逻辑,则需要将DFF进行替换:

之后将所有替换后的DFF串起来形成一条链。

目的:方便将测试激励灌到任意DFF中。

方法:

- SE选中SI端,经过scan shift将测试激励通过SI端移到寄存器中

- SE选中D端,让寄存器Capture数据

- SE选中SI端,继续shift,将待测点结果输出到output pin

- 继续Capture ...

例子:

可以看到,要测标记点的fault,需要给1000的测试激励,首先通过SI端将数据依次打入对应寄存器,之后capture fault结果,然后继续shift,此时经过若干周期就能将所有DFF的capture值从PO导出来,就可以判断fault结果了。

ATPG

自动测试图形(pattern)生成。芯片测试需要有pattern, 手工设计pattern是非常耗时的。主要Tools: Teramax, Testkcompress, Encouter Test.

ATPG flow:

- Read design

- Build design

- DRC

- Prepare for ATPG

- Run ATPG

- Save patterns and faults

Memory 在测试的时候是交给BIST来做的,是一个black box,但是这样在Memory block的附近可观测性很低,如何解决?

- 加bypass逻辑,(mem输入到输出加DFF)

- 使用TetraMax Model (为memory建模)

MBIST

为什么要做MBIST?

-

Memory在现在芯片中占比越来越大。(80%-90% Today)

-

mem对工艺波动非常敏感

-

目前很多嵌入的mem都有内置的redundancy(冗余逻辑),可以替换一些失效的mem区域,而失效区域需要BIST来检测到

Memory类型

- SRAM

- DRAM

- CAM

- ROM

- FLASH

MBIST一般只针对SRAM, DRAM, ROM

Memory Defects

- 地址解码逻辑

- 读写控制逻辑

- memory cell

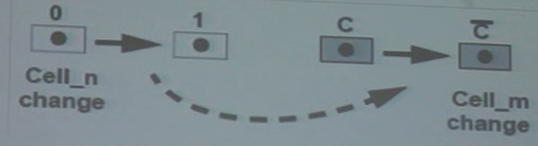

同样,memory 的fault也有stuck-at fault(钳位在固定电平) 和transition fault。此外,mem还有Coupling Fault:

Coupling Fault:

-

Inversion Coupling Faults(CFin)

-

一个cell上的跳变导致另一个cell往反方向跳变

-

-

-

Idempotent Coupling Faults

- 跟上面类似,只是导致另一个cell往固定值跳变

-

Bridge Coupling Faults (BF)

- 在内部cell之间存在桥接,效果是看上去两个cell相或,相与

-

Neighborhood Pattern Sensitive faults

MBIST 算法

- Address Decoder Algorithm

- March Algorithm

- Checkerboard Algorithm

MBIST 的基本架构