https://blog.csdn.net/vivid117/article/details/100653875

1.奇偶校验电路

奇偶校验码

奇偶校验码是比较简单的数据校验码,可以检测出一位错误,但是并不能确定错误的位置。

如果数据中发生多位数据错误就可能检测不出来,更检测不到错误发生在哪一位;

实现方法

将有效信息位和校验位读入,判断1 的个数为奇数还是偶数个,在奇校验时,正常的情况下个数应该为奇数个,偶校验正常情况下应该时偶数个。

校验码的生成:对于奇校验,判断有效信息的位1的个数,若为偶数,则校验位为1,奇数则校验位为0;偶校验则相反。

用Verilog设计8bit奇偶校验电路。

奇偶校验电路,一般多用于UART中接受数据位的校验等。

通信中发送一个字节的数据,8位,加上一个校验位,一共九位。

如果是奇校验,8位中1的个数加上,校验位为1的情况,最终1的个数为奇数个。

如果是偶校验,8位中1的个数加上,校验位为1的情况,最终1的个数为偶数个。

module Odd_Even_Check(

input [7:0] indata,

output odd_bit,

output even_bit

);

assign even_bit = ^indata; //偶校验位是所有数据为按位异或得到

assign odd_bit = ~even_bit;

endmodule

实现奇偶检验的算法就是,如果是偶校验,只要将该8位数据第一位和第二位进行异或,然后将得到的结果和第三位异或,依次下去,直到和第七位异或,

这样得到的最后结果,就是偶校验位;如果是奇校验,将上面的偶校验位取反即可。

2.数据比较器

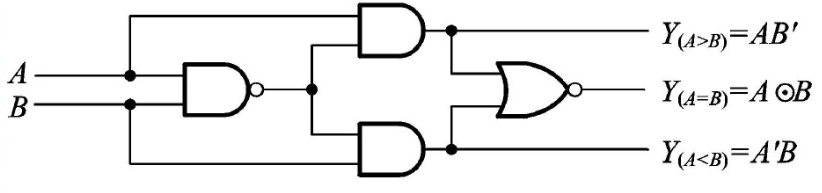

一位数值比较器

当A>B,则Y= AB’ = 1

当A<B,则Y= A’B= 1

当A=B,则Y= AB’ + A’B = 1

下面即为一位数值比较器的电路:

多位数值比较器

多位数据进行比较时,必须从高位进行比较,并且高位相等时才能比较下一位。

下图是74LS85逻辑框图。

————————————————

版权声明:本文为CSDN博主「摆渡沧桑」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/vivid117/article/details/100653875