1 RISC与RISC-V

RISC发明者是美国加州大学伯克利分校教师David Patterson,RISC-V(拼做risk-five)是第五代精简指令集,也是由David Patterson指导的项目。

1.1 为什么要做RISC-V指令集?

历史上是这样的,2010年伯克利大学并行计算实验室(Par Lab) 的1位教授和2个研究生(下图这三位大佬)想要做一个项目,需要选一种计算机架构来做。当时面临的的是选择X86、ARM,还是其他指令集,不管选择哪个都或多或少有些问题,比如授权费价格高昂,不能开源,不能扩展更改等等。所以他们在2010年5月开始规划自己做一个新的、开源的指令集,就是RISC-V。

接着时间到2015年,这个指令集在学术界已经开始出名了,这时为了更好的推动这个指令集在技术和商业上的发展,3位创始人大佬做了下面两件事情。

技术方向,成立RISC-V基金会,维护指令集架构的完整性和非碎片化。

商业方向,成立SiFive公司,推动RISC-V的商业化。

1.2 硬件构建语言Chisel

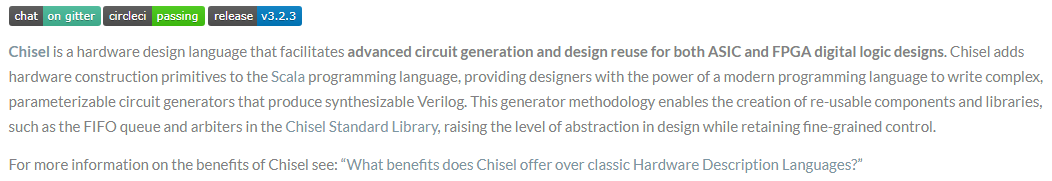

除了开发RISC-V指令集,大佬们还同步开发了用于RISC-V处理器设计的Chisel语言(Constructing Hardware in a Scala Embedded Language,硬件构建语言)。

注意不是硬件描述语言(Hardware Description Language,HDL)。

我们知道,数字电路设计一般使用verilog(HDL)语言进行开发。那么Chisel是什么呢,为什么可以用它来做处理器?

https://www.chisel-lang.org/index.html

参考这个链接大概了解了一下,Chisel是一种硬件设计语言,开发的目的是为了促进ASIC和FPGA高级电路生成和设计重用。Chisel是用Scala语言写的一个针对硬件开发的库(有点类似于uvm和SystemVeriolg的关系)。开发人员可以使用Chisel编写可以生成可综合、可参数化的verilog电路生成器。Chisel首先生成通用的verilog,然后使用的DC进行综合。其实设计Chisel并不是用来替代verilog的,而是为了在硬件设计中引入敏捷开发的思想解决硬件设计反馈环太长这件事情的。[3][5]

Rocket-Chip-Generator项目是SiFive的第一个RISC-V的开源处理器,使用Chisel编写。

关于基金会目前的开源的RISC-V Core和SoC开发语言状况,可参考基金会Github,

https://github.com/riscv/riscv-cores-list

2 RISC-V基金会

RISC-V Fundation Community,RISC-V基金会。

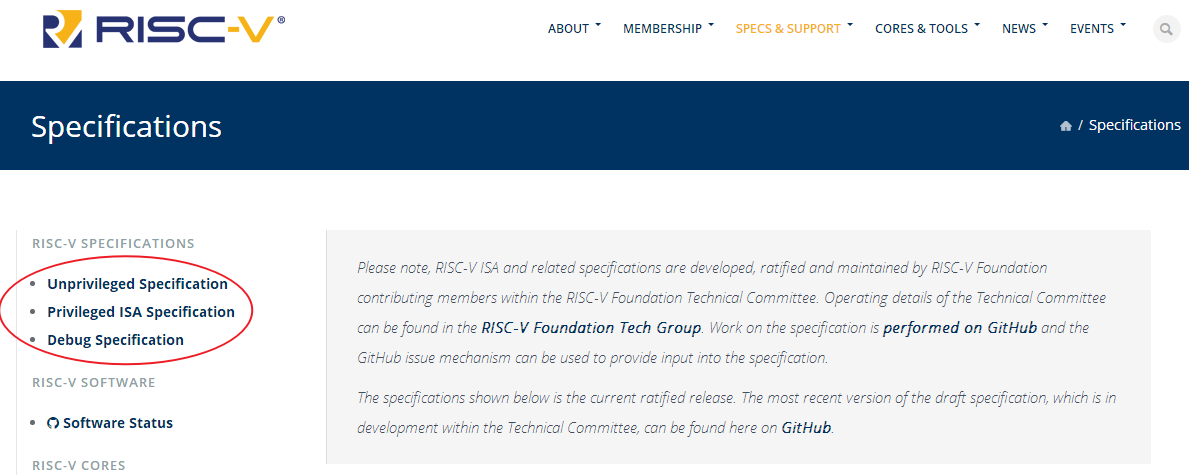

2.1 基金会成立

2015年,3名RISC-V发明者创办SiFive公司,SiFive联合以google为首的公司作为创始会员创立RISC-V基金会。并将RISC-V指令集所有相关的资料都交给非盈利性的RISC-V基金会来处理。并将之前所做的CPU及SOC的实现的积累都开放源代码,就是上面提到的Rocket-Chip-Generator。RISC-V基金会目前已经吸引了全球33个国家超过325个组织加入,包括西部数据,三星,Microchip,NXP,Google等国际大厂。基金会负责维护RISC-V指令集标准手册(riscv-spec.pdf)和架构文档(riscv-privileged.pdf),对应Spec文档可从官网下载,如下图

2.2 基金会会员细则

RISC-V基金会由五个等级会员组成,包括Platinum(白金会员)、Gold(金牌会员)、Silver(银牌会员)、Auditor(审核员)和Individual(个人会员)。就像我们办会员卡一样,前三种会员每年需要向基金会缴纳一定的费用,费用从$5000~25000不等,当然其各自的权利也相对高一些。如下截图列举了会员协议和章程,

https://riscv.org/membership-application/

细则说明了基金会成员为维护和发展RISC-V指令集架构所需要遵循的治理方法和贡献原则,所有成员都有资格参加基金会任务组,并对RISC-V指令集的维护做出贡献。

白金会员,会员费用$2.5w/年,10次RISC-V研讨会折扣注册权限。会员有资格参加董事会席位选举,并担任基金会技术委员会、营销委员会和工作小组成员。

金牌会员,会员费用$1w/年,7次RISC-V研讨会折扣注册权限。会员有资格担任基金会技术委员会、营销委员会和工作小组成员。

银牌会员,会员费用$0.5w/年,5次RISC-V研讨会折扣注册权限,会有在董事会选举中每个公开职位都有一票表决权。

审核员会员,不收取会员费,全年研讨会的折扣注册,主要针对非盈利性研究室和大学。

个人会员,不收取会员费,无投票权,适用于特定公司或组织无关的个人贡献者。

审核员和个人会员不得将RISC-V知识产权用于商业目的,付费会员才有商业化使用的资格。

2.3 国内加入基金会企业

大概看了一下,目前国内企业和机构在基金会中占比不大(之前看到资料说大概25家),其中,

Platinum Level有阿里巴巴、华米科技、中兴微(Sanechips)、晶芯科技(Andes)等;

Gold Level华为、浪潮(Inspur)、乐鑫(Espressif)、芯原微(VeriSilicon)等;

Silver Level有芯来科技(Nuclei)、紫光同创(Pango)、全志(Allwinner)、君正(Ingenic)、兆易创新(GigaDevice)、比特大陆(Bitmian)等。

具体哪些公司是哪种会员可参加官网https://riscv.org/members-at-a-glance/。

基金会除了维护技术规范的文档外,还负责组织RISC-V会议和讨论。

2019.11.26,由于担心美国的贸易限制,RISC-V基金会总部从美国迁往瑞士。

3 SiFive公司

SiFive是2015年7月由RISC-V发明者创立的用于推动RISC-V商业化的公司。SiFive是SaaS(Software-as-a-Service)服务商,提供基于RISC-V指令集架构的商业化处理器IP、开发工具和芯片解决方案。2018年8月在中国注册独立公司赛昉科技(SaiFan)用于为国内客户提供服务。

3.1 商业化动作-开发板

SiFive商业化做了2重要的事情,即提供2块HiFive开发板给全世界的开发者用户,这两块开发板很大的推动了RISC-V生态的建设。

https://www.sifive-china.com/site/HiFive1

3.2 SiFive提供的IP产品

我们知道,ARM Cortex分为3个系列,即M,R和A,分别是针对应用嵌入式(Microcontroller)、实时(Real-Time)和操作系统(Application)3个领域,分别对应Cortex-M、Cortex-R、Cortex-A 3个系列。SiFive提供的RISC-V IP对标的也做了3个系列内核,如下,

E核,32位嵌入式内核,用于边缘计算,AI和物联网方向,对标ARM Cortex-M系列;

S核,64位嵌入式内核,用于存储、AR/VR、机器,对标ARM Cortex-R系列;

U核,64位应用处理器,用于数据中心、网络基带等方向,对标ARM Cortex-A系列;

每种类型的内核又按照数字标号从低端到高端做了不同种类,2系列,3/5系列(看来大家都会默认跳过4这个编号),7系列,对标Cortex A、R、M编号从低到高可用于不同的场景。可以说是从横向和纵向都对标了ARM系列。

3.3 题外话

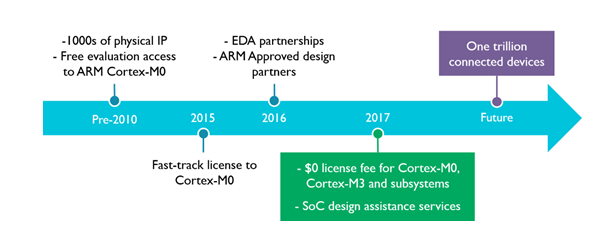

我们看到目前RISC-V可以做到全系列的对标ARM,但是从市场角度来说,RISC-V还是有很多事情要做的。2017年6月20日,ARM宣布Cortex-M0/M3处理器内核不在需要授权费用(版权费用仍需支付),免费的目标是为了实现一万亿的出货量。[9]

也就是说低端的M0和M3系列用户可以直接拿来IP先做集成使用,所以RISC-V在低端场景下是否有价格优势是存疑的。RISC-V要做到有价格优势,应该往高性能的发展,毕竟ARM高性能的授权费是很高的。

另一个就是生态建设,ARM经过这么多年的发展,生态是相当成熟的,包括软件、编译器、APP、参考设计等。我们知道消费类产品开发是很追求实效的,如果你晚了一步上市,可能就会差很多了。从这方面来说,大家可能会更愿意选择成熟的ARM,毕竟没有学习成本。但是反观RISC-V,可能还或多或少有一些欠缺,所以RISC-V需要把生态链快速推起来。当然也不必过分悲观,如果RISC-V快速将生态链建立起来,并且做得更有价格优势的话,自然会有很多人愿意选的。

还有就是高端场景,RISC-V目前没有拳头产品。大家如果要做一些高端的处理器,很自然的都会去选择x86或者ARM架构(年前找工作面试看到的现象。)不同架构现在在国内都有典型的代表,如X86代表有兆芯、海光、北大众志、澜起(Intel、清华、澜起联手研发可重构计算模块和Intel x86架构技术的新型通用CPU,2016)。ARM代表有海思、展锐等,MIPS有龙芯和君正,Alpha有申威。需要有RISC-V的领头企业。详细见下节国内状态。

4 RISC-V国内状态

主要介绍RISC-V IP和芯片厂商及相关联盟。

4.1 RISC-V IP和芯片厂商

前面提到x86,ARM,MIPS、Alpha指令集在国内都有典型代表。那RISC-V是什么样的一个情况呢?

RISC-V芯片爆品不断,遍地开花的一个情况,如下列举部分厂商的RISC-V芯片和IP的公司。

4.1.1 RISC-V IP Core厂商和产品

芯来科技,类似SiFive,提供3个级别x 4个系列RISC-V IP(900系列开发中)。

晶心科技,AndeStar™ V5架构= RISC-V + 晶心扩充架构,支持32位与64位处理器,N25及NX25非常适合网络、储存及人工智能(AI)等需高速控制的各种应用。

芯启科技,SAR-T6系列、SAR-D9系列和TNA-300系列。

SAR-T6系列对标ARM Cortex-M4,面向AIoT终端、传感器、机电MCU、轻量级智能以及众核智能应用;

SAR-D9系列对标ARM Cortex-A9,面向医疗、通讯、工控、机电MCU、视频音频处理、轻量级智能、通用算法加速场景;

TNA-300对标英伟达的开源神经网络加速器NVDLA,面向设备端AI方案。

阿里平头哥,玄铁910 IP Core,最高支持16核,2.5GHz,单核性能可达7.1 Coremark/MHz,玄铁910与ARM v8的高性能处理器Cortex-A72,处于同一水平。应用领域主要是5G、自动驾驶、人工智能等高端领域。

https://www.cnblogs.com/whik/p/11258546.html

4.1.2 RISC-V芯片公司和产品(部分)

紫光展锐,春藤5882,该芯片支持蓝牙5.0,用于TWS蓝牙耳机方向;

兆易创新,GD32VF103,32位通用MCU;

嘉楠,勘智K210,边缘计算AI芯片;

华米科技,黄山一号,可穿戴设备、运动健康手环;

格兰仕,BF-细滘,联合SiFive China开发,用于物联网、智能家居产品;

优微科技,UPD350系列,USB PD 3.0控制器;

时擎科技,AIoT、边缘计算;

核芯互联,璇玑CLE系列,通用嵌入式MCU处理器,用于家电、工业控制、物联网等领域;

中科物栖,JX1和JX2,实时嵌入式设备,可替代现有ARM Cortex-M系列核心;

中科蓝汛,蓝牙,TWS方向;

汇顶科技,GM2656,微控制器,指纹和安全算法;

4.2 RISC-V相关联盟

4.2.1 中国开放指令生态联盟

2018.11.8,浙江乌镇第五届互联网大会,中国开放指令生态联盟(China RISC-V Alliance,缩写CRVA)正式成立。联盟由中国工程院院士、中科院计算技术研究所研究员倪光南任理事长,阿里-中天微、百度、北京大学、长虹集团、清华大学、腾讯、中芯国际、紫光展锐等为副理事长单位,中国电子信息产业发展研究院为常务副理事长单位,计算所研究员包云岗任秘书长。组织架构如下图:

来源:http://crva.ict.ac.cn/?page_id=44

联盟制定了一个“三步走”的计划,希望用10年左右的时间,到2030年逐步完成RISC-V开源芯片生态的建立,主要包括,

● 第一步,为开源社区提供经过流片验证的高质量RISC-V开源核及SoC芯片设计方案;

● 第二步,逐步构建一套基于开源工具链、开源IP、开源工艺库的SoC芯片设计流程,为企业提供商业版工具与IP之外的开源方案;

● 第三步,迭代优化开源工具,提高设计验证效率,为大批科研机构、中小企业提供定制芯片服务,降低芯片开发门槛。

4.2.2 中国RISC-V产业联盟

中国RISC-V产业联盟(China RISC-V Industry Consortium,CRVIC),2018.10.17 成立。

中国RISC-V产业联盟由国内外RISC-V领域重点企业、研究机构、和行业协会发起成立,芯原控股公司担任联盟首任理事长单位,目前已有五十余家RISC-V领域相关企业以及十余家大学和研究机构加入。

联盟将秉承开放、合作、平等、互利的原则,致力于解决中国RISC-V领域共同面对的关键问题,建立中国国产自主、可控、安全的RISC-V异构计算平台,促进形成贯穿IP 核、芯片、软件、系统、应用等环节的RISC-V 产业生态链。

https://www.eet-china.com/news/201810180904.html

大概就先写这么多,关于RISC-V指令集的详细内容下次分享,以上。

5 参考

[1] RISC-V官网

[2] Chisel语言

https://www.chisel-lang.org/index.html

[3] Chisel引领敏捷硬件开发浪潮(矽说公众号)

https://mp.weixin.qq.com/s/FYOv7otrbY0n0h9LZ_wOeQ

[4] 错过这个点,中国芯要再落后十年?(矽说公众号)

https://mp.weixin.qq.com/s/3ae0ri9Yxyo5jYgQUXM8LQ

[5] 核芯互联CEO胡康桥:RISC-V与敏捷设计

https://mp.weixin.qq.com/s/mirlpAURnAFf2B-P3PFnkA

[6] Chisel是什么

https://mp.weixin.qq.com/s/JouEBYePvqgpPj2vKv_4jQ

[7] 狂奔的RISC-V

https://www.nucleisys.com/newsdetail.php?id=180

[8] 出书、做公众号、做网站~另类理工男的造芯之路

https://www.nucleisys.com/newsdetail.php?id=179

[9] 特大好消息,ARM Cortex-M0/M3免收授权费了

https://www.sohu.com/a/151460752_467791

http://www.chinaaet.com/topic/cortex-m0/#section2

[10] RISC-V基金会Github

https://github.com/riscv/riscv-cores-list

[11] 阿里平头哥首次交货——玄铁910是个啥?是芯片吗?

https://www.cnblogs.com/whik/p/11258546.html

[12] ARM 架构、ARM7、STM32、Cortex M3之间有什么区别和联系?

https://www.zhihu.com/question/22464046/answer/21450143