配套FPGA开发板(含该设计的工程代码):https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-4676525296.4.6e8950ed57YPhv&id=17848039135

功能

采用FPGA实现正弦波、三角波、矩形波,锯齿波生成,

频率分别为100Hz~10k,实现频率步进调节;

输出信号幅度为0V~3.3V,并能步进调节;

实时显示波形类型名称、频率值

操作

看演示视频视频

文档说明

-

顶层文件

文件名:DDS_top.v

该文件为工程的顶层文件,相当于C语言中的主函数,下面的文件相当C语言中的子函数。

在FPGA中,这个文件就是顶层电路。

DDS算法模块:

32位加法器:

10位加法器:

32位寄存器:

10位寄存器:

TLC5615驱动模块:

按键消抖模块:

按键编码模块:

涉及到的电路

该设计中涉及到的硬件电路如下:

DAC电路

按键

对应的使用的按键为:

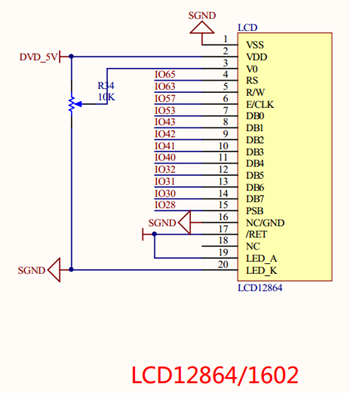

LCD1602

FPGA

电源

晶振

原理

顶层设计原理图

主要分为5个大模块:按键消抖、按键编码、dds控制、液晶显示、DAC驱动。

对按键信号进行消抖(频率控制按键、波形控制按键、幅值控制按键),然后对消抖后的按键信号进行按键编码,形成频率控制信号,波形控制信号,幅值控制信号,接着将这三中信号输入到DDS控制模块中,对dds产生波形的类型、波形的频率、波形的赋值进行控制,同时再将这三个控制信号输入到LCD1602显示模块之中,进行显示当前输出波形的类型,波形的频率,其中液晶的第一行显示波形的类型,第二行显示波形的频率。最后将DDS控制模块输出的dds波形数字信号输出到DAC驱动模块—TLC5615中,将数字信号转换为模拟信号。

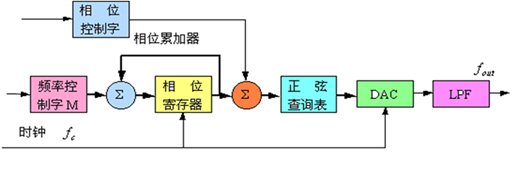

DDS原理

DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器,也可叫DDFS。

- DDS是从相位的概念直接合成所需波形的一种频率合成技术。

- 不仅可以产生不同频率的正弦波,而且可以控制波形的初始相位。

DDS原理框图

主要构成:

内部:相位累加器,正弦查找表

外围:DAC,LPF(低通滤波器)

工作过程

1、将存于ROM中的数字波形,经DAC,形成模拟量波形。

2、改变寻址的步长来改变输出信号的频率。步长即为对数字波形查表的相位增量。由累加器对相位增量进行累加,累加器的值作为查表地址。

3、DAC输出的阶梯形波形,经低通滤波,成为模拟波形。

频率控制

波形存储

正弦信号相位与幅度的对应关系

可以将正弦波波形看作一个矢量沿相位圆转动,相位圆对应正弦波一个周期的波形。波形中的每个采样点对应相位圆上的一个相位点。

相位累加器的值作为ROM的地址,读取ROM的相位幅度,实现相位到幅度的转换。

AD转换和滤波

分析:

DDS优点

- 频率分辨率高,可达2的N次。

- 频率切换速度快,可达us量级。

- 频率切换时相位连续。

- 可以产生任意波形。

DDS缺点

- 输出频带范围有限。

输出杂散大。

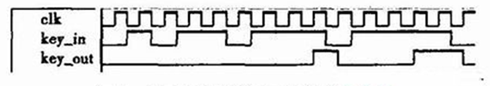

按键消抖

状态机型消抖电路

状态机型消抖电路采用有限状态机的设计方法来描述与实现,一般的状态机有S0,S1,S2三种状态,在S0状态下key_out输出为低电平,并以clk时钟信号的频率采样按键输入信号,如果key_in='0',则保持在S0状态,并继续采样按键输入信号的状态,如果key_in='1',则转入S1状态;在S1状态下key_out输出仍为低电平,继续采样按键输入信号的状态,如果key_in='1',则转入S2状态,如果key_in='0'则转入S0状态;在S2状态下继续采样按键输入信号的状态,如果key_in='1',则保持在S2状态,key_out输出正脉冲,如果key_in='0',则转入S0状态,key_out输出低电平。

下图为状态机型消抖电路波形仿真图

实验使用的状态机为14个状态的状态机,如下图所示,能够更加有效的消除掉抖动信号。

液晶显示

1602常用与显示数字和字母,显示容量为16*2个字符,内部有80个字节的RAM缓冲区,当要向1602送数显示时,要先发送显示地址指针80H+地址码。

内部地址码分布:

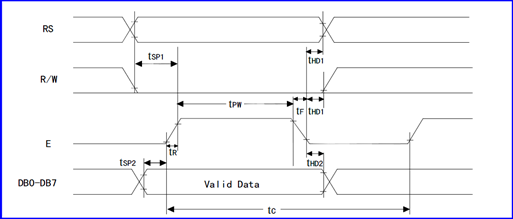

1602有16个管脚,其中用于编程操作的有RS(数据命令),RW(读写),E(使能端),D0-D7(并行数据端口)。

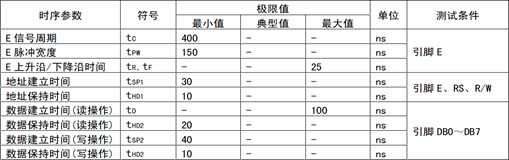

由于只要向1602写数据,因此给出写时序图和其时序图上的时序参数:

(其指令说明请详细查看1602数据手册)

Verilog的编程只要遵循时序图描写出时序图那样的信号和满足其时序参数就可以实现FPGA控制1602显示,并且可用状态机实现。

其中由于是往1602写数据因此RW可一直置0电平,使能信号E可以做成时钟信号用于控制数据的传输。

资源使用情况