配套FPGA开发板(含该设计的工程代码):https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-4676525296.4.6e8950ed57YPhv&id=17848039135

功能

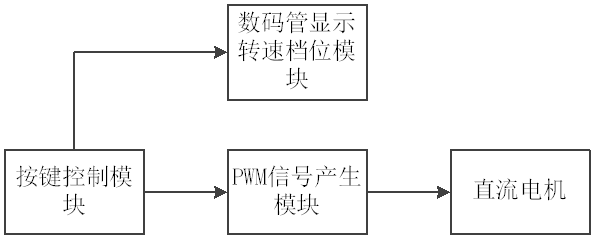

本设计主要分为三个主要部分:按键控制部分、数码管转速档位显示部分、PWM信号产生部分。分别采用verilog 语言完成底层模块的设计和以原理图的方法完成顶层模块的设计,采用自顶向下的设计方法,实现通过按键控制直流电机的转速,并将转速档位分为10个等级,同时将当前的转速档位显示到数码。在软件平台下分别对设计项目、各个模块以及顶层模块进行仿真分析。

接电机

电机有两条线,红色那条接到 这个。

这个。

蓝色那条接到

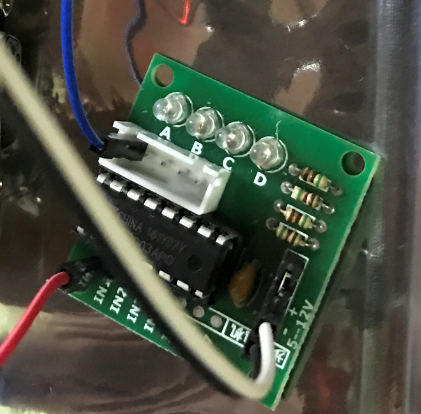

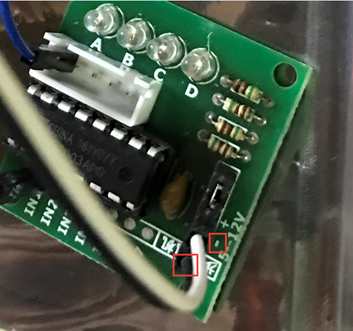

接电机驱动板

电机驱动板有4条线:PWM驱动信号输入--红色、PWM驱动信号输出--蓝色(该线已经焊接在电机上面)、3.3V电源--白色、地--黑色。

PWM驱动信号输入--红色线,接FPGA板上的142号引针

注意,这条线要等到下载好之后才能接!!!!!!!!!!

PWM驱动信号输出--蓝色

接电机的时候就已经接好了。

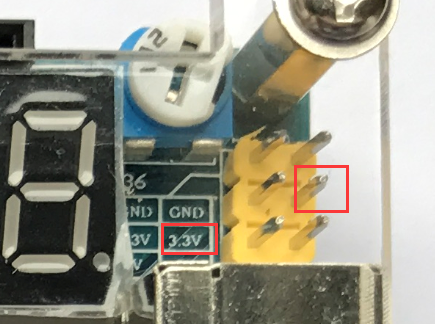

3.3V电源--白色

一头接电机驱动板上的"+"号引针,

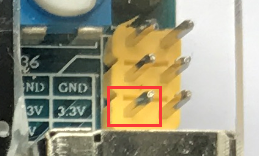

一头接FPGA开发板上的3.3V电源:

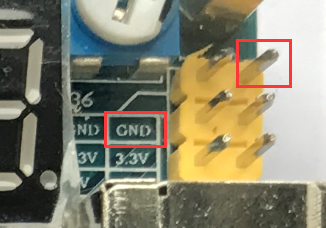

地--黑色

一头接电机驱动板上的"-"号引针,

一头接FPGA开发板上的地GND;

上电

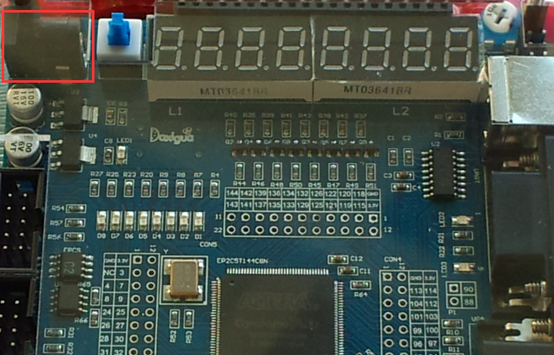

接入5V电源,用配套的线,USB那端接电脑即可;

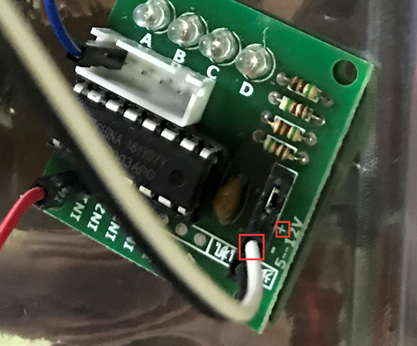

电源开关

按下电源开关

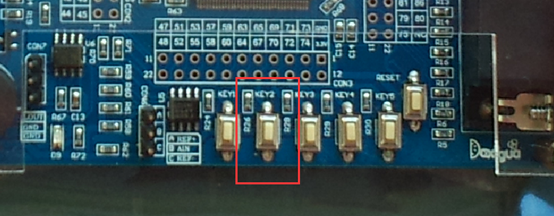

电路板按键说明

复位

按下则复位回1,输出占空比为10%;

控制档位

按下一次,档位加1,有时可能会产生跳变,按的时候不要太用力;

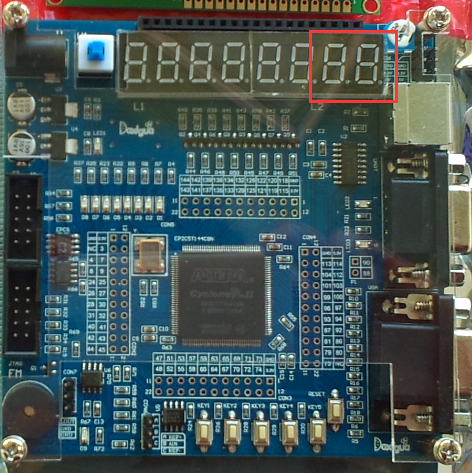

电路板数码管说明

显示档位

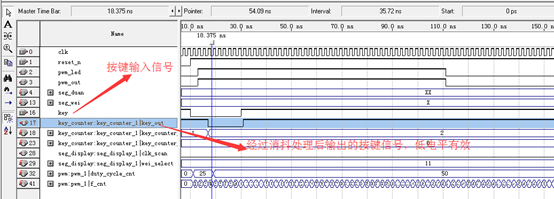

按键消抖原理

采用状态机型消抖方法进行,状态机型消抖电路采用有限状态机的设计方法来描述与实现,状态机有S0,S1,S2三种状态,在S0状态下key_out输出为低电平,并以clk时钟信号的频率采样按键输入信号,如果key_in='0',则保持在S0状态,并继续采样按键输入信号的状态,如果key_in='1',则转入S1状态;在S1状态下key_out输出仍为低电平,继续采样按键输入信号的状态,如果key_in='1',则转入S2状态,如果key_in='0'则转入S0状态;在S2状态下继续采样按键输入信号的状态,如果key_in='1',则保持在S2状态,key_out输出正脉冲,如果key_in='0',则转入S0状态,key_out输出低电平。

下图为状态机型消抖电路波形效果示意图:

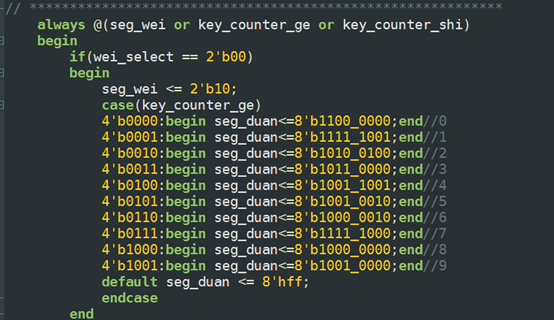

数码管显示原理

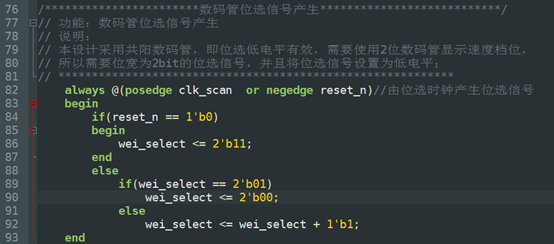

位选信号

本设计采用共阳数码管,即位选低电平有效,需要使用2位数码管显示速度档位,所以需要位宽为2bit的位选信号,并且将位选信号设置为低电平;

段选信号

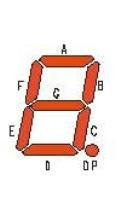

本设计采用共阳数码管,数码管的段选信号为8bit,数码管的段选对应实物图如下:

一个数码管有八段:A,B,C,D,E,F ,G,H,DP,即由八个发光二极管组成,; 因为发光二极管导通的方向是一定的(导通电压一般取为1.7V),这八个发光二极管的公共端有两种: +5V(即为共阳极数码管)、接地(即为共阴极数码管),其中共阳极每个段均有0导通,而共阴极则1导通发光,所以共阳极数码管和共阴极数码管显然是不同的,段选码表如下图所示:

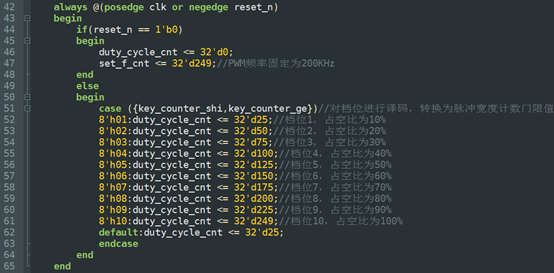

PWM产生原理

PWM的全称为Pulse-Width Modulation(脉冲宽度调制,),实际就是调节脉冲的占空比。当输出的脉冲频率一定时,输出脉冲的占空比越大,相当于输出的有效电平越大,这样也就简单实现了由FPGA来控制模拟量。由一个独立按键key来控制FPGA输出脉冲的占空比,用该脉冲去直接驱动直流电机,随着占空比不同,电机的转速也将不同。

本设计将PWM频率固定为200KHz,而通过控制PWM的脉冲宽度来调节电机的转速,计算频率的方法为50M/(249+1)。采用定时计数法来产生PWM波,即一个脉冲的周期为250个系统时钟周期脉冲宽度调制就是对这250个系统时钟进行分配,分配多少个系统时钟周期输出高电平,多少个系统时钟周期输出低电平。

仿真图

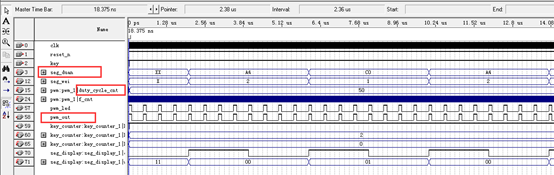

按键模块仿真

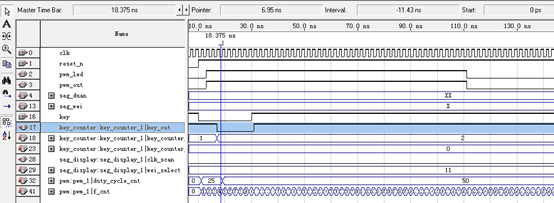

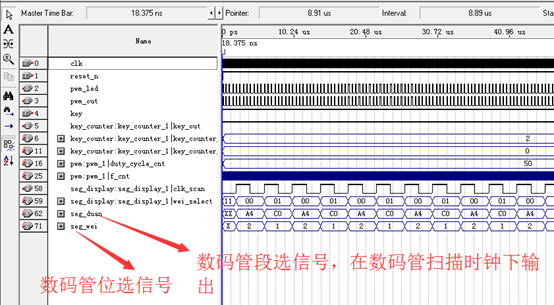

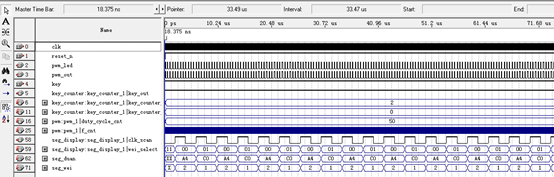

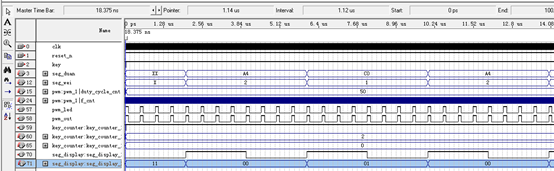

数码管模块仿真

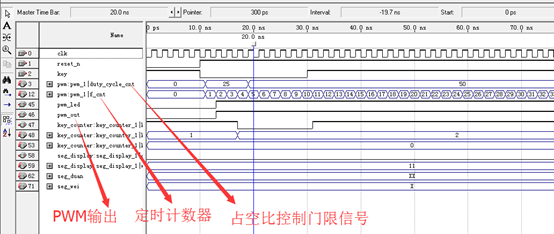

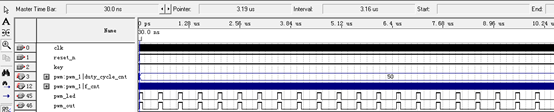

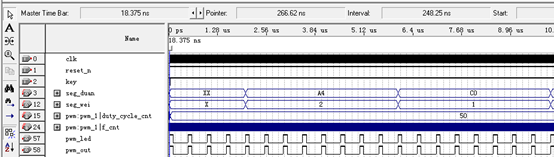

PWM产生模块仿真

duty_cycle_cnt在复位时为0,复位完成后初始化为25,对应的占空比为10%,由于档位控制按键按下,将档位控制为档位2,所以duty_cycle_cnt变为50,即控制输出20%的占空比。

整体仿真

将档位控制为档位2,所以duty_cycle_cnt为50,即控制输出20%的占空比,此时输出PWM信号。当数码管的段选信号seg_duan输出的十六进制数:C0,对应的位选信号seg_wei输出的十进制数为:1,根据数码管BCD码表,表示在第二位数码管上面显示的数为:0;当数码管的段选信号seg_duan输出的十六进制数:A4,对应的位选信号seg_wei输出的十进制数为:2,根据数码管BCD码表,表示在第二位数码管上面显示的数为:2。