Vivado建立工程流程

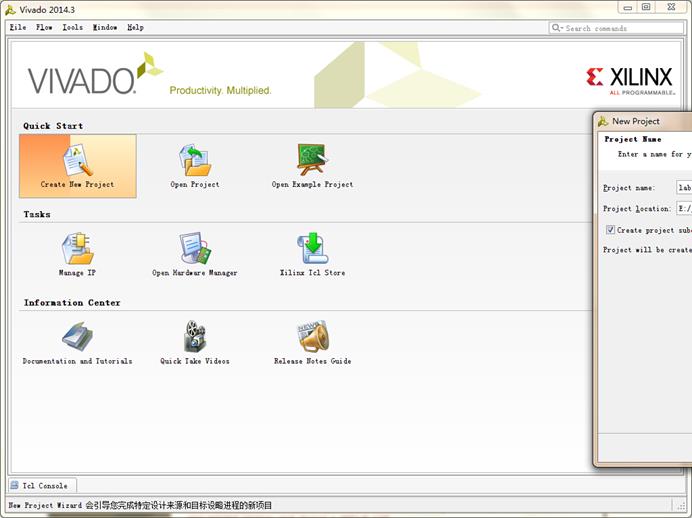

双击桌面的 图标,打开vivado软件,然后进入如下图所示的界面,点击create new project,即创建新的工程。

图标,打开vivado软件,然后进入如下图所示的界面,点击create new project,即创建新的工程。

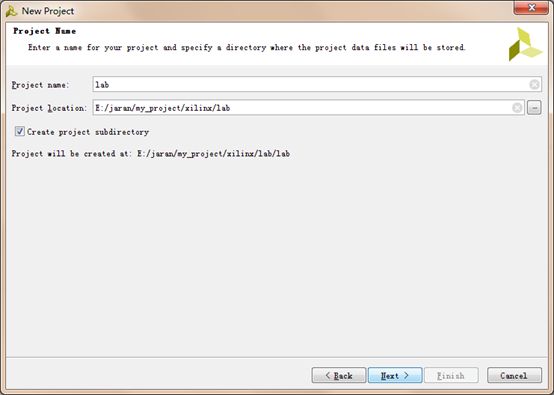

设置工程名称和工程路径,设置路径的时候要记住一点就是,软件会以工程名称建立以个文件夹,这里工程名设置为lab,路径可以自行设置不过不要在含有中文的路径之下。

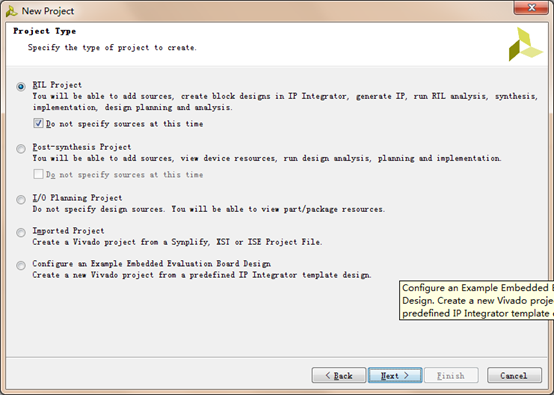

需要从 RTL 代码开始综合,因此选择 RTL Project。下面的 Do not specify source at this time 用于选择是否指定源代吗文件,即是是否需要添加已经设计好的代码文件,这里可以选中那个方框,从新开始编写代码文件,然后点击next。

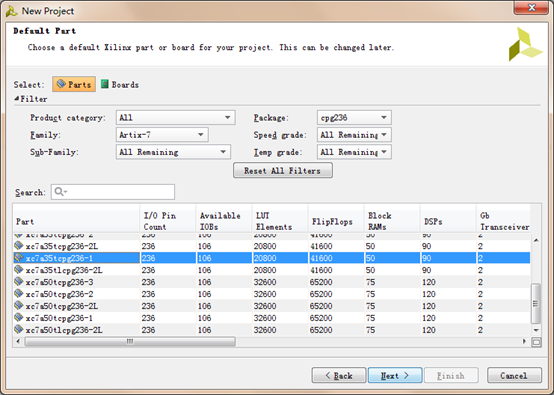

接下来就是选中FPGA器件型号,开发板的型号为xc7a35tcpg236-1,选中好之后,点击next。

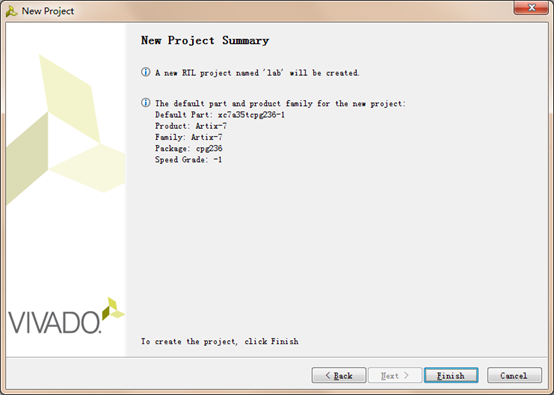

至此,工程创建完成,接下来进行代码的编写。

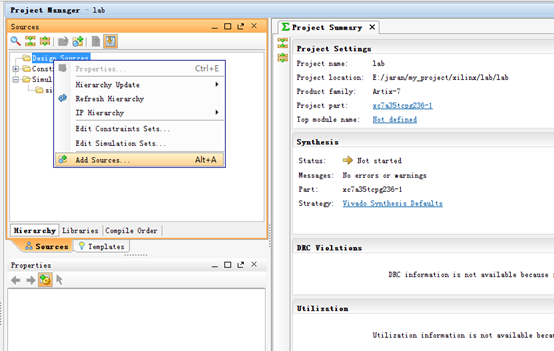

完成之后,会进入到软件的工程操作界面,在source这一框里面,由于还没有添加或者编写源代码文件,所以需要选中design,然后右击选中add sources,添加已经编写好的源代码文件。

添加源文件

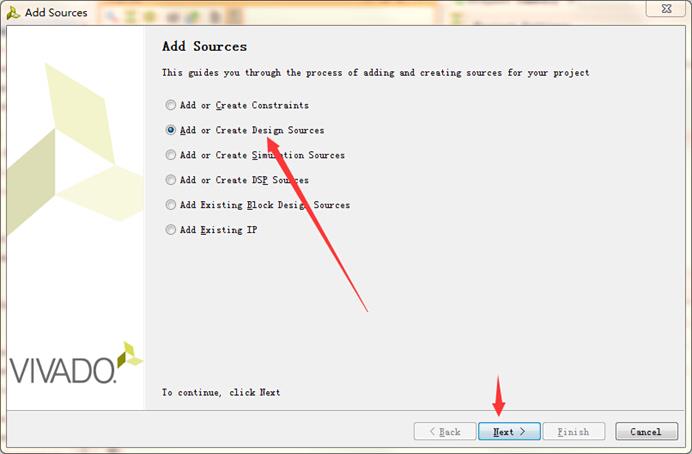

选中add or create design sources,即添加或者创建新的代码文件,然后点击next。

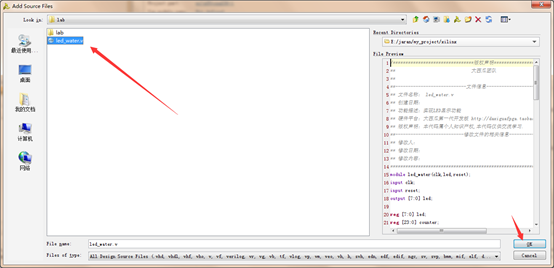

点击add files添加文件

这个实验为流水灯实验,选中已经编写好的源代码文件,然后点击ok。

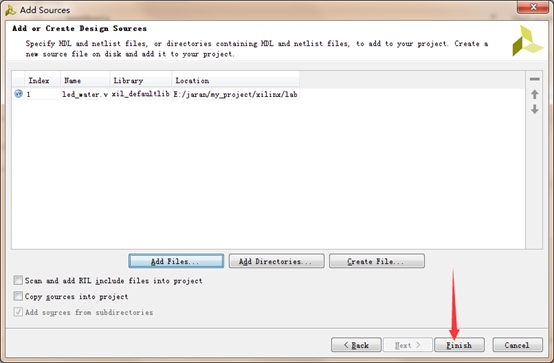

添加完成文件之后,点击finish。

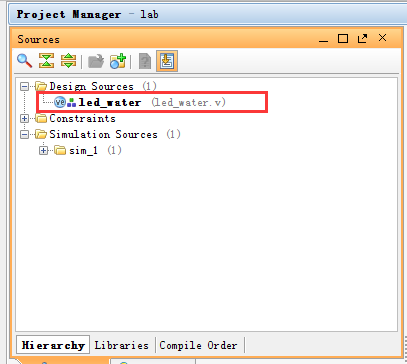

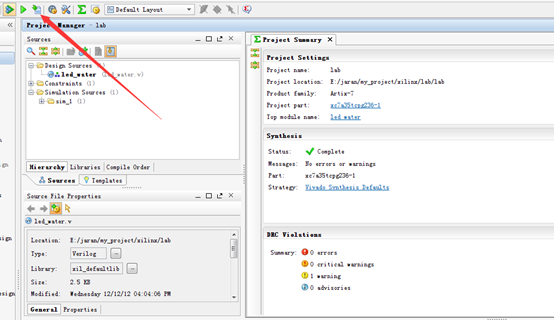

在这个 Sources 窗口中,Vivado 会自动加粗识别出来的top module,由于这个工程中只涉及到一个文件,所以一般就是默认这个文件为顶层文件。

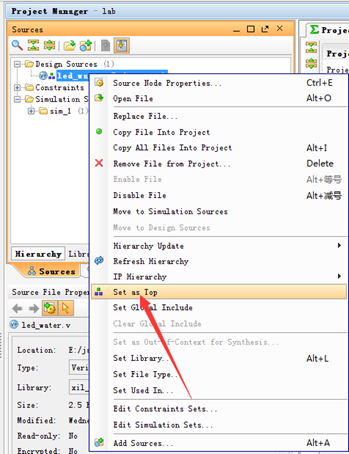

软件总是有不智能的时候,如果软件无法正确判断出哪个文件是顶层文件,这时可以通过选中对应的文件,然后右击选中set as top将对应的文件设置为顶层文件。

添加约束文件

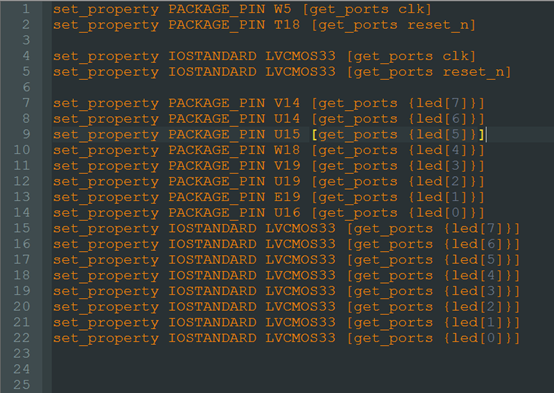

文件添加完成之后,可以添加约束文件,对FPGA引脚进行约束操作,vidado采用的约束文件是xdc,和ISE的约束文件不能通用。根据开发板原理图,编写xdc文件,如下所示:

内容为:

set_property PACKAGE_PIN W5 [get_ports clk] set_property PACKAGE_PIN T18 [get_ports reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property PACKAGE_PIN V14 [get_ports {led[7]}] set_property PACKAGE_PIN U14 [get_ports {led[6]}] set_property PACKAGE_PIN U15 [get_ports {led[5]}] set_property PACKAGE_PIN W18 [get_ports {led[4]}] set_property PACKAGE_PIN V19 [get_ports {led[3]}] set_property PACKAGE_PIN U19 [get_ports {led[2]}] set_property PACKAGE_PIN E19 [get_ports {led[1]}] set_property PACKAGE_PIN U16 [get_ports {led[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}] |

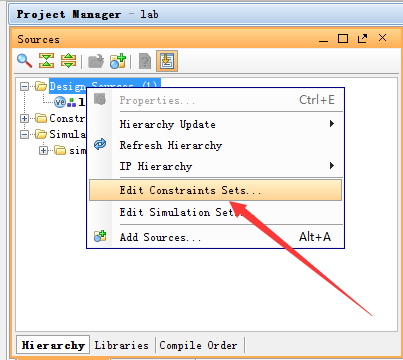

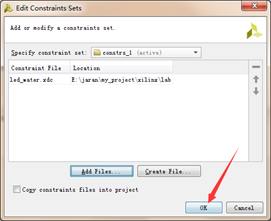

完成xdc文件的编写后,可以通过选中design sources,然后右击选择edit constraints sets进行设置xdc文件。

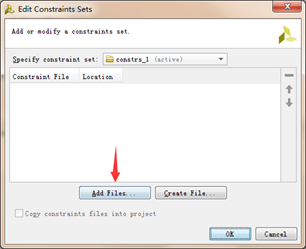

点击add files,添加xdc文件。

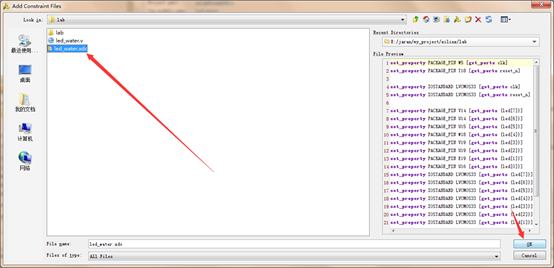

选中添加刚才编写好的xdc文件,然后点击ok。

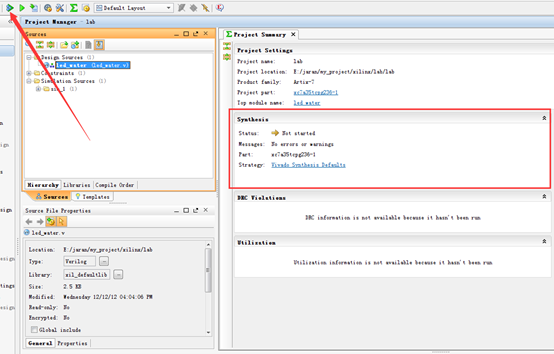

编译综合工程

点击左上角的图表,如下图所示,进行run synthesis。

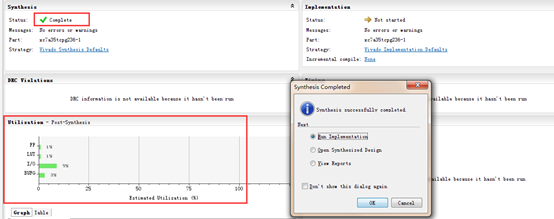

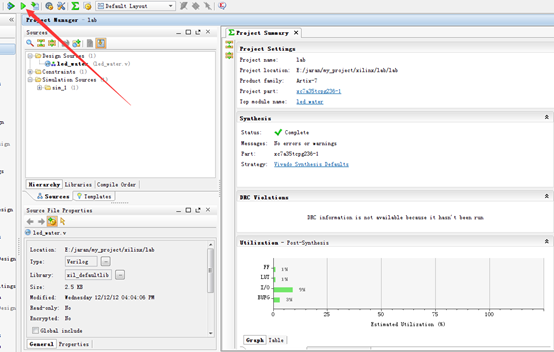

综合完成后,会弹出这样一个提示小窗口。如果没什么问题可以直接点击 Run

Implementation,在这里我们先点 Open Synthesized Design,查看综合后的设计,点击view report可以查看资源的使用情况等信息。

布局布线

完成综合之后,就可以进行映射到FPGA芯片,即进行布局布线的过程。点击左上角的图表,如下图所示,进行Run Implementation。

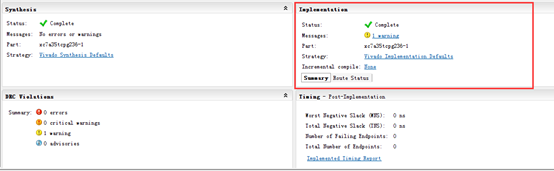

完成之后可以在Implementation框中查看布局布线的情况。

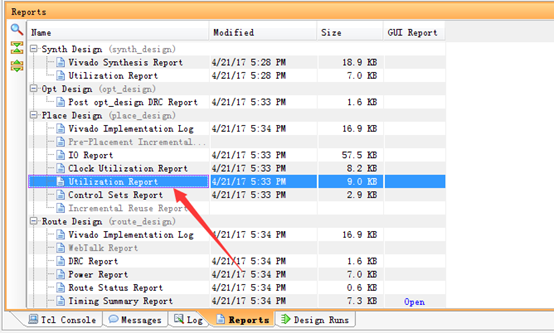

完成之后,可以通过报表查看资源的使用量。

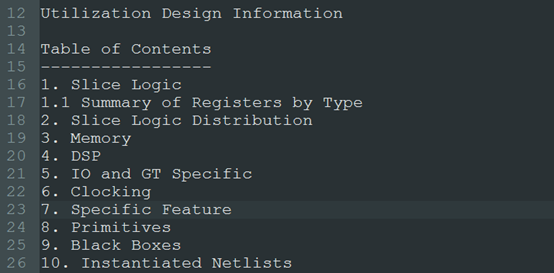

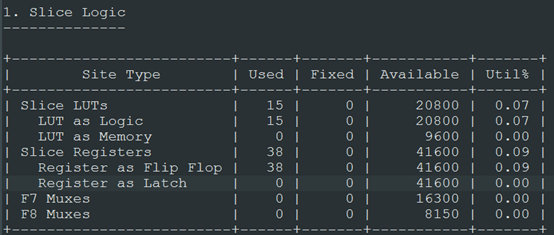

双击改报表之后会出现,资源使用报表信息,具体包括:

可以在报表中详细查看,如lut使用了15个,占用率为0.07%。寄存器位38,使用率为0.09%。

完成之后, 在 [project_name].runs/impl_1/

这个目录下会生成[top_module_name]_routed.dcp这个文件,继续点击 generate bit file 即可生成 bit 文件。

生成bit流文件

点击左上角的图表,如下图所示,点击 generate bit file 即可生成 bit 文件。

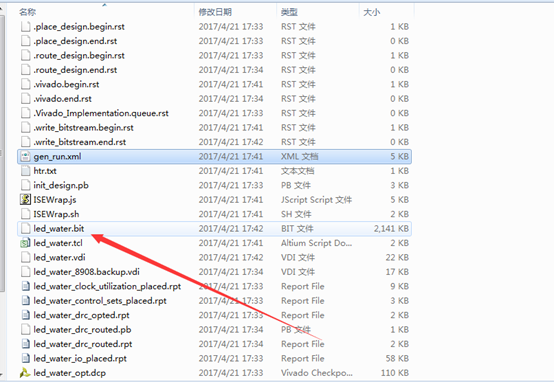

生成完后之后,可以在【lab.runs】夹中查看,生成的bit流文件。