AD_TLC549采集模拟信号

实验原理

芯片介绍

TLC549是 TI公司生产的一种低价位、高性能的8位A/D转换器,它以8位开关电容逐次逼近的方法实现 A/D转换,其转换速度小于 17us,最大转换速率为 40000HZ,4MHZ典型内部系统时钟,电源为 3V至 6V。它能方便地采用三线串行接口方式与各种微处理器连接,构成各种廉价的测控应用系统。

TLC549 引脚图及各引脚功能

TLC549引脚图

REF+:正基准电压输入 2.5V≤REF+≤Vcc+0.1。

REF-:负基准电压输入端,-0.1V≤REF-≤2.5V。且要求:(REF+)-(REF-)≥1V。

VCC:系统电源3V≤Vcc≤6V。

GND:接地端。

/CS:芯片选择输入端,要求输入高电平 VIN≥2V,输入低电平 VIN≤0.8V。

DATA OUT:转换结果数据串行输出端,与 TTL 电平兼容,输出时高位在前,低位在后。

ANALOGIN:模拟信号输入端,0≤ANALOGIN≤Vcc,当 ANALOGIN≥REF+电压时,转换结果为全"1"(0FFH),ANALOGIN≤REF-电压时,转换结果为全"0"(00H)。

I/O CLOCK:外接输入/输出时钟输入端,同于同步芯片的输入输出操作,无需与芯片内部系统时钟同步。

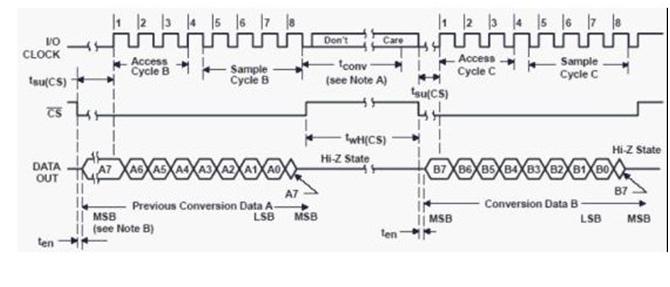

TLC549工作时序

当/CS变为低电平后, TLC549芯片被选中,同时前次转换结果的最高有效位MSB (A7)自 DATA OUT 端输出,接着要求自 I/O CLOCK端输入8个外部时钟信号,前7个 I/O CLOCK信号的作用,是配合 TLC549 输出前次转换结果的 A6-A0 位,并为本次转换做准备:在第4个 I/O CLOCK 信号由高至低的跳变之后,片内采样/保持电路对输入模拟量采样开始,第8个 I/O CLOCK 信号的下降沿使片内采样/保持电路进入保持状态并启动 A/D开始转换。转换时间为 36 个系统时钟周期,最大为 17us。直到 A/D转换完成前的这段时间内,TLC549 的控制逻辑要求:或者/CS保持高电平,或者 I/O CLOCK 时钟端保持36个系统时钟周期的低电平。由此可见,在自 TLC549的 I/O CLOCK 端输入8个外部时钟信号期间需要完成以下工作:读入前次A/D转换结果;对本次转换的输入模拟信号采样并保持;启动本次 A/D转换开始。

TLC549工作时序

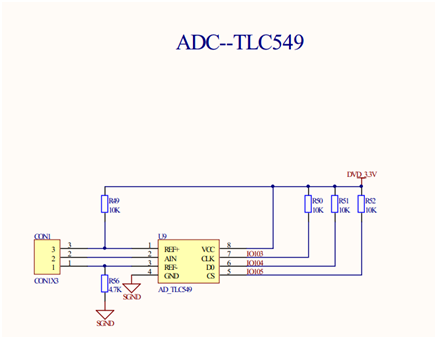

本实验中,我们使用TLC549芯片检测模拟电压,为方便检测,我们在实验中,使用了数码管作为我们的显示模块,将检测到的电压显示到数码管上,与实际的电压进行比较。开发板上,芯片VCC=3.3V,VREF+=3.3V,VREF-=0。

硬件原理图

实验代码

|

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: ADC_TLC549.v ** 创建日期: ** 功能描述:使用AD芯片TLC549采集模拟信号,经过模数转换并显示在数码管上 ** 操作过程:将模拟信号接到TLC549的数据管脚上,观察数码管变化 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module ADC_TLC549 ( clk,//系统50MHZ时钟 adc_sclk,//AD TLC549的时钟 data,//AD TLC549的数据口 cs,//AD TLC549的片选择 wei,//数码管的为选择 duan //数码管的7段码 ); input clk; input data; output cs; output adc_sclk; output[7:0] duan; output[3:0] wei; reg cs,adc_sclk,clk1k,clk1ms; reg[15:0] count; reg[24:0] count1ms; reg[3:0] cnt; reg[2:0] number; reg[1:0] state; reg[3:0] wei; reg ledcs; reg[7:0] duan; reg[7:0] dataout; reg[16:0] tenvalue; parameter sample=2'b00, display=2'b01; /**********产生100k的采集时钟信号*********/ always@(posedge clk) begin if(count<=250) count<=count+1'b1; else begin count<=0; adc_sclk<=~adc_sclk; end end /*******产生周期为1ms即1kHz的信号*********/ always@(posedge clk) begin if(count1ms>25'd25000) begin clk1ms<=~clk1ms; count1ms<=0; end else count1ms<=count1ms+1; end /*********AD采样程序**************/ always@(negedge adc_sclk) begin case(state) sample: begin cs<=0; dataout[7:0]<={dataout[6:0],data}; if(cnt>4'd7) begin cnt<=0; state<=display; end else begin cnt<=cnt+1; state<=sample; end end display: begin cs<=1;//关AD片选 tenvalue<=(tendata((dataout>>4)&8'b0000_1111)*16+ tendata(dataout&8'b0000_1111))*129;// //得到采集的数据 state<=sample; end default: state<=display; endcase end /***********2进制转十进制函数*************/ function[7:0] tendata;//返回一个4位的数字 input[7:0] datain; begin case(datain) 4'b00000000: tendata=4'd0;//0 4'b00000001: tendata=4'd1;//1 4'b00000010: tendata=4'd2;//2 4'b00000011: tendata=4'd3;//3 4'b00000100: tendata=4'd4;//4 4'b00000101: tendata=4'd5;//5 4'b00000110: tendata=4'd6;//6 4'b00000111: tendata=4'd7;//7 4'b00001000: tendata=4'd8;//8 4'b00001001: tendata=4'd9;//9 4'b00001010: tendata=4'd10;// 4'b00001011: tendata=4'd11;// 4'b00001100: tendata=4'd12; 4'b00001101: tendata=4'd13; 4'b00001110: tendata=4'd14; 4'b00001111: tendata=4'd15; default:tendata=4'bzzzz_zzzz; endcase end endfunction /*********十进制转LED段选函数*********/ function[7:0] leddata;//返回一个8位的数字 input[3:0] datain; begin case(datain) 4'd0: leddata=8'b11000000;//0 4'd1: leddata=8'b11111001;//1 4'd2: leddata=8'b10100100;//2 4'd3: leddata=8'b10110000;//3 4'd4: leddata=8'b10011001;//4 4'd5: leddata=8'b10010010;//5 4'd6: leddata=8'b10000010;//6 4'd7: leddata=8'b11111000;//7 4'd8: leddata=8'b10000000;//8 4'd9: leddata=8'b10010000;//9 4'd10: leddata=8'b10111111;//- 4'd11: leddata=8'b01111111;//. default:leddata=8'bzzzz_zzzz; endcase end endfunction /********数码管扫描函数*************/ always@(posedge clk1ms) begin if(number==5) number<=0; else begin number<=number+1; case(number) 4'd0: begin duan<=leddata((tenvalue/10)%10);//个位 wei<=4'b1110; end 4'd1: begin duan<=leddata((tenvalue/100)%10);//十位 wei<=4'b1101; end 4'd2: begin duan<=leddata((tenvalue/1000)%10);//百位 wei<=4'b1011; end 4'd3: begin duan<=leddata(tenvalue/10000);//千位 wei<=4'b0111; end 4'd4: begin duan<=leddata(4'd11);//. 显示小数点 wei<=4'b0111; end endcase end end endmodule |

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。