8051内核介绍

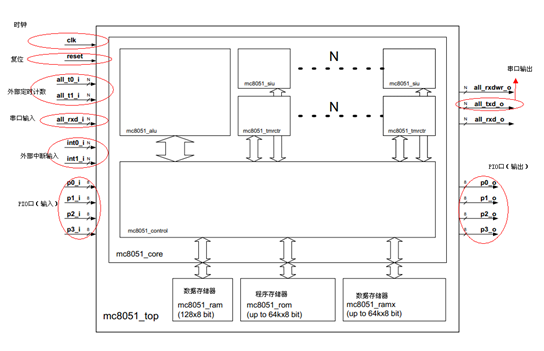

8051内核结构

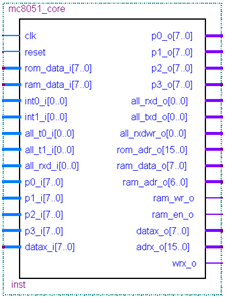

8051内核说明管脚

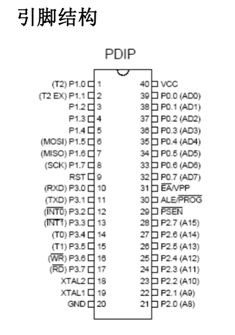

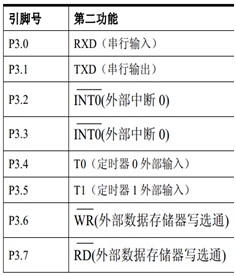

该部分的8051内核的顶层信号引脚在8051内核的顶层便可查看到各个引脚模块的定义。引脚的定义和普通的8051单片机相似,区别在于P3口的定义,普通的8051单片机的P3口有双重功能,在对普通的8051单片机编程时,特别是用C进行编程时所面向的是寄存器层面的,但在硬件层面上,在定义P3口的两种功能时是不一致的,原因是用C编程时,编译软件已经将C代码转变成机器代码,让机器能够辨别要用哪一个硬件模块,也就是8051的内核已经"解码"了机器码。普通的8051芯片的引脚框图和P3口的定义如下如下:

这里姑且不讨论哪些电源、地、时钟输入XTAL1/XTAL2、地址锁存控制信号ALE/PROG、外部程序存储器选通信号PSEN、访问外部程序存储器控制信号EA/VPP。可以看出剩下的都是单片机的外部通信操作接口(P0~P3口)。如果想进一步了解8051单片机的更多内容可以参考8051单片机的芯片手册。(这里不在多讲)

8051IP核

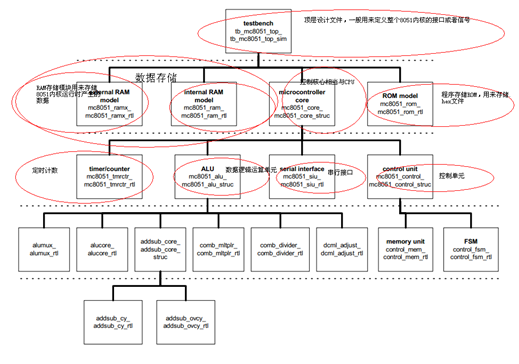

核心本身是由定时器/计数器,ALU,串行接口,和控制单元组成。

8015内核的原理图:

Clk:时钟输入

Reset:复位输入引脚

rom_data_i:ROM数据输入

ram_data_i :RAM数据输入

int0_i外部中断0

int1_i:外部中断1

all_t0_i:定时计数0

all_t1_i:定时计数1

all_rxd_i:串口接收

p0_i:IO-port0 input

p1_i:IO-port1 input

p2_i:IO-port2 input

p3_i:IO-port3 input

p0_o:IO-port0 output

p1_o:IO-port1 output

p2_o:IO-port2 output

p3_o:IO-port3 output

all_rxd_o:内部接收后直接输出,可以进入all_rxd_i

all_txd_o:串口发送

all_rxdwr_o:接收方向信号

rom_adr_o:输出到ROM地址信号

ram_data_o:输出到RAM数据信号

ram_adr_o:输出到RAM地址信号

ram_wr_o:数据输出到RAM的使能信号

ram_en_o:RAM的时钟使能信号

datax_i:从RAM 的数据输入到单片机的信号

datax_o:从单片机输出数据到RAM的信号

adrx_o:RAM 的地址信号

wrx_o:RAM的写使能信号

8051内核的设计层次和设计文件:

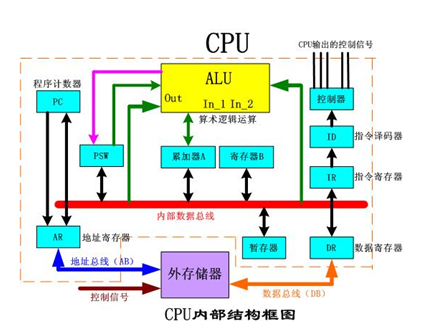

层次设计框图中的microcontroller core相当与CPU,一般的CPU的整体框图如下:

(该8051模块的设计文件都是用VHDL编写的所以要看懂器内部的构造还必须把VHDL学好)原理性的东西和层次结构已经说明了,现在就开始应用8051内核,把FPGA开发板打造成一块8051单片机开发板,先通过一个简单的实验看认识8051内核的使用。

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。