SDRAM读写一字

SDRAM控制模块

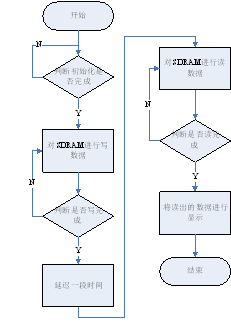

上电后进行初始化状态,初始化完成后进入空闲状态,在此进行判断如下判断:

如果自刷新时间到,则进行自刷新操作,操作完成后重新进入空闲状态;

如果读使能有效则进行读操作,操作完成后产生完成信号并延迟一个时钟周期重新进入空闲状态;

如果写使能有效则进行写操作,操作完成后产生完成信号并延迟一个时钟周期重新进入空闲状态。

其中自刷新状态的优先性最高,然后是写操作、最后是读操作;

SDRAM控制状态机流程图:

控制模块代码

自刷新定时

自刷新15us定时流程图

自刷新代码

SDRAM顶层模块

sdram_bank_add:读写SDRAM的地址

write_data: 写如sdram的数据

read_data: 从sdram读出的数据

read_req: 读数据请求信号

write_req: 写数据请求信号

rw_ack: 读写应答信号

bus_signal: 忙信号

init_done: 初始化完成信号,输出,高电平有效

SDRAM接口信号

sdram_clk: sdram时钟信号

sdram_data: sdram读写数据

sdram_command:cke、cs_n、ras、cas_n、we_n,SDRAM指令信号

sdram_address:[13:12]BA , [11:0]Addr,SDRAM地址信号

sdram_dqm: SDRAM数据掩码

SDRAM测试模块编写

测试模块设计

根据SDRAM的顶层模块的接口信号,在判断sdram初始化完成后对sdram的特定地址进行写入数据,在写入完成后延迟一段时间,然后将该特定地址的数据读出显示在LED灯上,一验证整个工程的功能。

测试模块流程图

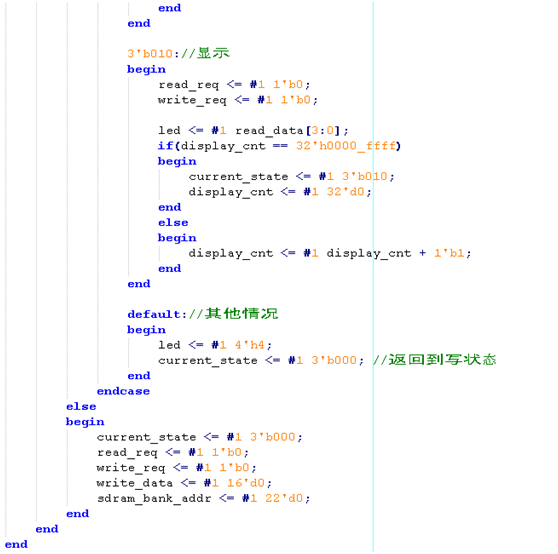

测试代码

实验效果

SDRAM原理图

LED原理图

实验的工程夹文件为"sdram_read_write_a_word",其源代码文件如下:

实验中对地址为10和11分别写入:16'h5555和16'h0003;

然后通过指定地址读出数据显示在LED灯上,实验中可以自行更改读写的地址和数据,以验证读写的正确性。

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。