27_基于FPGA的误码检测仪

实验原理

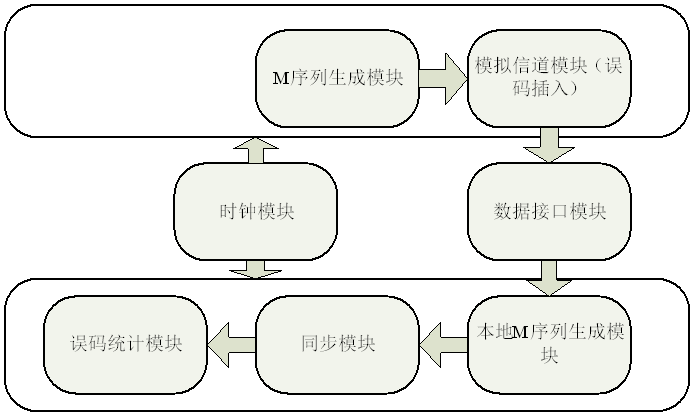

主要分为以下几个部分:

- 锁相环

- M序列生成模块

- 数据接口模块

- 模拟信道模块

- 本地M序列生成模块

- 同步模块

- 误码统计模块

锁相环

主要产生系统时钟信号和输出同步时钟信号。

采用Altera自带的IP模块

M序列生成模块

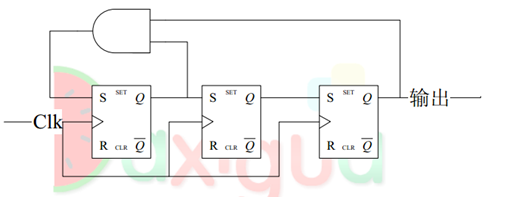

伪随机信号发生器又叫PN序列发生器或者是m序列发生器。m序列是一种线性反馈寄存器序列,m序列的产生可以利用r级寄存器产生长度为2^r-1的m序列,该实验中采用3级寄存器产生7序列发生器。其原理框图如下:(实验中反馈的信号采用异或进行反馈)

设计中采用的M序列为:f ( x) =x2 + x3 + x4 + x8

数据接口模块

由于没有实际信道,所以收发模块预留,这里进行了人为地插入误码,并将此误码作为模拟实际的信道。

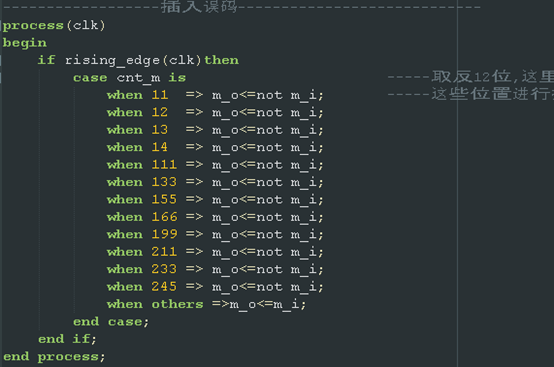

模拟信道模块

误码插入模块,采用的简单的方法进行插入。

根据输入的M序列和序列的位置,对某些想要插入的位置的M序列进行取反操作,然后进行插入。

本地M序列生成模块

与M序列生成模块相同。

同步模块

同步判断是进行误码统计的先决条件,只有对接收的码序列与本地码序列不断地进行同步判断,确定收、发端处于同步状态,那么误码统计才有意义。在通信系统中同步的方法有很多,通常采用的方法有滑动相关法,匹配滤波法等。

本设计中采用的是滑动相关法,以7个序列为滑动的范围,进行同步判断,确定收、发端处于同步状态,当误码数小于3时才继续循环判定。

误码统计模块

当收发端已经判断同步后,只要将接收信号于本地的M序列流进行同步的串行比较就可以统计误码的数量。当统计完成256个时,才输出误码数量。

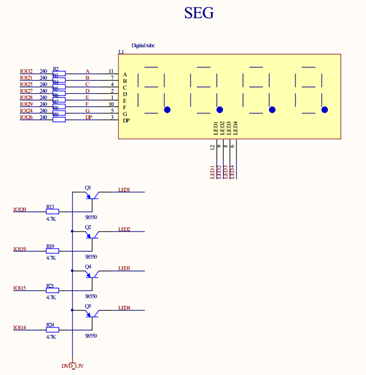

硬件原理图

实验代码

- 顶层设计文件

- 锁相环

- M序列生成模块

- 数据接口模块

- 模拟信道模块

- 本地M序列生成模块

- 同步模块

- 误码统计模块

仿真操作

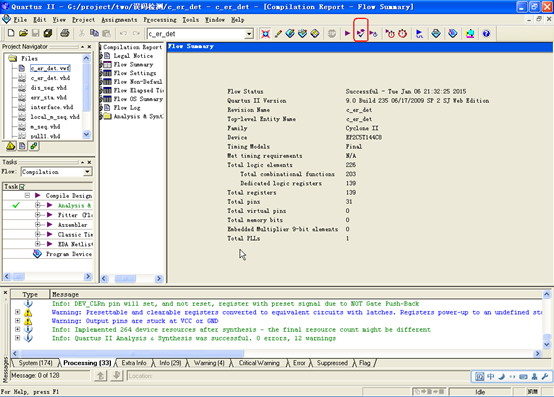

编译

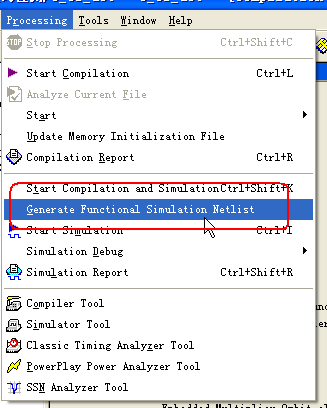

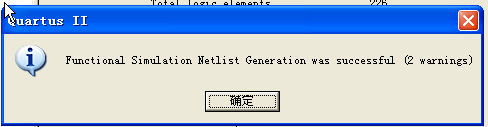

生成网表

开始仿真

实验效果

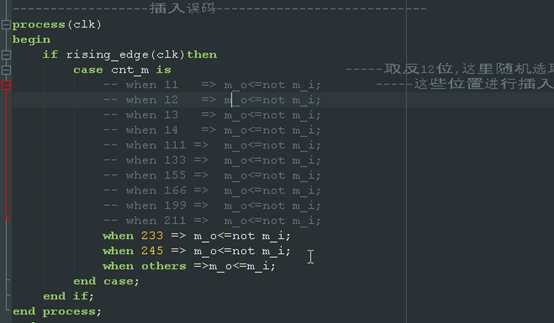

这里可以人为地插入误码的位置和控制误码的数量,这里随机地选取了一下这些位置。总共插入了12个误码。(你可以自己增加误码数或者改变误码的位置)

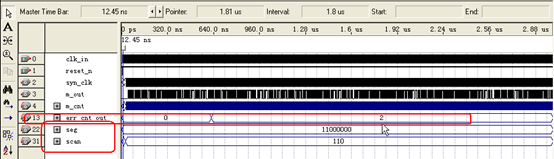

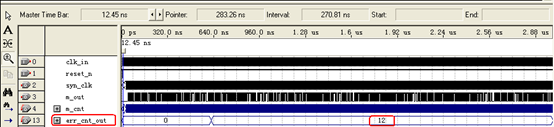

仿真结果如下

err_cnt_out输出的值为12,符合插入的误码数。

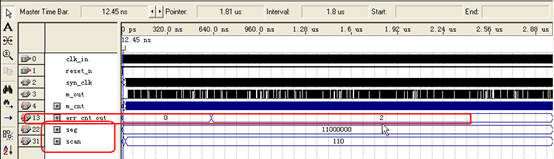

总共插入了2个误码:

err_cnt_out输出的值为12,符合插入的误码数。

Scan、 seg为后期电路板显示用的,仿真时不用管。

大西瓜FPGA-->https://daxiguafpga.taobao.com

配套开发板:https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.3.489d7241aCjspB&id=633897209972

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号"科乎"。