16_基于FPGA的DA_TLC5615驱动输出

实验原理

芯片简介

TLC5615 为美国德州仪器公司 1999 年推出的产品,是具有串行接口的数模转换器,其输出为电压型,最大输出电压是基准电压值的两倍。带有上电复位功能,即把 DAC 寄存器复位至全零。性能比早期电流型输出的 DAC 要好。只需要通过 3 根串行总线就可以完成 10 位数据的串行输入,易于和工业标准的微处理器或微控制器(单片机) 接口, 适用于电池供电的测试仪表、移动电话,也适用于数字失调与增益调整以及工业控制场合。

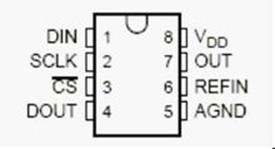

TLC5615 器件的引脚图及各引脚功能

TLC5615引脚图

DIN: 串行数据输入端; SCLK: 串行时钟输入端;

/CS: 芯片选用通端,低电平有效;

DOUT: 用于级联时的串行数据输出端;

AGND: 模拟地;

REFIN:基准电压输入端, 2V~ (VDD - 2),通常取2.048V;

OUT: DAC 模拟电压输出端;

VDD: 正电源端,4.5~5.5V ,通常取 5V。

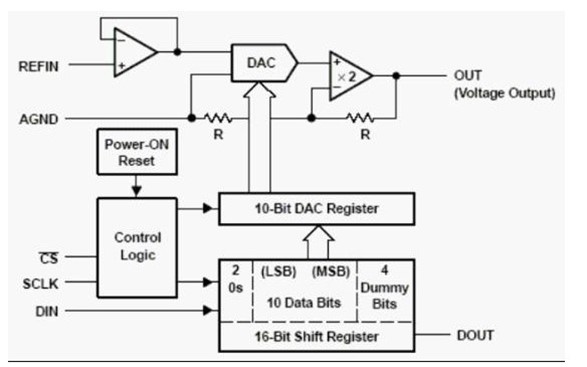

功能框图

TLC5615 的内部功能框图如下图所示,它主要由以下几部分组成:

1、10 位 DAC 电路;

2、一个 16 位移位寄存器, 接受串行移入的二进制数,并且有一个级联的数据输出端DOUT ;

3、并行输入输出的 10 位 DAC 寄存器, 为 10 位 DAC 电路提供待转换的二进制数据;

4、电压跟随器为参考电压端REFIN提供很高的输入阻抗,大约10MΩ;

5、×2 电路提供最大值为 2 倍于 REFIN 的输出;

6、上电复位电路和控制电路。

两种工作方式:

(A)从上图可以看出,16 位移位寄存器分为高 4 位虚拟位、低两位填充位以及 10位有效位。在单片 TLC5615 工作时,只需要向 16 位移位寄存器按先后输入 10位有效位和低 2 位填充位, 2 位填充位数据任意,这是第一种方式,即 12 位数据序列。

(B)第二种方式为级联方式, 即 16 位数据列,可以将本片的 DOU T 接到下一片的 DIN , 需要向 16 位移位寄存器按先后输入高 4 位虚拟位、10 位有效位和低 2 位填充位, 由于增加了高 4 位虚拟位, 所以需要 16 个时钟脉冲。

TLC5615功能框图

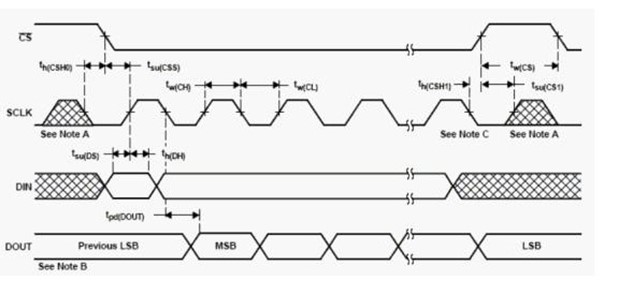

TLC5615 的工作时序

TLC5615 工作时序如下图所示。可以看出,只有当片选 CS 为低电平时, 串行输入数据才能被移入 16位移位寄存器。当 CS 为低电平时,在每一个 SCLK 时钟的上升沿将 DIN 的一位数据移入 16 位移寄存器。注意, 二进制最高有效位被导前移入。接着,CS 的上升沿将 16 位移位寄存器的 10 位有效数据锁存于 10 位 DAC 寄存器, 供 DAC 电路进行转换; 当片选 CS 为高电平时,串行输入数据不能被移入 16 位移位寄存器。注意, CS 的上升和下降都必须发生在 SCLK 为低电平期间。

TLC5615工作时序

工作原理

在我们的实验中,我们采用TLC5615的12位工作模式。其中10位是有效位,2位是填充位,填充位补0即可。芯片在片选/CS为低电平时工作。在每个SCLK上升沿将DIN的一位数据移入寄存器中。/CS的上升和下降都必须发生在SCLK为低电平的时候。在实验中,我们可以根据需要输出的电压,设置一个10位二进制数,

计算公式:Vout=VREF*(N/1024) N为10位二进制码。

开发板DA芯片VDD=5V,VREF=3.3V

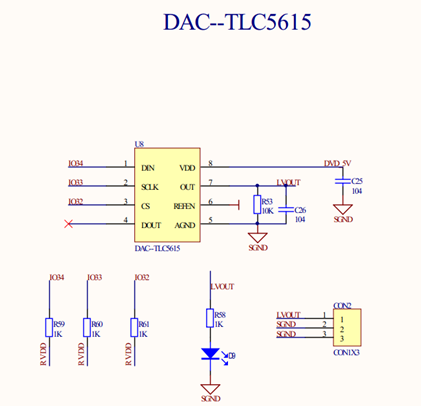

硬件原理图

为了方便大家能观察TLC5615输出的电压,我们附加一个例程,该例程添加了AD_TLC549芯片,只要用杜邦线把相应IO连接,通过数码管就可以显示输出的电压。

实验代码

TLC5615控制LED亮度

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: TLC615.v ** 创建日期: ** 功能描述:使用10位串行DA芯片TLC5615将数字信号转换为模拟信号,开发板DA芯片VDD=5V,VREF=3.3V 计算公式:Vout=VREF*(N/1024) N为10位二进制码 ** 操作过程:根据需求,在程序改变10位二进制数,在DA芯片的Vout脚输出相应电压 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module TLC5615 (clk, //内部时钟 sclk, //TLC5615 sclk时钟脚 din, //TLC5615 din数据脚 cs); //TLC5615 cs片选 input clk; output din; output cs; output sclk;

reg din; reg cs; reg sclk; reg[3:0] count1,count2,count3; reg [15:0] count4; reg clk_div; reg[9:0] din_reg; //10位数据寄存器 initial //初始化 begin cs=1; din=0; count1=0; count2=0; count3=0; din_reg=10'b00_0000_1111; //实验者可以根据需要修改10为二进制码 end

/*** sclk的频率设置为2.5MHz ***/ always@(posedge clk) begin if(count3==4'd9) begin sclk<=~sclk; count3<=0; end else count3<=count3+1; end

always@(posedge clk) begin if(count4==16'b1111_1111_1111_1111) begin clk_div<=~clk_div; count4<=16'b0; end else count4<=count4+1'b1; end

always @(posedge clk_div) begin if(din_reg==10'b11_1111_1111) din_reg<=10'b00_0000_0000; else din_reg<=din_reg+1'b1; end

/*** TLC5615 cs片选 ***/ always@(negedge sclk) begin if(count1>=4'd12&&count1<4'd15) begin cs<=1; //拉高片选 count1<=count1+4'd1; end else if(count1==4'd15) begin count1<=0; end else begin cs<=0; //拉低片选 count1<=count1+4'd1; end end

/*** 10位二进制码进行数模转换(采用12位传送方式即10位有效位+2位填充位) ***/ always@(posedge sclk) begin if(cs==0) begin case(count2) 4'd0:din<=1'd0; //无效位 4'd1:begin din<=din_reg[9];end //10位有效位 4'd2:begin din<=din_reg[8];end 4'd3:begin din<=din_reg[7];end 4'd4:begin din<=din_reg[6];end 4'd5:begin din<=din_reg[5];end 4'd6:begin din<=din_reg[4];end 4'd7:begin din<=din_reg[3];end 4'd8:begin din<=din_reg[2];end 4'd9:begin din<=din_reg[1];end 4'd10:begin din<=din_reg[0];end

4'd11:begin din<=1'd0;end //填充位 补0即可 4'd12:begin din<=1'd0;end //填充位 补0即可

4'd13:din<=1'd0; //无效位 4'd14:din<=1'd0; //无效位 4'd15:din<=1'd0; //无效位 default:begin count2<=0;din<=0;end endcase end if(count2==4'd15) count2<=0; else count2<=count2+4'd1; end endmodule |

TLC5615与TLC549联合实验

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: TLC615.v ** 创建日期: ** 功能描述:使用10位串行DA芯片TLC5615将数字信号转换为模拟信号,开发板DA芯片VDD=5V,VREF=3.3V 计算公式:Vout=VREF*(N/1024) N为10位二进制码 最后使用开发板上AD芯片TLC549将电压显示于数码管上 ** 操作过程:根据需求,在程序改变10位二进制数,在DA芯片的Vout脚输出相应电压 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module TLC5615_display (clk, //内部时钟 sclk, //TLC5615 sclk时钟脚 din, //TLC5615 din数据脚 cs); //TLC5615 cs片选 input clk; output din; output cs; output sclk;

reg din; reg cs; reg sclk; reg[3:0] count1,count2,count3; reg[9:0] din_reg; //10位数据寄存器

initial //初始化 begin cs=1; din=0; count1=0; count2=0; count3=0; din_reg=10'd250; //实验者可以根据需要修改10为二进制码 end

/*** sclk的频率设置为2.5MHz ***/ always@(posedge clk) begin if(count3==4'd9) begin sclk<=~sclk; count3<=0; end else count3<=count3+1; end

/*** TLC5615 cs片选 ***/ always@(negedge sclk) begin if(count1>=4'd12&&count1<4'd15) begin cs<=1; //拉高片选 count1<=count1+4'd1; end else if(count1==4'd15) begin count1<=0; end else begin cs<=0; //拉低片选 count1<=count1+4'd1; end end

/*** 10位二进制码进行数模转换(采用12位传送方式即10位有效位+2位填充位) ***/ always@(posedge sclk) begin if(cs==0) begin case(count2) 4'd0:din<=1'd0; //无效位 4'd1:begin din<=din_reg[9];end //10位有效位 4'd2:begin din<=din_reg[8];end 4'd3:begin din<=din_reg[7];end 4'd4:begin din<=din_reg[6];end 4'd5:begin din<=din_reg[5];end 4'd6:begin din<=din_reg[4];end 4'd7:begin din<=din_reg[3];end 4'd8:begin din<=din_reg[2];end 4'd9:begin din<=din_reg[1];end 4'd10:begin din<=din_reg[0];end 4'd11:begin din<=1'd0;end //填充位 补0即可 4'd12:begin din<=1'd0;end //填充位 补0即可 4'd13:din<=1'd0; //无效位 4'd14:din<=1'd0; //无效位 4'd15:din<=1'd0; //无效位 default:begin count2<=0;din<=0;end endcase end if(count2==4'd15) count2<=0; else count2<=count2+4'd1; end endmodule |

实验操作

实验效果

TLC5615控制LED亮度

TLC5615与TLC549联合实验

大西瓜FPGA-->https://daxiguafpga.taobao.com

配套开发板:https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.3.489d7241aCjspB&id=633897209972

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号"科乎"。