14_基于FPGA的DSS与嵌入式逻辑分析仪的调用

实验原理

DDS的原理

DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器,也可叫DDFS。

- DDS是从相位的概念直接合成所需波形的一种频率合成技术。

- 不仅可以产生不同频率的正弦波,而且可以控制波形的初始相位。

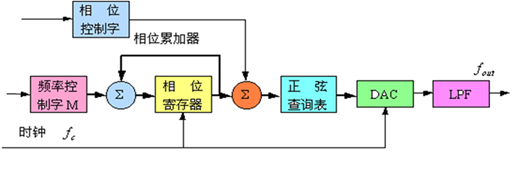

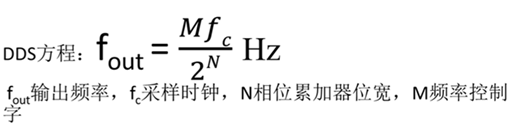

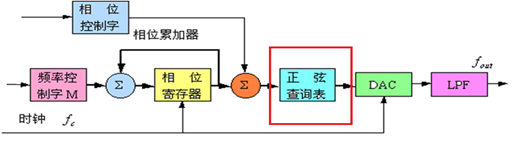

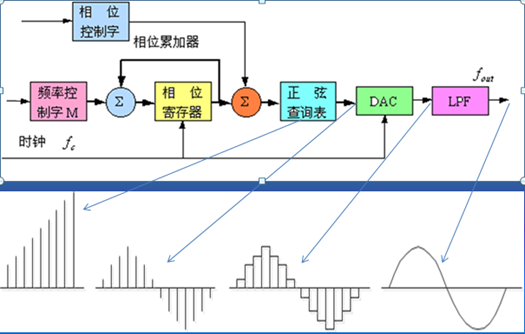

DDS原理框图

主要构成:

内部:相位累加器,正弦查找表

外围:DAC,LPF(低通滤波器)

工作过程

1、将存于ROM中的数字波形,经DAC,形成模拟量波形。

2、改变寻址的步长来改变输出信号的频率。步长即为对数字波形查表的相位增量。由累加器对相位增量进行累加,累加器的值作为查表地址。

3、DAC输出的阶梯形波形,经低通滤波,成为模拟波形。

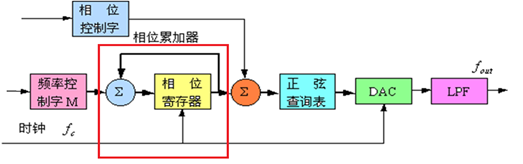

频率控制

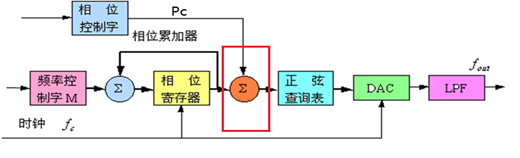

相位控制

波形存储

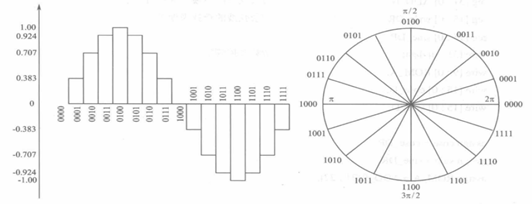

正弦信号相位与幅度的对应关系

可以将正弦波波形看作一个矢量沿相位圆转动,相位圆对应正弦波一个周期的波形。波形中的每个采样点对应相位圆上的一个相位点。

相位累加器的值作为ROM的地址,读取ROM的相位幅度,实现相位到幅度的转换。

AD转换和滤波

分析:

DDS优点

- 频率分辨率高,可达2的N次。

- 频率切换速度快,可达us量级。

- 频率切换时相位连续。

- 可以产生任意波形。

DDS缺点

- 输出频带范围有限。

- 输出杂散大。

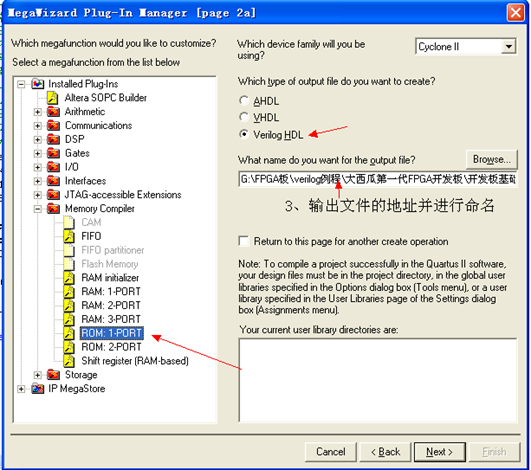

ROM的调用

(1)选择【Tools】--【Megawizard plug-zn Manager】,然后创建一个新的宏功能模块,

选择输出文件的语言类型和单端口ROM

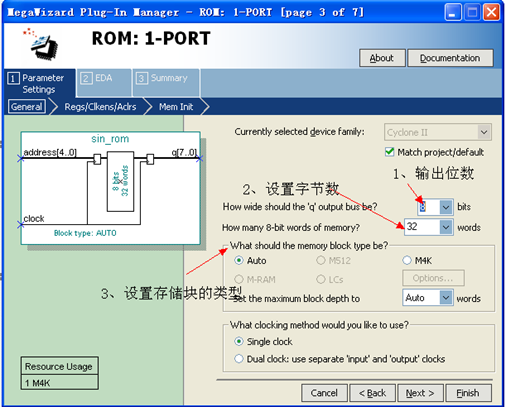

(2)ROM位宽和存储深度的设置

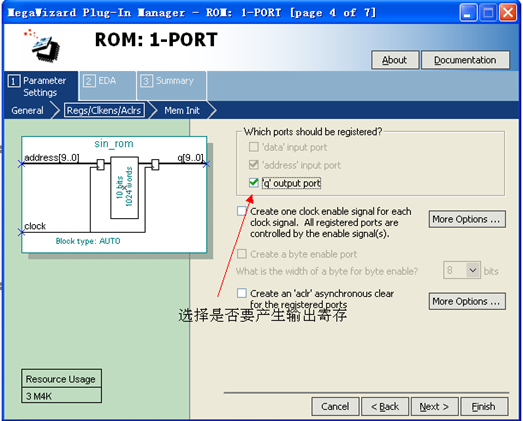

(3)选择是否要产生输出寄存,这个选择不用

(4)MIF文件的生成

ROM的初始文件的格式有两种:一种为.HEX文件;一种为.MIF文件。

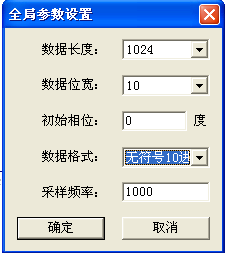

生成这两种文件的方法有很多种,这里因为要产生数字10位的正弦波,所以采用Mif_Maker2010软件进行生成。

步骤如下:

【设定波形】---【全局参数的设置】--【确定】--【设定波形】--【正弦波】,即可得到相应的波形;

【文件】--【保存】,选择保存途径并进行命名即可得到生成的MIF文件

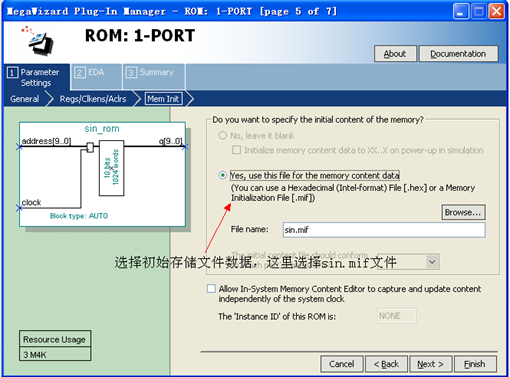

(5)MIF文件的调用

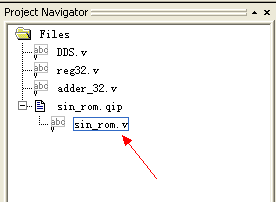

(6)然后一直点击Next,最后点击Finlish便生成该文件:

嵌入式逻辑分析仪的使用

- SignalTapⅡ逻辑分析仪是QuartusⅡ软件中集成的一个内部逻辑分析软件,

主要是用来观察设计的内部信号波形,方便查找设计中的缺陷。

- 在复杂的设计中,不能从外部的输入输出引脚上观察内部端口之间(如模块

与模块之间)的信号波形是否正确,这就可以使用SignalTapⅡ逻辑分析仪来

进行观察。

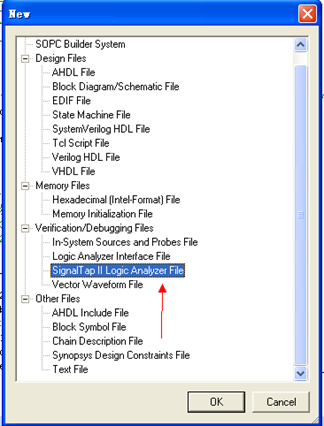

- 通过菜单【Tools】-【 SignalTap II Logic Analyzere】打开SignalTapII

窗口,将自动新建一个STP文件

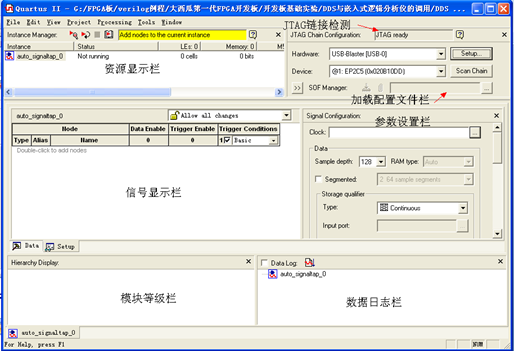

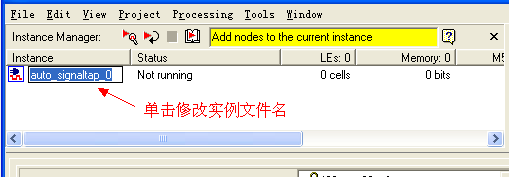

生成后出现如下窗口:

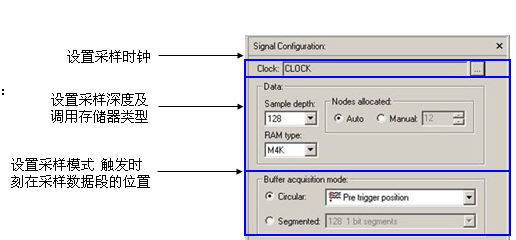

在上面的窗口中进行以下的设置:

1、参数设置栏的设置

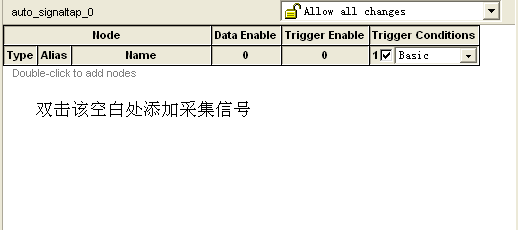

2、信号显示栏的设置:

添加方式与功能仿真时添加测试引脚一致,SignalTap II能够采集FPGA的引脚信号和内部寄存器的信号

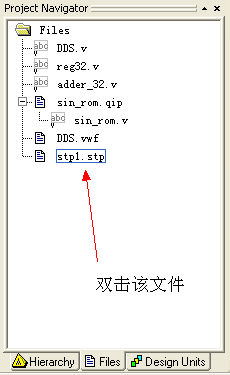

- 保存SignalTap II文件,然后关闭SignalTap II窗口,关闭后会提示是否将该文件加入整个工程中,这里选择YES,软件将重新综合整个工程项目。

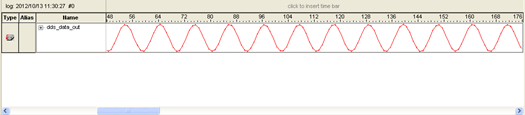

观察SignalTap II采集回来的信号,该信号是实际真实信号

下载

在出现的窗口中,单击 ,在下载成功后单击

,在下载成功后单击 ,然后在信号显示栏中选中信号右击,在出现的下拉列表中选择【Bus Display Form】--【Unsigned Line Char】即可观察线性信号。

,然后在信号显示栏中选中信号右击,在出现的下拉列表中选择【Bus Display Form】--【Unsigned Line Char】即可观察线性信号。

实验代码

DDS顶层代码

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: DDS.v ** 创建日期: ** 功能描述:DDS信号发生与嵌入式逻辑分析仪的调用 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module DDS(clk,dds_data_out,test_clk); input clk;//时钟输入 output [9:0] dds_data_out,test_clk;

wire clk; wire [9:0] dds_data_out; /**************连接线***************/ wire [31:0] f32_bus;//AC频率控制字输入 wire [31:0] reg32_out;//32位寄存器输出 wire [31:0] reg32_in;//32位寄存器输入 /************************************/ reg [15:0] clk_counter; reg test_clk; parameter [15:0] f32_bus_init=16'b0000_0000_0000_0000;

assign f32_bus[31:16]=f32_bus_init;//初始化,高位置低 assign f32_bus[15:0]=16'b0000_1111_1111_0000;//低位可以设置DDS的输出频率 /*********************元件例化***************************/ adder_32 u1(.data1(f32_bus),.data2(reg32_out),.sum(reg32_in)); reg32 u2(.clk(clk),.data_in(reg32_in),.data_out(reg32_out)); sin_rom u3(.address(reg32_out[31:22]),.clock(clk),.q(dds_data_out));//正弦 always @(posedge clk) begin if(clk_counter==16'b0001_0000_0000_0000) begin clk_counter<=16'b0; test_clk<=~test_clk;//产生SignalTap II的采集时钟 end else clk_counter<=clk_counter+1'b1; end endmodule |

32bit寄存器代码

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: reg32.v ** 创建日期: ** 功能描述:32位寄存器 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module reg32(clk,data_in,data_out); input clk; input [31:0] data_in; output [31:0] data_out;

wire clk; wire [31:0] data_in; reg [31:0] data_out;

always @(posedge clk) begin data_out<=data_in; end endmodule |

32bit加法器代码

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: adder_32.v ** 创建日期: ** 功能描述:32位累加器 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module adder_32(data1,data2,sum); input [31:0] data1,data2;//输入数1,2 output [31:0] sum;//和输出

wire [31:0] data1,data2; wire [31:0] sum;

assign sum=data1+data2;

endmodule |

实验效果

大西瓜FPGA-->https://daxiguafpga.taobao.com

配套开发板:https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.3.489d7241aCjspB&id=633897209972

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号"科乎"。