FPGA芯片内部硬件介绍

FPGA(Filed programmable gate device):现场可编程逻辑器件

FPGA基于查找表加触发器的结构,采用SRAM工艺,也有采用flash或者反熔丝工艺;主要应用高速、高密度大的数字电路设计。

FPGA由可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源(时钟/长线/短线)、底层嵌入功能单元、内嵌专用的硬核等组成;

目前市场上应用比较广泛的FPGA芯片主要来自Altera与Xilinx。另外还有其它厂家的一些低端芯片(Actel、Lattice)。

这里主要介绍AlteraCyclone II系列FPGA的内部硬件结构:

- FPGA器件结构

- 可编程输入/输出单元IOE

- 可编程逻辑单元LE

- 嵌入式块RAM

- 布线资源

- 底层嵌入功能单元

FPGA器件结构

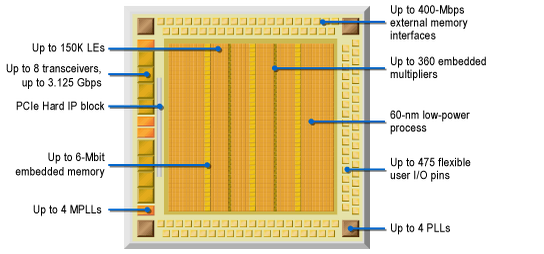

Altera cyclone IV器件结构

FPGA的内部结构包括:

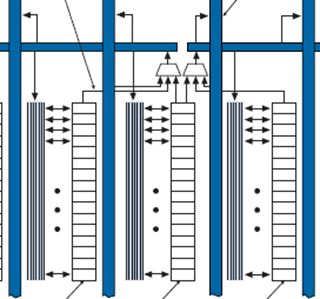

- 可编程逻辑门阵列,由最小单元LE组成

- 可编程输入输出单元IOE

- 嵌入式RAM块,为M4K块,每个的存储量为4K,掉电丢失

- 布线网络

- PLL锁相环,EP4CE6E22C8N最大的倍频至250MHz,这也是该芯片的最大工作频率

可编程输入/输出单元IOE

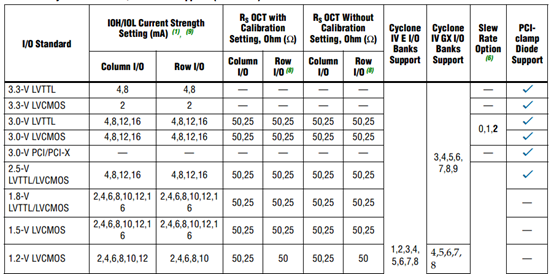

可编程I/O,可配置成OC门、三态门、双向IO、单端/差分等;支持各种不同的I/O标准:LVTTL、LVCOMS、SSTL、LVDS、HSTL、PCI等;

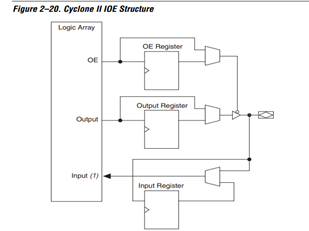

Altera 器件IOE结构

Altera器件的输入输出结构:可配置成三态、输入/输出、双向IO

Altera器件中cyclone系列中的IOE结构是基本的输入、输出、使能的触发器结构。

可编程逻辑单元LE

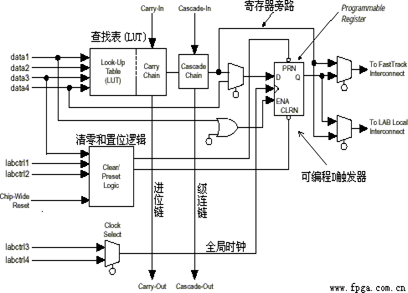

基本可编程逻辑单元LE由查找表(Look up table)触发器(FF)组成,而LE是组成LAB的最小单元;

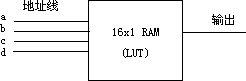

LUT一般是4输入查找表,高端器件(xilinx v5)采用LUT-6结构;LUT可看成4位地址线的16x1的RAM 结构。

FF是可编程的触发器,可配置成同步/异步复位、同步/异步置位、使能、装载等功能触发器。

可编程逻辑块:

Altera:LAB

Xilinx:CLB

Xilinx CLB由四个SLICE构成;而Altera的LAB由16个/8个LE构成;

基本逻辑单元LE/SLICE:

Altera:LE

Xilinx:SLICE

xilinx 为SLICE:包括两个LUT-4/两个FF;

altera为LE:包括一个LUT-4/一个FF;

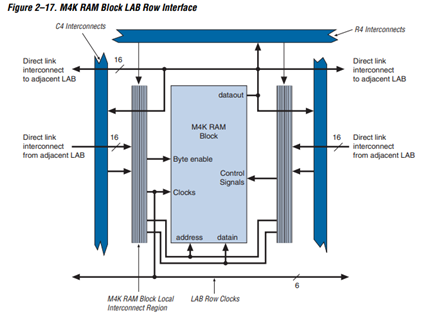

嵌入式块RAM

嵌入式块RAM可配置单/双端口RAM、伪双端口RAM、ROM、FIFO、SHIFT、CAM等;不同厂家的块RAM大小不一样:

Altera:M512、M4K M4K、M-RAM(512K);

Xilinx:18kbit;

Lattic:9kbit;

Altera:M4K:

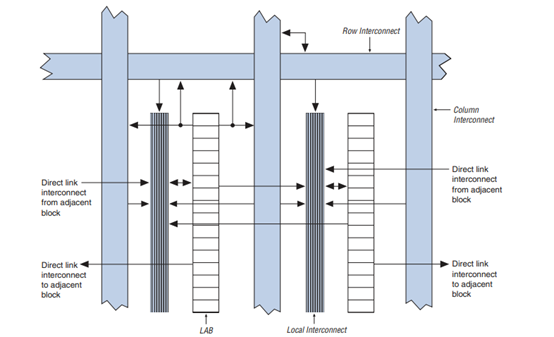

布线资源

全局布线资源:用于全局时钟/全局复位/全局置位布线;

长线资源:用于BANK或者嵌入式功能单元的高速信号或者第二全局时钟的布线;

短线资源:用于其中逻辑单元间的逻辑互联与布线;

全局布线资源:

全局时钟树:

底层嵌入式功能块

主要是指PLL/DPLL、DCM、DSP48、乘法器、嵌入式硬核/软核;

Xilinx:DCM、DSP48/48E、DPLL、Multiplier等

Altera:PLL/EPLL/FPLL、DSPcore等;

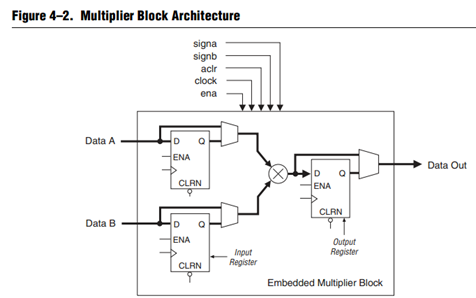

Multiplier结构

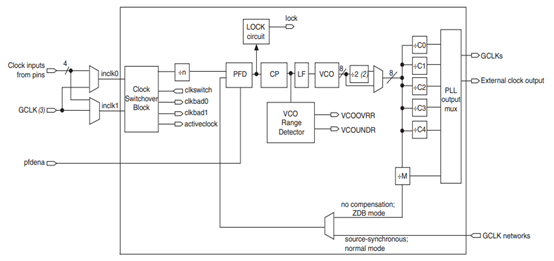

PLL/DCM:嵌入式锁相环

Altera:PLL

Xilinx:DCM

Altera的Cyclone II器件最多有四个PLL,分布在芯片四个角;需要主要的是Altera的PLL是模拟锁相环,在电源/地方面要做考虑。

Xilinx的spatan-3器件最多有四个DCM,也是分布在芯片四个角。

两者的区别:Altera的PLL可支持较低的输入频率,可Xilinx的DCM支持的最低锁相频率为24/32MHz;但Xilinx的高端器件Virtex-5的DPLL可达到很低的输入频率。

内嵌专用硬核

指高速串行收发器;GMAC、SERDES、PCIe等;

Xilinx:GMAC、SERDES、PCI、GTX、GRX

Atera:GMAC、SERDES、PCIe、SPI.4/SFI.5

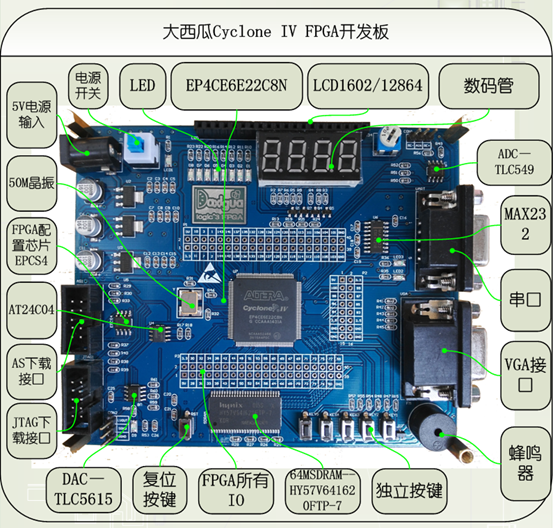

开发板硬件资源介绍

大西瓜FPGA-->https://daxiguafpga.taobao.com

配套开发板:https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.3.489d7241aCjspB&id=633897209972

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号"科乎"。