基于FPGA的OV7670驱动--第2部分

视频采集显示系统功能描述

在进入正题之前,先来普及下视频图像的概念。

人类从外部世界获取信息的70%~80%是从视觉获得的。

图像(image)在计算机中又被称为点阵图或者是位图,它将二维平面对象的信息细化为密集排列的点,然后将这些点的信息按顺序存储在计算机中。在计算机中,图像的实质是一个数字矩阵,矩阵中各项数据用来描述构成图像的每一个点的亮度、颜色等信息。构成图像的点被称为像素(pixel)。图像通常数字设备捕捉的实际场景图面或以数字化形式存储的任意画面来获得。

一个像素点的数据位宽通常为:1位、4位、8位、16位、24位、32位。真彩色图像就是用24位进行显示的。

颜色= R(红色的百分比)+G(绿色的百分比)+B(蓝色的百分比);

动画/视频是指由一系列的静止图面以一定的速度连续播放时,由于视觉暂留现象产生的连续动态的效果。视觉暂留现象是人眼的一个特性。这个特性是人能够把他看到的东西在视网膜上保留一段时间。一般的视觉暂留时间为1/12~1/16s。动画/视频中静止的图面为帧,一秒播放静止图面的数目为帧频,一般最低的帧频为12帧。

视频采集显示系统,即OV7670实时采集图像信息,然后通过VGA接口显示于显示屏上。具体实现过程如下:

FPGA驱动OV7670(CMOS图像传感器),OV7670的采集图像的速度为30帧/秒,FPGA接收OV7670的图像信息,然后以25M的时钟频率写入FPGA内部的异步FIFO中,在写入异步FIFO的同时,以100M的时钟频率将异步FIFO中的图像数据读出,并缓存到FPGA外部的SDRAM(HY57V641620ET-H)中。

SDRAM(HY57V641620ET-H)作为ping pang操作的缓存器,由于该 OV7670的分频率为30W,所以采用的VGA显示模式为640*480@60Hz,像素信息为RGB565,显示一帧的图像的数据量为640*480*16bit = 4915200bit。SDRAM(HY57V641620ET-H)的存储容量为64Mbit,分为4页,每一页的存储容量为16Mbit,对于存储一帧的图像数据已经足够了。

SDRAM(HY57V641620ET-H)作为ping pang操作的缓存器,实现的过程为使用其内部的两个存储页进行缓存,当一页正被写入数据时,另一页正被读出数据,这样循环操作。

例如当A页被写完时,转入B页进行写,此时也是B页被读完,转入A页进行读操作。这样就可以无间断地将采集的图像数据往SDRAM内部进行写入,也可以无间断地往SDRAM内部读出图像数据进行显示。

写SDRAM需要一个异步FIFO,当然读SDRAM也需要一个异步的FIFO,以100M的时钟频率将SDRAM中的数据读出之后再存储到异步FIFO中,然后以25M的时钟频率读出异步FIFO中的数据进行VGA显示。

该系统需要的25M和100M 时钟信号,由FPGA内部的PLL进行产生。

视频采集显示系统设计分析

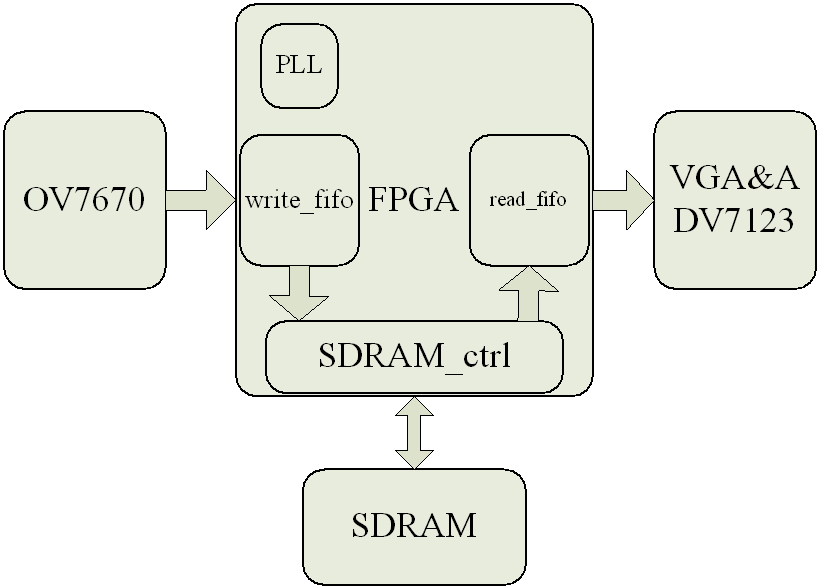

系统设计框图

系统说明:

OV7670将采集到的数据信号传送到FPGA内部的write_fifo中,write_fifo再将图像数据通过SDRAM_ctrl模块写入到SDRAM中,再通过SDRAM_ctrl模块将图像数据读出写入到read_fifo中,最后再将read_fifo中的图像数据读出通过VGA&ADV7123进行显示,在此期间SDRAM作为缓存器。

系统模块层次分析

在FPGA设计中经常遵循的设计方法是"至上而下"的设计方法,在该视频采集显示系统中也不例外,我们采用一种至上而下的设计思维,将我们之前所设计的所有模块综合起来(进行修改、连接)形成这样一个复杂的系统。

该系统中要用到的模块有:

-

ov7670的视频图像采集

-

SDRAM突发读写页

-

异步dcfifo的读写

-

VGA显示

-

PLL时钟产生

当然这里还需要进行很大的修改、调试使之满足我们的系统需要。

这种模块重用的方法很重要,在如今的电子设计中,电子系统的集成度将只会是越来越高,这是电子行业的趋势,所以我们要顺势而为,将一些常用的硬件模块或者是一些算法模块封装好,做成属于自己的IP,在需要的时候就可以快速地调用这些IP模块,加入到开发工程之中,避免再次去重写驱动代码和算法代码。以后的FPGA开发趋势应该是朝着IP调用,IP模块的来源应该是:官方、第三方公司、网上开源、自身。而对于一个FPGA开发工程师而言,更多的工作是在如何去选用IP和如何去运用IP。这是硬件开发的一个趋势,相信你已经看到了软件开发已经走在了这一条路上,安卓的高速发展是除了是开源外,更多的是其内部已经封装了很多的API函数,开发人员只需调用这些API函数,就可以很方便地进行设计,我相信以后的IP 也将会成为API一样,满足FPGA开发人员的设计需求,让FPGA设计更为方便。说了这么多,还是回归主题吧!

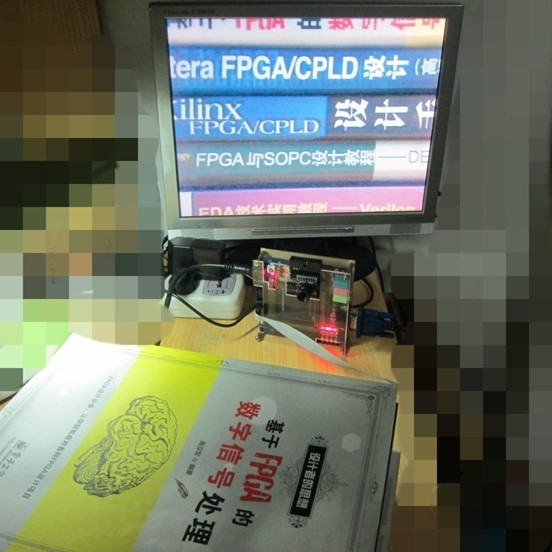

最后显示效果:

https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.7.489d7241aCjspB&id=35795666317