流水线

流水线使用存储器件将时钟周期内关键路径(最大组合延迟的路径)分割开来,减少了关键路径上各阶段延迟并使迪娜路能以更高频率工作。

优点:提高了时钟频率,增加了各阶段时钟的计算能力;

缺点:使用了更多的存储器单元,增加了面积和负载;

流水线要求

- 所有共享一条流水线的指令的阶段和阶段次序必须相同,例如“add”指令在存储器阶段什么也不做;

- 所有中间值必须在各周期锁存;

- 不能复用任何功能模块;

- 一个阶段的所有操作都应在一个周期内完成;

流水线冒险

冒险会干扰流水线并阻止下一条指令在目标周期内的执行,会降低流水线在理想情况下所能带来的速度提升。

主要分为三类:结构冒险、数据冒险、控制冒险。

参考:https://www.cnblogs.com/lfri/p/10053598.html

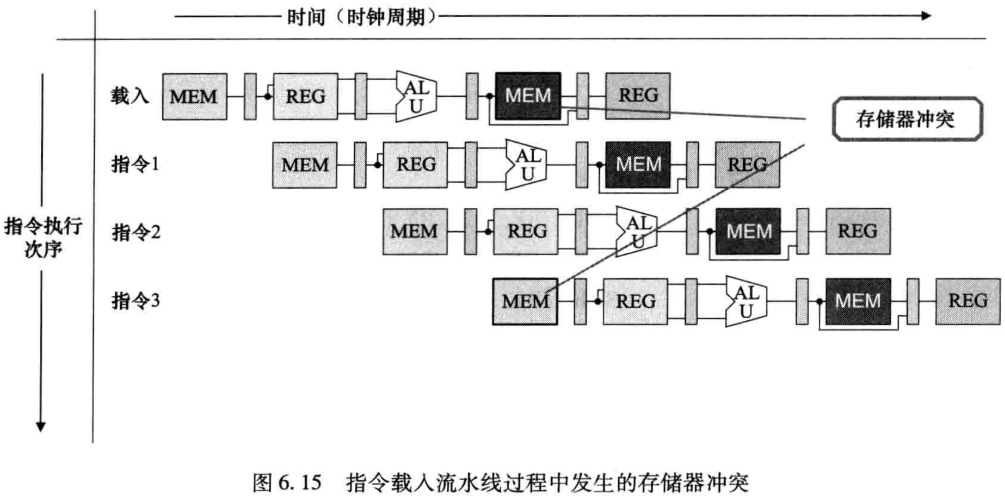

结构冒险

含义:

由于资源冲突使硬件无法支持所有可能的指令组合同时执行,即多个指令同时要求访问同一个地址,或流水线不同阶段需要使用同一模块;

如果一条指令需要的硬件部件还在为之前的指令工作,而无法为这条指令提供服务,那就导致了结构冒险。

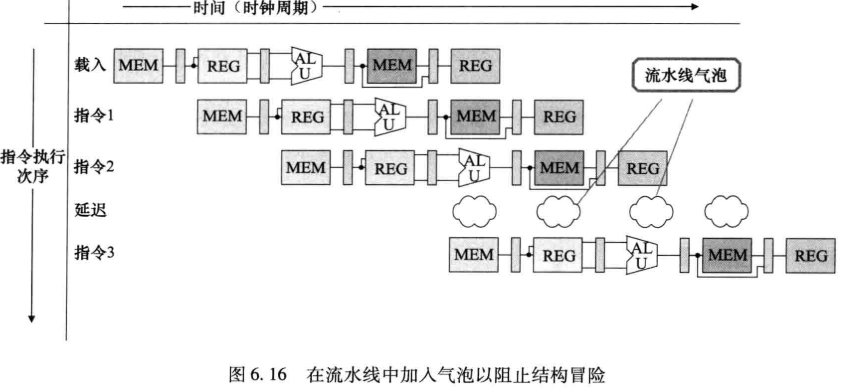

解决方法:

1、在发生冲突时将流水线停一个时钟周期,产生一个流水线气泡,在增加一个时钟延迟的情况下执行。

2、增加一个额外的MEM模块(本问题中),使不同指令使用不同的模块进行工作,但是增加了硬件资源。

数据冒险

含义:指当前指令的执行需要依赖前面指令执行的结果,后一条指令需要使用前一条指令的输出。

如果一条指令需要某数据而该数据正在被之前的指令操作,那这条指令就无法执行,就导致了数据冒险。

解决方法:

1、数据/寄存器转移

控制冒险

含义:通常发生在由于分支语句使程序计数器(PC)发生变化的情况下。

如果现在要执行哪条指令,是由之前指令的运行结果决定,而现在那条之前指令的结果还没产生,就导致了控制冒险。

其他风险

影响最大时钟频率的因素

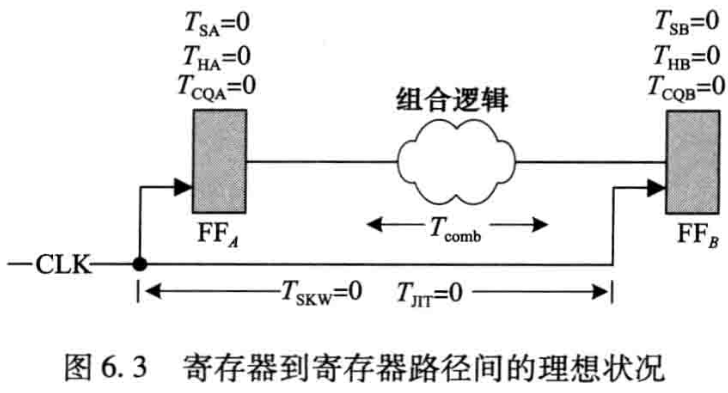

时钟频率是根据数据流入系统后在输出端出现的速率,许多因素都会影响系统的最大时钟频率。

以下图为例,当不存在时钟偏移、A输入输出响应为0,B建立时间和保存时间为0时,最大之中频率仅与中间组合逻辑延迟Tcomb有关,成反比。

Fmax = 1/Tcomb

但是实际中存在许多其他因素会影响时钟频率,如时钟偏移和抖动。

时钟偏移对流水线最大频率的影响

在实际电路中,存在线路上的传播延时,B的时钟输入现对于A会有延迟。这些传播延迟中的微小差别会发生在复杂数字产品的整个时钟网络上,最终对系统时序产生巨大影响。

当流水线相邻两个寄存器的时钟延迟TSKW大于Tcomb时,会产生负时钟偏移,先到的时钟会引起竞争条件,即数据在未成功锁存时就出发了寄存器。

时钟偏移倾向于增加电路所能承受的最大时钟频率。

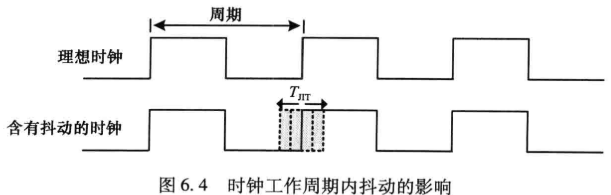

时钟抖动对流水线最大频率的影响

时钟抖动:到达电路中某一点的连续时钟边沿之间间隔的变化称为时钟抖动Tjit

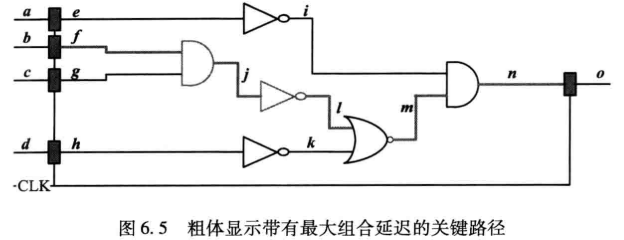

以下图中关键路径c—o的路径为例讨论时钟抖动的影响:

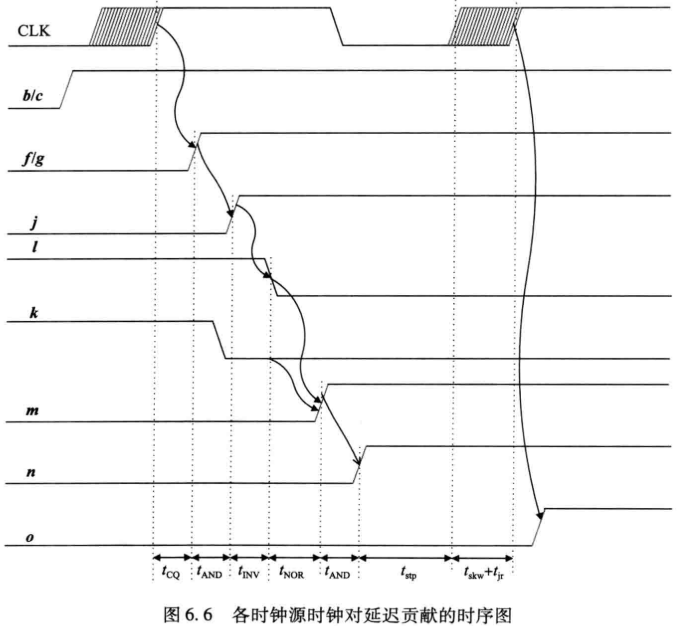

时序图如下:

因此,最大的时钟周期应该为,需要考虑最坏情况下最大的时钟抖动,导致时钟频率减小:

![]() 可以考虑在组合逻辑中增加寄存器构建流水线结构来提高最大频率。

可以考虑在组合逻辑中增加寄存器构建流水线结构来提高最大频率。

CPU五级流水

根据MIPS处理器的特点,将整体的处理过程分为取指令(IF)、指令译码(ID)、执行(EX)、存储器访问(MEM)和寄存器回写(WB)五级,对应多周期的五个处理阶段。

- 取指(Instruction Fetch):处理器从指令存储器中读取指令

- 译码(instruction Decode):处理器从寄存器文件中读取源操作数并对指令译码产生控制信号

- 执行(Excute):处理器使用ALU执行计算

- 存储器访问(Memory Access):处理器从数据存储器中读取或者写入数据

- 写回(Write Back):若是LOAD指令,将结果写回寄存器文件。

一个指令的执行需要5个时钟周期,每个时钟周期的上升沿来临时,此指令所代表的一系列数据和控制信息将转移到下一级处理。