内容:描述减少动态功耗和静态功耗的技术。

主要功耗源:

浪涌电流(启动电流):器件上电时产生的最大瞬时输入电流,与设备相关。

静态功耗(待机功耗):关断主电源或系统进入待机模式下产生的功耗,与器件的电器特性密切相关。

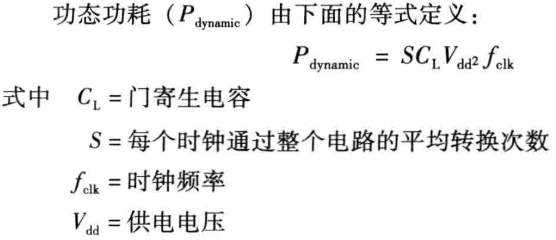

动态功耗(开关功耗):门电路输出切换时,由逻辑转换引起的功耗。

总功耗定义为静态功耗与动态功耗之和。

CAUTION:动态功耗占主要地位,在典型应用中动态功耗占总功耗的80%

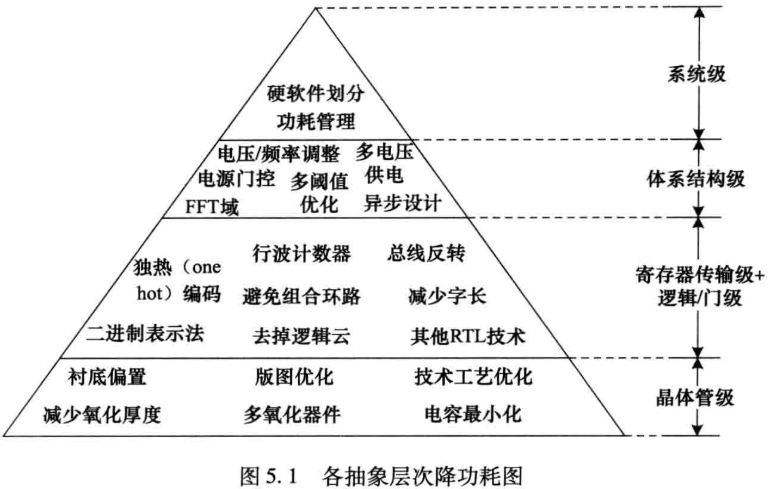

在不同设计抽象层次降低功耗的常见手段

CAUTION: 在越高的抽象层次进行低功耗设计,对功耗的降低越有效。

系统级低功耗技术

一、片上系统方法

对于纳米级芯片来说,I/O的供电电压比芯片供电电压更高,占到了50%以上。芯片之间使用I/O互连会导致大量功耗,可以使用SoC

优点:

- 降低功耗

- 减少体积

- 增加系统功能

- 提高速度

- 节省成本

二、软硬件协同设计

协同设计常规方法:

基于给定规范建立系统模型方法:

三、低功耗软件

在使用高级语言设计软件时,避免使用复杂原语;

简化算法描述方式。

基于确定硬件体系结构或处理器指令和寄存器的实现

四、选择处理器

- 采用适合需求的数据宽度的处理器;

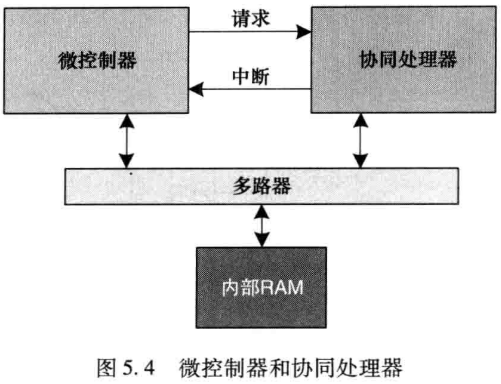

- 使用如下图的由微处理器进行控制,协处理器(最好使用特定的协处理器,以使任务在最小且能效最高的及其中完成)进行数据处理的系统体系结构;

体系结构级低功耗技术

系统使用不同的体系结构对于功耗会有显著的影响。

一、高级门控时钟

在同步数字系统中,时钟分布占整个数字开关功率中的绝大部分,可以通过门控时钟关闭绝大部分不使用的电路。

门控时钟分类:

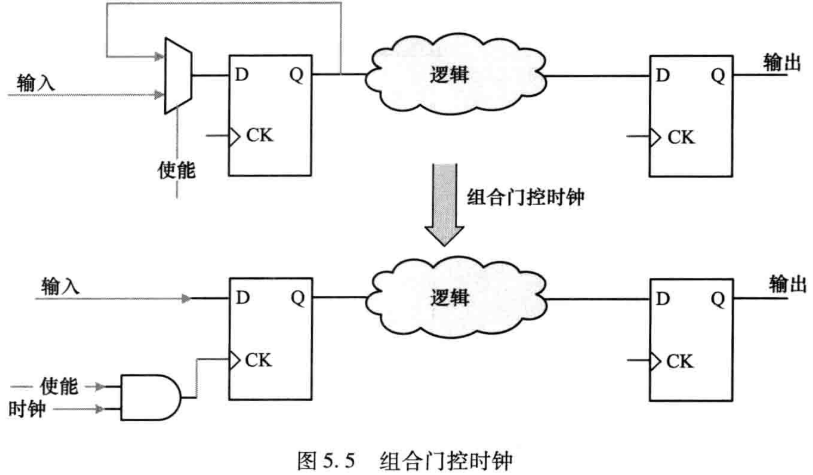

组合门控时钟(时钟与复位中不含锁存器的门控时钟电路):

在插入前后功能不改变,可以使用一致性检查工具进行验证。

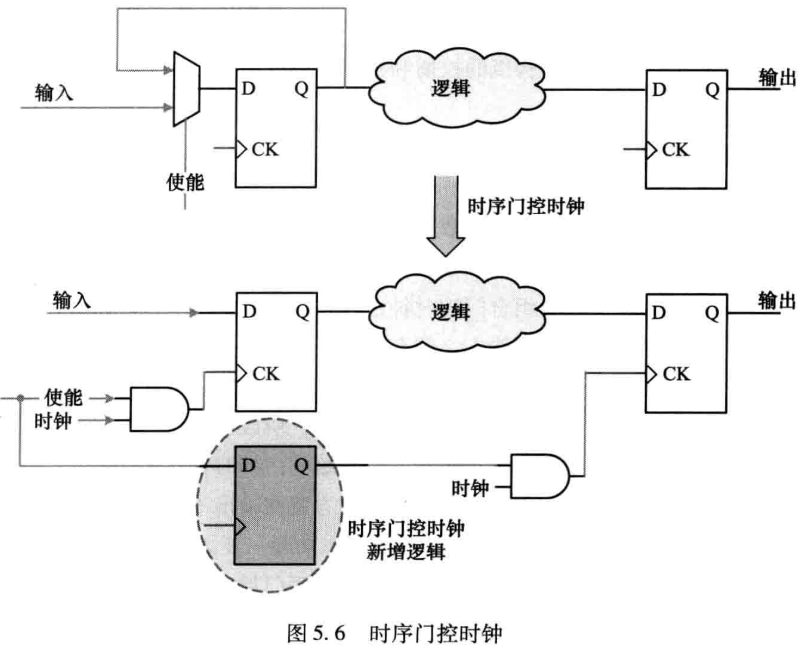

时序门控时钟

改变了设计结构,

减少了连接到带有门控时钟的寄存器块的设计部分的冗余切换

在实现时会加入额外的逻辑,所以不适用于多位宽数据的情况

问题:需要识别流水线上‘多余的’或‘不关心’ 的状态,若完成可以降低15%~25%的开关次数。??为什么

二、电压频率调节(DVFS)

动态电压频率调节(DVFS)通过在对频率不敏感的应用阶段中降低时钟速率和供电电压,在损失部分性能的情况下大幅降低功耗,时提高系统能效的流行方法。

动态电压调节依赖特殊的硬件,使用可编程的DC-DC开关电压调节器,一个可编程的时钟产生器和一个宽操作域的高性能处理器。实现在性能需求不同时是实现电压和频率的调节。

由于现在多核集成在单芯片了,对于全芯片电压/频率控制要转变为更细粒度的方式,从而增加能效。

根据运算负载动态调节处理器/系统的电压和频率,DVS能够提供峰值满足运算要求的性能,这种方式在低性能处理器上的使用体现明显。

三、基于缓存的系统体系结构

在大部分DSP应用中,可能存在频繁访问存储器数据的情况,存储器能效并不高。可以在系统存储器或RAM和处理器之间增加缓存,即预先将相关数据从主存中取到缓存中,使用小范围的缓存使计算能耗大量下降,提高能耗。

四、使用对数FFT体系结构

对于大规模运算的应用,使用对数系统(LNS)比线性系统更好,能够降低平均位元活跃度的同时用加减法代替乘除运算,效率更高。

缺点:加法器和减法器的宽度会增加,导致需要以指数级增大查找表。

五、使用异步(无全局时钟)设计

对于基于时钟体系结构的同步时钟设计,在传统设计方法中会形成大规模的时钟树结构,产生大量功耗;同时还会带来时钟偏移的问题。

使用对延时不敏感编码的信号交换接口。

六、使用电源门控

与电压门控类似,在模块不使用时暂时将其关闭。通常指在芯片上加入开关以根据应用要求选择性切断供电电流。能够将漏电减少为原来的十分之一。

分类:

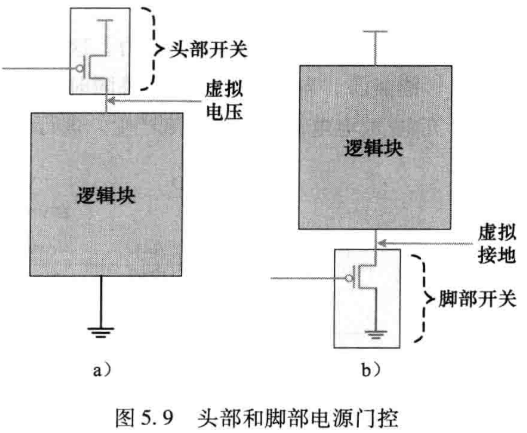

细粒度电源门控:在每个门和地之间存在一个开关晶体管,电源门控的开关的大小必须满足任何情况下对开关电流的需求,需要较大以避免压降,可以分为头部开关和脚部开关,脚部开关面积更小,类似于数集中的动态cmos。

粗粒度电源门控:电源开关晶体管作为供电网络的一部分,而非标准单元的一部分,创建了电源开关网络,各组开关晶体管能并行的对整个模块进行开关。

内容较多

七、使用多阈值电压

使用两组或多组功能相同,但是阈值电压不同的单元,会增加设计和生产的复杂性,对面积增加的副作用有限。

高阈值电压单元较慢,但漏电少;低阈值电压单元快,但漏电多。

根据设计目标的不同,可以采用不同的综合方法:

以性能为主:先使用低阈值电压库进行综合,再使用高阈值单元进行替换,是主流方法,满足时序要求的前提条件,会产生较大面积的设计。

以功耗为主:先使用高阈值电压库进行综合,找出关键路径扣使用低阈值单元进行替换。

八、多电压供电

将设计分割为多个独立的电压域,根据每个区域对时序的要求使用不同的供电电压。

(与DVS的区别:DVFS以时间为区分,在不同时间对电路整体采用不同的电压;多电压域以空间为区分,在所有时间对不同区域采用不同的电压)

九、存储器电源门控

在典型的SOC中,SRAM消耗了三分之一的功耗,对不使用的存储器矩阵进行关闭,可以减少功耗。

常用方法:

1、如果只有小部分需要常开,则可以将存储器分割,小部分处于‘开’的状态,其余部分只有在使用时才开;需要注意的是,大块RAAM划分后,读周期总数仍相同,但消耗的功耗会降低;

2、基底偏压存储器,在不使用时将存储器反向偏置,提高阈值电压,降低漏电功耗;

3、采用多种模式供电的方法,根据使用需要调节供电电压;

4、使用堆叠式存储器,降低互联电容,能并降低存储器功耗。

寄存器传输级(RTL)降低功耗

在asic设计中,RTL完成时有至少80%的功耗已经确定,RTL级代码风格对于动态和静态功耗有极大的影响,有效的方法学要求在综合前的RTL级中就将功耗相关的所有问题解决。

一、状态机编码和解码

在所有状态机编码类型中,格雷码在相邻状态转换时仅有一位发生变化,是最适合低功耗设计的;

以格雷码编码的状态机也消除了依赖于状态的组合等式中存在毛刺的风险。

对于经常使用到的状态编码为相邻的编码;

将有限状态机的转台转移图分解为两个没有状态变化的状态机,这样每个时刻仅需给一个状态机供给时钟。

二、二进制数表示法

使用有符号数的二进制表示形式比使用补码的表示形式有优势,能降低转换时变化的位数。

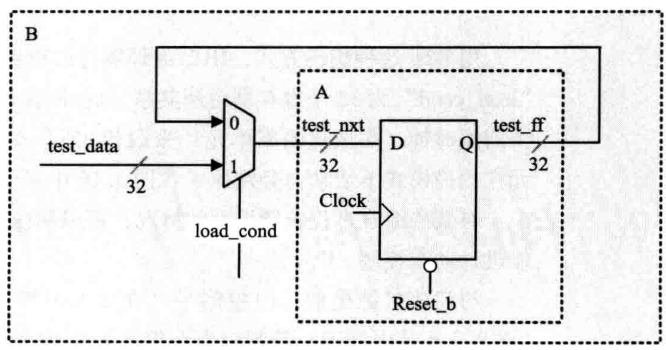

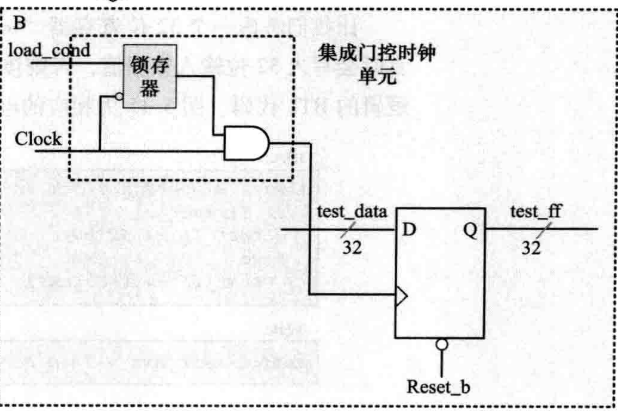

三、门控时钟基础

需要注意门控时钟的HDL写法,部分写法不会综合出门控时钟

// 不综合出门控时钟

always @(posedge clk or negedge rst)

if (!rst)

test_ff <= 32'b0;

else

test_ff <= test_nxt;

assign test_nxt = load_cond ? test_data : test_ff;

//综合出门控时钟

always @(posedge clk or negedge rst)

if(!rst)

test_ff <= 32'b0;

else if(load_cond)

test_ff <= test_data;

与门控时钟类似,门控信号和数据通路重组等应当在编写RTL时予以考虑以便达到进一步降低功耗的目的。

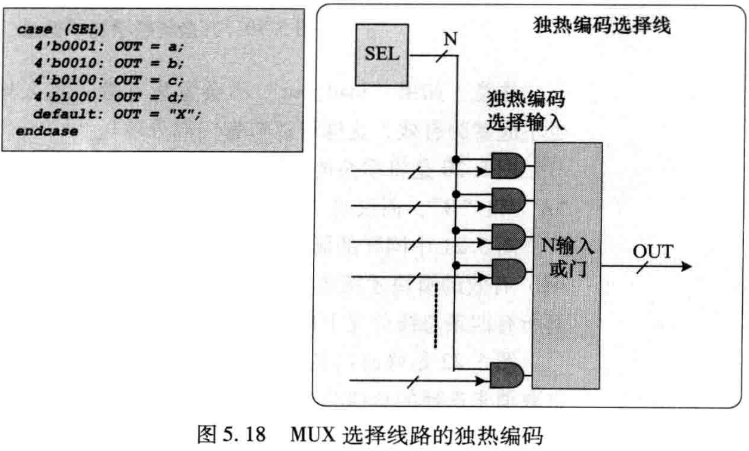

四、独热码多路器

如果MUX的每个输入都是多位总线,使用二进制选择信号会产生明显的开关过程,产生功耗。

在多路器设计中,使用one-hot编码代替二进制编码,则输出就会更快,更稳定,在初期就能将未选中的总线掩藏,降低功耗,即通过避免或掩蔽掉伪转换的发生能有效的降低功耗。

五、除去多余的转换

在没有设置默认状态的情况下,总线数据常常会发生没有意义的转换,如果转换后的数据未被真正采样,那么就是多余的,将这样的转化去掉可以显著降低功耗。

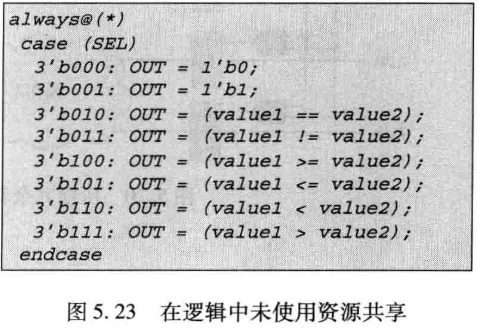

六、资源共享

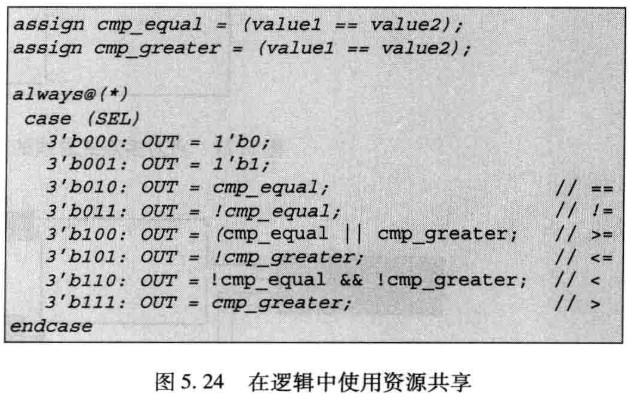

对于涉及较多算术运算的设计,如果有同样的操作在多处使用,必须避免相应的运算逻辑在多个位置重复出现。使用重复逻辑会增大面积,增加功耗。

下图分别为未使用资源功耗和使用资源共享的verilog代码,综合后使用资源共享的代码减少了比较器的数量。

七、使用行波计数器来降低功耗

能够减少电路漏电流并降低电路功耗,但是存在由于产生新的时钟域及数据之间存在一定程度偏移所导致的问题需要注意使用。

见硬件架构的艺术——时钟与复位——行波计数器

八、总线反转

当当前数据和下一数据之间的汉明距离大于N/2(N为总线宽度)时,就将下一数据反向后传输,可以减少总线上出现转换的位数量。

需要传输一个额外的控制位表示所传输的数据是否已翻转。

九、通过活跃度区分网络

通过将活跃度高的网络与活跃度低的网络区分,并将高活跃度网络置与逻辑云深处。

如图所示,若X不活跃,而Y活跃,考虑Y可能的取值,获的两个逻辑云,再使用Y作为选通信号进行选择,减少了逻辑的计算。

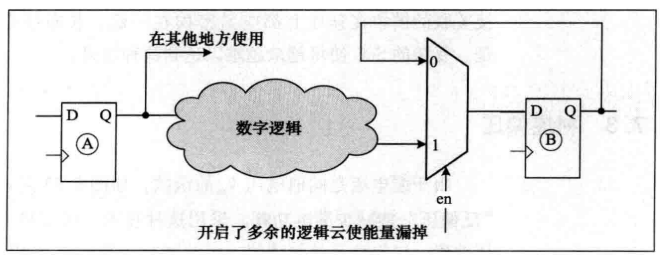

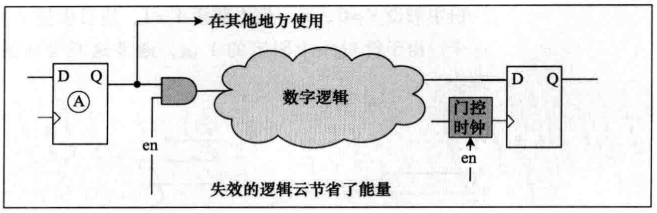

十、启用和禁用逻辑云

在逻辑云前后增加使能信号,使得A在其他地方使用,B不采样时逻辑云不进行计算,减少逻辑云功耗