内容:

主要涵盖了设计者在设计模块或者知识产权(Intellectual Preoperty)时所要用到的一些建议。

同步设计(对ASIC时序控制最安全的方法):

由单个主时钟和主置位/复位信号驱动设计中所有的时序器件。

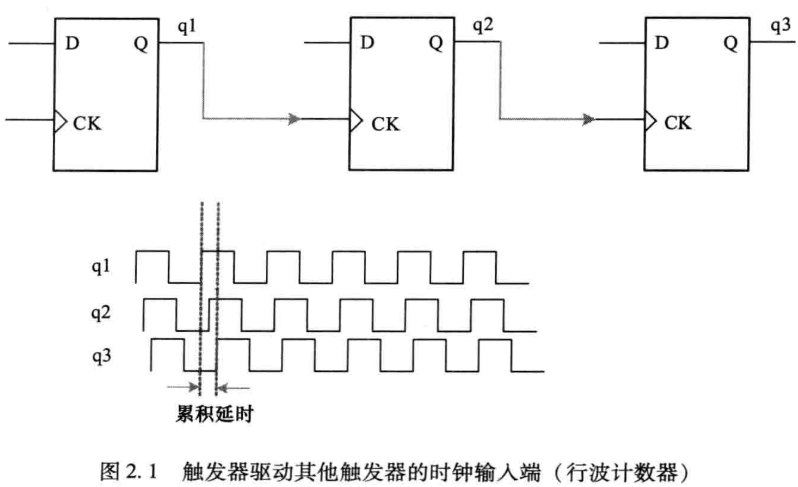

一、避免使用行波计数器

含义:即使用触发器输出作为下一级触发器的时钟输入端

缺点:

- 由于第一个触发器的输出响应导致第二个触发器的时钟输入相对于时钟信号产生偏移(延迟);

- 无法在每个时钟边沿都激活:由于延迟问题,当时钟发生跳变时,第一个触发器的输出未发生变化,从而导致第二个触发器的时钟输入变化较时钟信号晚;在每个时钟边沿都激活?可能在某几个时钟边沿激活?考虑的是第二个触发器的激活?

优点:能够减少电路的漏电流并降低电路的功耗,在低功耗设计中会取得很好的效果;

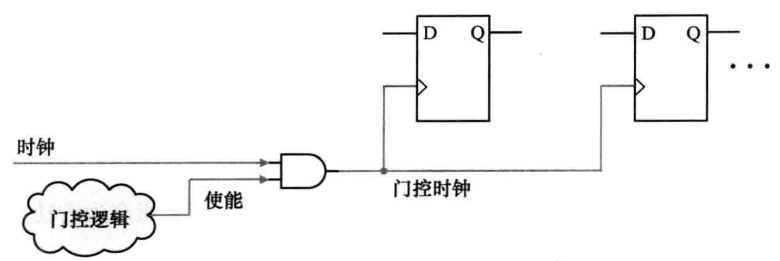

二、避免使用门控时钟

前端设计注意:含门控时钟的设计在仿真过程中可能工作正常,但是综合时会出现问题;

含义:在时钟线上使用门控单元,使用门控逻辑使能信号开关时钟;

优点:能够有效减少功耗,当时钟被门控电路关闭后,门控时钟在根部将时钟关闭,该时钟网络和其中的寄存器都会停止翻转,从而减少功耗;

同步设计中的功耗来源:

- 在每个时钟边沿变化的组合逻辑所产生的功耗(由触发器驱动这些逻辑组合);

- 由触发器产生的功耗(及时在触发器的输入和内部状态不发生变化,该功耗仍存在);

- 时钟树产生的功耗(通常占到总功耗的50%);

图2.21为同步时钟使能,通过mux可以实现纯同步方式关闭时钟域,使用该方法时钟树始终保持翻转,寄存器内部电路保持活跃,功耗高;

图2.2为门控时钟,使用门控时钟使能能在时钟树根部关闭时钟信号,时钟信号驱动的寄存器由于无时钟输入,保持原来的值,同事还能避免同步时钟设计中输入端的多路选择器,在实现大的寄存器块时节省面积。

缺点:

- 由于门控单元输入输出的延迟,会导致门控单元后的寄存器的时钟输入端信号较时钟发生偏移;

- 对毛刺敏感,并引入尖峰脉冲作用于触发器,可能导致设计失败;

- 由于门控时钟不是同步设计方案的一部分,因此会显著增加设计时间和验证的工作量;

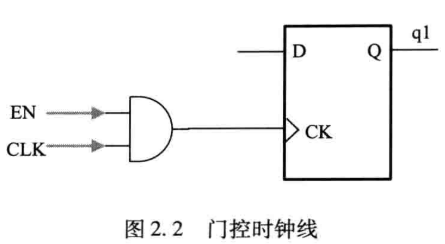

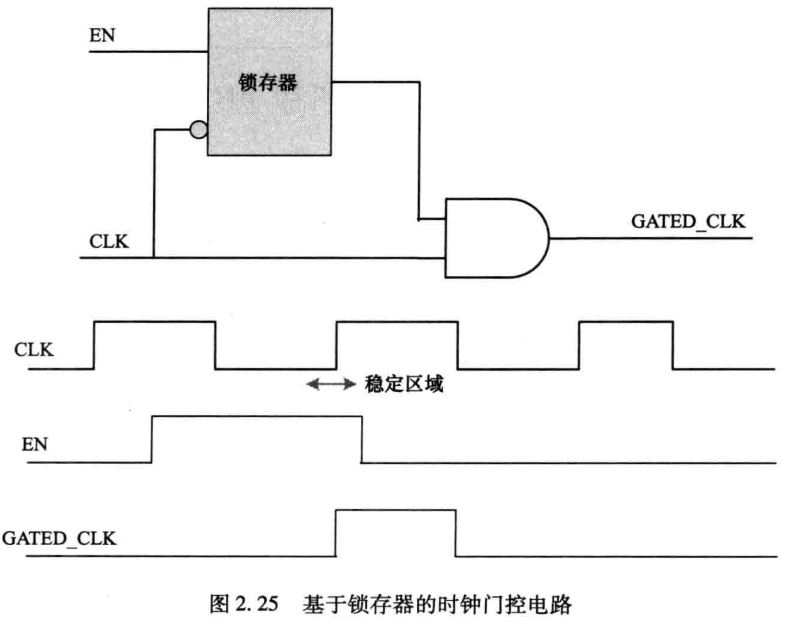

分类:不含锁存器的门控时钟和基于锁存器的门控时钟

不含锁存器的门控时钟电路:如图2.2,使用and gate 或 or gate实现

要求:使能信号从时钟活跃沿(上升沿)时钟不活跃沿(下降沿)保持常量(避免过早截断时钟脉冲或误产生多个时钟脉冲,即,门控电路输出的时钟频率增加从而导致错误)

如下图所示,由于EN在CLK活跃沿到不活跃沿发生变化,导致GATED_CLK相对于CLK提前结束高电平,等价于时钟宽度减小,频率增大,可能导致保持时间不满足,从而产生时序问题。

基于锁存器的时钟门控电路:通过锁存器来实现使能信号在时钟活跃沿到不活跃沿保持常量的要求;

下降沿为有效沿时,使用正沿触发的锁存器,并使用or gate进行控制;

使用这种电路每次仅需改变门的一个输入就能开关时钟,保证电路输出不包含任何毛刺或尖峰脉冲;

Caution:需要注意时钟占空比和产生使能信号逻辑的延迟。

重组数据路径以减少转换传播?

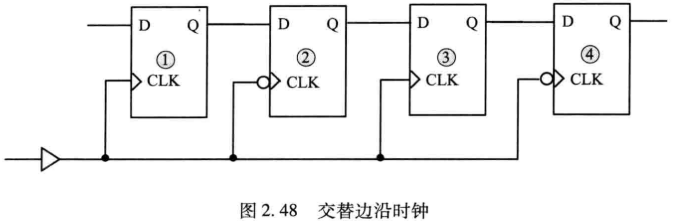

三、避免使用双边沿或混合边沿时钟

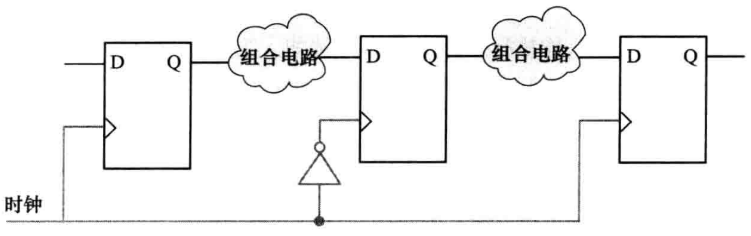

含义:使用如下图所示的相位相反的时钟信号控制两个触发器,在时钟的上升沿和下降沿都传输数据;

优点:

- 能够在给点的时钟频率下达到双倍的吞吐量;

- 与等效同步电路先比,能够降低一半功耗,同时避免了使用两倍频率的在设计中遇到的接口问题(接口在两倍频自身电气特性变差,对时钟频率和时序增加干扰愈发敏感,接口电路设计成本增加);

缺点:

- 不对称的时钟占空比会导致违背建立时间和保持时间;

- 难以确定关键路径;

- 难以使用插入扫描链的设计方法学(要求所有寄存器的有效沿一致);

Caution:尽量避免使用双沿时钟,除非对性能/速度要求很高,并无法承受使用等效同步电路在DFT和验证带来的额外开支。

四、用触发器驱动另一个触发器的异步复位端

含义:使用第一级触发器的输出作为第二级触发器的复位信号;

缺点:违反同步设计原理,还为导致第二级触发器时钟信号与复位信号产生潜在的竞争关系;

同步设计方法学

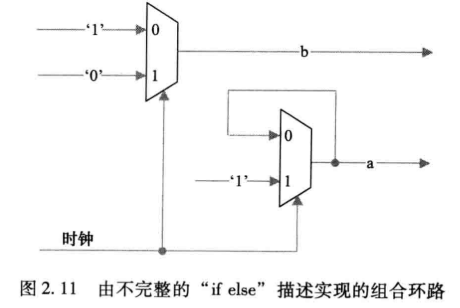

一、避免在设计中出现组合环路

含义:组合环路中的信号之间存在直接反馈回路,反馈回路中不包含寄存器,

如下图,always块之间存在直接相连,a信号通过d信号与自身直接相连;

缺点:组合环路的行为与所有逻辑的传播延迟相关,而传播延迟会根据条件的变化而发生改变,从而导致电路行为的变化;

解决方法:改变其中某个信号的生成方式,以消除信号之间的依赖性;

- 在组合环路中引入一个触发器或寄存器,打断直接通路;

- 在寄存器的输出端通过组合逻辑直接控制同一个寄存器的异步输入端;

Caution:组合环路不可综合

二、避免数字设计中的延迟链

延迟链:使用多个带有单扇入和单扇出的连续节点产生延迟(通常使用多个反相器链增加延迟),通常出现在异步设计中,有时用于解决其他组合逻辑导致的竞争条件。

问题:会增加设计对操作环境的敏感性,降低设计的可靠度,增加将设计移植到不同器件结构上的难度。

方法:在设计中使用同步技术取代异步技术。

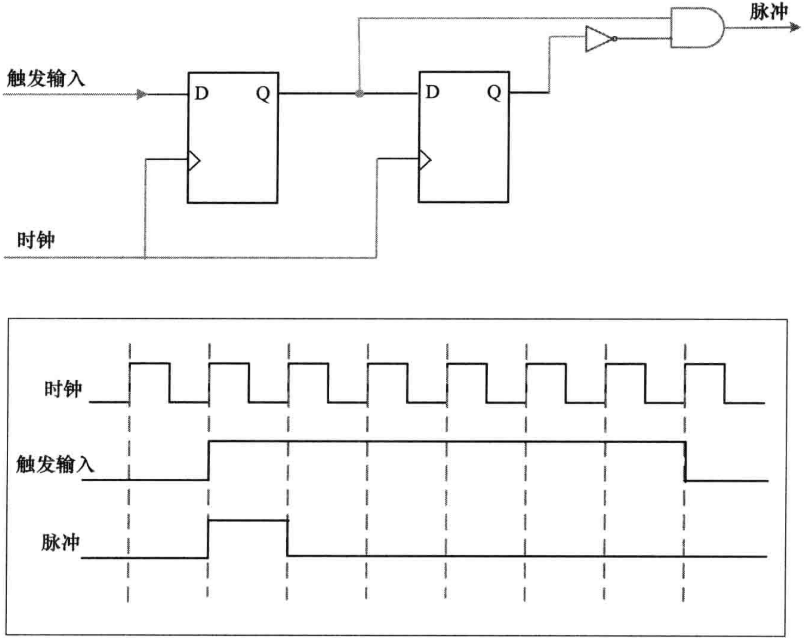

三、避免使用异步脉冲产生器

脉冲类型:单个脉冲(脉冲产生器) & 一系列脉冲(多振子):

- 一个触发信号接到两输入门的and gate 或 or gate的输入端,其中一个输入端信号取反或加入延迟链从而使门电路输出脉冲,脉冲的宽度取决于两个输入的相对延迟;

- 寄存器输出通过延迟链后驱动自身的异步复位端(本质是经过一个确定延迟后对自身异步复位);

Caution:上述方法为纯异步,尽可能避免;

问题:

- 脉冲宽度难以确定,实际宽度只有在布局布线之后,确定布线和传播延时后才能确定;

- 同时,脉冲宽度可能会随工艺的变化而产生变化;

- 难以使用静态时序分析来验证脉冲宽度;

解决方法:

使用如下图的同步脉冲产生器,产生的脉冲宽度与时钟周期宽度相同,宽度可预测,可以使用时序分析进行验证,独立于具体工艺易于移植。

四、避免使用锁存器

缺点:

- 锁存器时序模糊,工具无法确定在时钟前沿还是后沿将数据传输至输出端,这种只有设计者知道的信息导致设计难以移植或代码复用;

- 静态时序分析器通常会作出与锁存器透明有关的错误假设,或发现通过数据输入端口的伪路径,或将真正的关键路径丢失;

- 锁存器常常使电路不可测;

- 锁存器为连通状态,即在数据输入输出之间存在直接通路,输入端的毛刺能传递到输出端;

解决方法:在数字设计中,锁存器用来在新值到来之前保持原值,应用使用触发器代替;

应用场景:使用锁存器挪用周期或借用时间可以满足关键路径的要求;

Caution:部分FPGA架构不支持锁存器,当综合包含锁存器的设计时,综合工具会创建组合反馈桐庐来取代锁存器,但是组合反馈通路会违背建立时间和保持时间的要求,并且难以发现

五、避免使用双沿时钟

时钟方案

一、内部产生的时钟

问题:

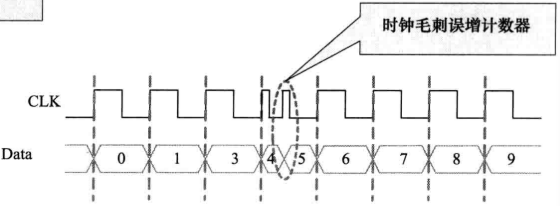

- 内部时钟产生器产生的毛刺或尖峰脉冲可能会违背建立时间与保持时间;

- 即使没有违背时序要求也可能会导致寄存器输出意料之外的值从而导致功能出现问题;

- 如图2.17,产生内部时钟的组合逻辑会增加时钟线上的延迟,如果时钟偏移大于数据延迟就会违背寄存器的时序要求,出现功能错误;

解决方法:

问题1:在时钟产生器后增加一个寄存器,以消除时钟产生逻辑中的毛刺;

问题3:将产生的时钟放到SoC中高扇出且低偏移的时钟树上,有助于减少信号整体的时钟偏移;

二、分频时钟

Caution:

- 在对主时钟进行分频时,应该始终使用同步计数器或状态机;

- 设计中应由寄存器直接产生分频时钟信号,永远不要对计数器或状态机进行解码后产生时钟信号,常常导致毛刺或尖峰脉冲;

三、行波计数器

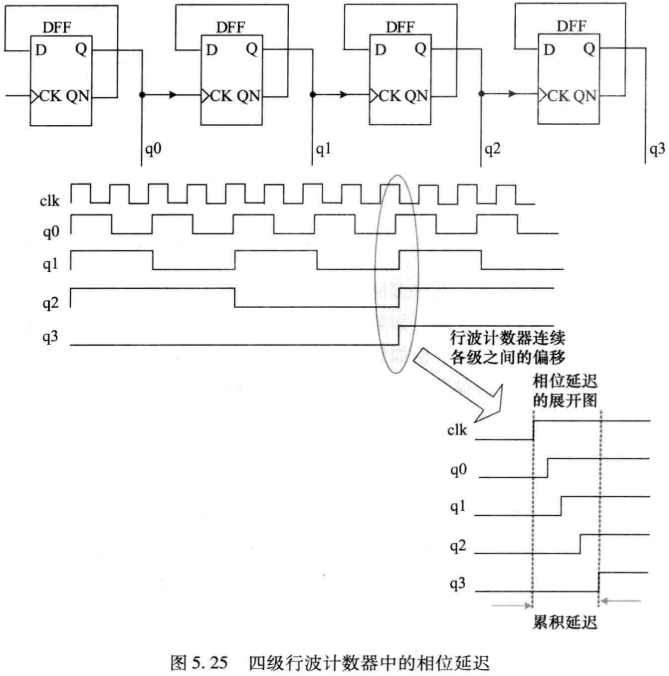

由计数器分频或状态机输出产生的时钟又叫“行波时钟(ripple clock)”,行波计数器常被用于幂为2的分频。当前一级时序逻辑的数据输出被用作下一级时序逻辑的时钟输入,这个时钟就是“行波时钟”。

下图所示,行波计数器每一级都进行二分频操作,但是由于存在寄存器的传播延时,在较高有效位(q3)相对于较低有效位(q0)发生变化更晚。

在时钟行进过程中,计数器可能由于毛刺产生不正确的值,在最高有效位变化时,会产生最坏的影响。?低有效位输入错误值,但是由于高有效位发生变化晚,导致低有效位的值传递至高有效位?

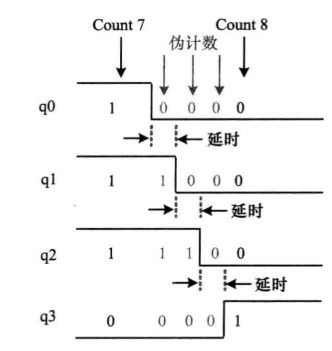

如下图所示,计数器从0111变到1000时会经历‘0111→0110→0100→0000→1000’几个阶段,中间的值是因为高有效位变化慢与低有效位所产生的伪计数。

如果将其驱动LED不会产生影响,但是如果用于驱动多路选择器,存储器中的索引指针,怎会导致错误输出,无法接受。

优点:与其他同步技术方式相比,行波计数器使用门数更少;

缺点:计数器在各阶段创建行波时钟,产生新的时钟域,这种级联会对STA和综合工具带来麻烦,会增加验证的工作量;还会为扫描链的插入增加难度。

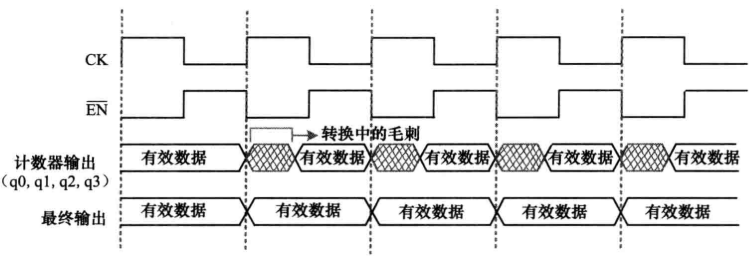

使用如下图方式能使行波计数器可靠性更高,可用性更强。

接收电路通过使能信号获获取行波计数器读数,在行波计数器输出稳定后接受,

行波计数器能减少电路都电流并降低电路功耗,但是在使用时要小心,会对可测性和缺陷覆盖率产生问题。

四、多路时钟

含义:使同一个逻辑功能具有不同时钟;

使用条件:

- 在初始化配置后,时钟多路操作就是可接受的;

- 在测试时,设计会绕过功能时钟多路逻辑而选择普通的时钟;

- 在时钟切换时,寄存器始终处于复位状态;

- 在时钟切换时产生的短暂错误没有负面影响;

复位信号设计策略

复位:是为了时SoC进入一个能进行稳定操作的确定状态,可以避免在上电后进入随机状态而死机;

选择策略:

- 使用同步复位还是异步复位;

- 是否每个触发器都要接收到复位信号;

是否使用复位:是否需要对SoC使用复位由系统、SoC应用环境以及SoC自身的设计方式决定;

Caution:好的设计指南会在系统没有明确要求的情况下为每个触发器都提供复位信号。

一、同步复位

含义:只有在时钟的有效沿到来时才能影响或者复位触发器的状态。

//同步复位信号

module load_syn_ff (

input clk, in, load, rst_n,

output out);

always @(posedge clk)

if(!rst_n)

out <= 1'b0;

else if(load)

out <= in;

endmodule

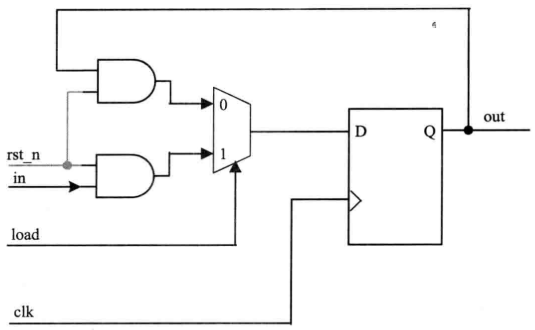

问题:综合工具无法区分复位信号与其他数据信号,产生如下电路图;

解决方法:综合工具允许指定信号为复位信号,从而使复位信号尽可能接近触发器,可以在开始时将这些指令加入RTL代码以避免重新综合。

优点:

- 同步信号一般能确保电路是完全同步的;

- 同步复位会综合为更小的触发器,尤其是复位信号被触发器的输入逻辑门控时;

- 同步复位确保复位智慧发生在有效时钟沿,可以过滤掉复位毛刺;

- 在部分设计中,复位必须由一组内部条件产生,在这样的设计中使用同步复位信号,可以将时钟之间的复位毛刺过滤掉?

缺点:

- 综合工具容易将复位逻辑综合到触发器自身之外(如上图);

- 为确保复位信号出现在时钟有效沿附近,同步复位需要一个脉冲展宽器(这在多时钟设计时必须考虑,可以使用小计数器指定复位脉冲的宽度);

- 由组合逻辑产生或者经多级组合逻辑的复位信号,可能不容易被外部引脚控制,复位信号可能标记为X;

- 使用门控时钟时,在时钟关闭阶段同步复位可能无效;

Caution:由于复位树的高扇出,复位信号相对于时钟信号晚,需要尽可能减少其到达本地逻辑前穿过的逻辑数量。

二、异步复位

含义:触发器在设计时加入复位引脚,通常为低电平有效,使触发器进入复位状态。

//异步复位

module load_asyn_ff(

input clk, in, load, rst_n,

output out);

always @(posedge clk or negedge rst_n)

if(!rst_n)

out <= 1'b0;

else if(load)

out <= in;

endmodule

优点:

- 能够避免同步复位带来的时序紧张问题,避免复位信号加载到数据路径中;

- 复位信号与时钟信号无关,无论有没有时钟信号都可进行复位;

缺点:

- 在DFT时,如果异步复位信号不能直接被I/O引脚驱动,就必须将异步复位路线与复位驱动器 断开以保证DFT扫描和测试的正确;

- 如果一部复位在触发器时钟有效沿附近释放,触发器的输出就会进入亚稳态,SoC的复位状态会丢失;(与时钟信号的竞争?)

- 异步复位信号中的毛刺可能会对电路功能产生影响,需要设计毛刺过滤器消除复位电路上的毛刺的影响;

- 对于同步和异步复位,都要确保复位树时间可控,复位能在一个时钟周期内释放,需要分析复位树的时序以确保满足时序要求;(可以使用分布式复位同步触发器?)

三、带异步复位和异步置位的触发器

仅在有特殊要求下才会设计这类触发器

下述代码:在①阶段复位信号有效,进入always块,信号复位;在②阶段置位信号有效,由于复位信号优先级高,信号仍保持复位;在③至④阶段如果没有时钟信号将不触发always块,则信号在④后不进入置位。

//asynchronous set and asynchronous reset

module dff_set_reset(

input clk, in, rst_n, set_n,

output out);

always @(posedge clk or negedge rst_n or negedge set_n)

if(!rst_n)

out <=1'b0;

else if(!set_n)

out <= 1'b1;

else

out <= in;

endmodule

???

Caution:仅有很少的设计中才允许复位与置位同时发出,然后复位信号先撤销;要尽可能避免使用同时带有异步置位和异步复位的触发器。

解决方法:将自校验码附着在正确的编译器指令中对触发器建模,并在这种情况发生时间刚出发起输出强制为正确的值

// Add Compiler specific directive to

// ignore the following block during synthesis

always @(rst_n or set_n)

if(rst_n && !set_n)

force q = 1;

else

release q;

//End the compiler directive here

endmodule

四、移除异步复位的问题

问题:移除异步复位(将复位信号从有效电平转换到无效电平)会使芯片进入不稳定的未知状态,在释放复位时需要特别注意;

同步复位:复位信号的前沿和尾沿必须远离时钟的有效边沿;

异步复位:

问题:

- 违背复位恢复时间,复位恢复时间指复位撤销后和时钟再一次置高之间的时间,会使寄存器数据输出端出现数据完整性或亚稳态问题;

- 复位移除会在不同时序元件的不同时钟周期内发生,复位移除与时钟上升沿异步时,在复位信号和/或时钟信号上不同的传播延迟会导致某些寄存器或触发器提前退出复位状态(有什么影响?);

解决方法:使用复位同步器。

复位同步器:

作用:是确保正确移除复位最常使用的方法,如果没有复位同步器,即使在仿真时复位能正常工作,但最终系统中的异步复位信号任是无效的;

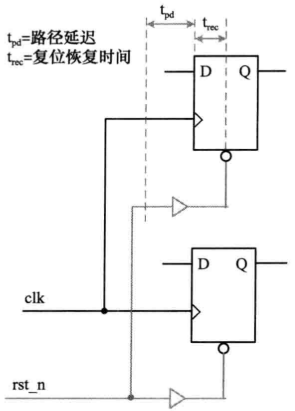

工作原理:用外部异步复位信号来复位一对触发器,这对触发器异步地依次驱动主复位信号通过复位缓冲树,再到达设计中的其他触发器,最后对整个设计异步复位;

第二个触发器能避免亚稳态的产生?

五、过滤复位毛刺

控制时钟偏移

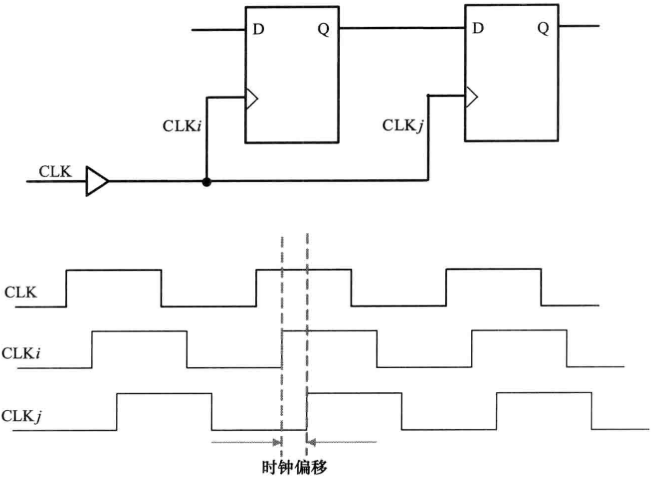

定义:整个芯片中时钟信号到达时间的差异称为时钟偏移。

如果下一级的建立时间小于始终偏移,那么次一级的输出可能会是前一级当前的输入?

短路径问题:

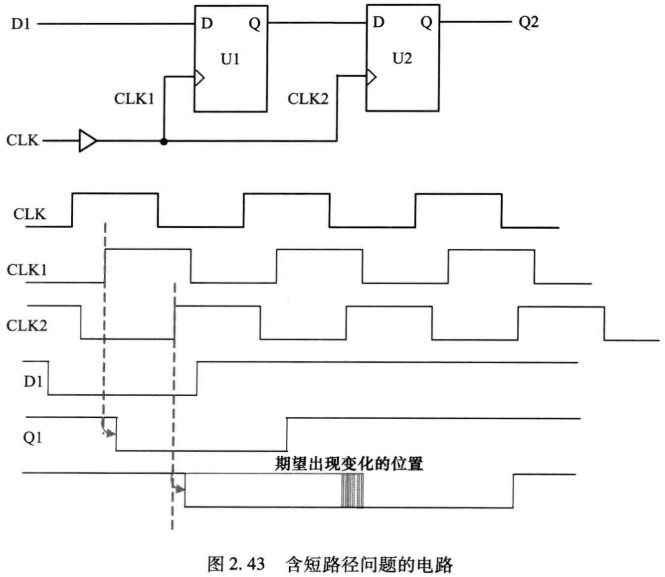

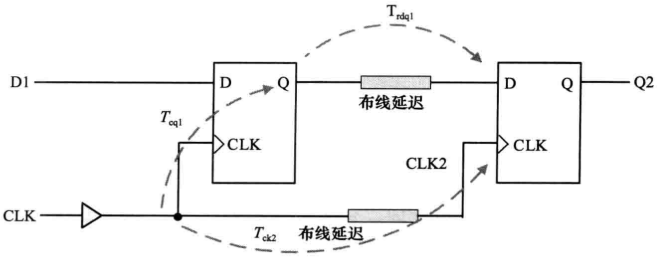

定义:相邻触发器之间的数据传播延迟比时钟偏移还短。

问题:由于第一个时钟沿到达第二个触发器比新数据要慢,因此第二个触发器在与第一个触发器相同的边沿处,切换为第一个触发器相同的值。使得两个触发器在同一个边沿处移位同样的数据,最终导致功能错误。

解决方法:将时钟偏移最小化

时钟偏移最小化

一、在数据路径上加延迟

含义:在数据路径上增加延迟,使数据路径的延迟大于时钟偏移。

要求:在数据路径中插入的延迟必须足够大以保证数据路径延迟一定能大于始终偏移。

二、时钟反转

含义:将时钟相对于数据反转使用,即让第二级寄存机较第一级先接收到时钟信号;

缺点:

- 牺牲了第一级的建立时间来提高保持时间;

- 由于难以明确定义第一级触发器,对于约翰逊计数器和线性反馈以为寄存器(LFSR)这样的环路结构并不是很有效;

三、使用交替相位时钟

交替使用时钟沿:顺序上相邻的触发器使用相反的时钟沿触发;

交替使用时钟相位:顺序上相邻的触发器分别由同一时钟的不同相位驱动,相位差需要与针对时序进行选择;

使用行波时钟结构:下一级触发器由上一级触发器的输出作为时钟信号,使得触发器不在同一时钟翻转,消除了时钟偏移;

平衡线路长度:保持所有时钟线长度相等,也保持各终端负载相同,从而保证线路长度适当平衡,实现低的时钟驱动器偏移;

Caution:

- 紧密关注驱动器上的输入-输出延迟规范;

- 在时钟各级层次上使用同样的驱动器;

- 平衡各级标称的线路延迟;

- 在各条线路上使用同样的终端策略;

- 平衡各条线路的负载,这可能意味着需要再一条支路上添加多余电容以与其他分支平衡;