转自https://www.cnblogs.com/kingstacker/p/7520199.html

前言

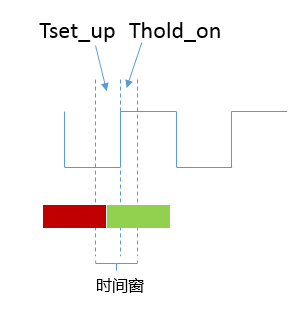

触发器输入端口的数据在时间窗口内发生变化,会导致时序违例。触发器的输出在一段时间内徘徊在一个中间电平,既不是0也不是1。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

触发器由于物理工艺原因,数据并不是理想化的只要触发沿时刻不变即可。触发器有固定的建立时间,保持时间。

建立时间:在时钟有效沿到来前数据需要稳定的时间。

保持时间:在时钟有效沿之后数据还需要保持不变的时间。

后果:会给设计带来致命的功能故障。

一般来说,信号是在异步信号,跨时钟域,复位电路中产生亚稳态。

解决方式:

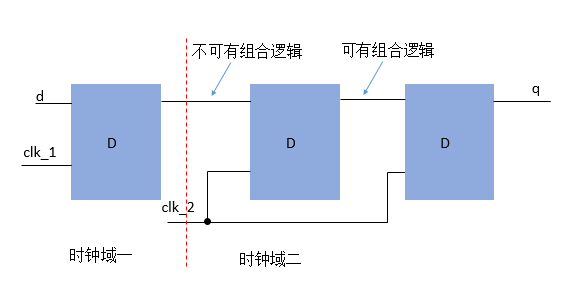

1.单比特信号:

①采用同步器同步,低速设计打两拍,高速设计可能需要打三拍。

低速到高速时钟域,低速信号一般能被高速时钟域采到甚至多次。但高速时钟域到低速时钟域就不太好办了:

②闭环解决方案:采用握手反馈信号,这会导致延时开销大。

③开环解决方案:把信号展宽,至少为采样T的1.5倍。这样至少能采到一次。

2.多比特信号:

传递多比特信号,普通同步器就没啥卵用了,因为多比特信号偶发数据变化歪斜,导致采到的不一定是正确数据。

①多比特信号融合:把多比特信号转换为单比特信号(GrayCode),再用同步器同步。

②多周期路径规划:数据不需要同步,至需要同时传递一个同步的使能信号到接收时钟域即可,使能信号没被同步到接收时钟域并被识别之前数据不被采集。即在信号某个沿产生同步脉冲指示信号。

③异步fifo。

以上。