在项目后仿的过程中,由于后端提供的网表并非完整的网表,而是分模块提供的独立网表。所以后仿是在仿真环境中既有rtl代码,又有网表。这种情况下rtl 模块与网表模块之间的接口存在信号的hold time无法满足的情况。所以需要将rtl给到网表的输入信号做一个delay再输入到网表中。在这个过程中研究了一下verilog中的延时问题。

no bb,show me your code.

module test(input in, output a,output b,output c,output d,output e,output f,output g); reg a; reg b; reg c; reg d; always@(*) begin #5 a=in; end always@(*) begin b= #5 in; end always@(*) begin #5 c<=in; end always@(*) begin d <=#5 in; end assign #5 e=in; assign f=in; assign #1 g=in; endmodule

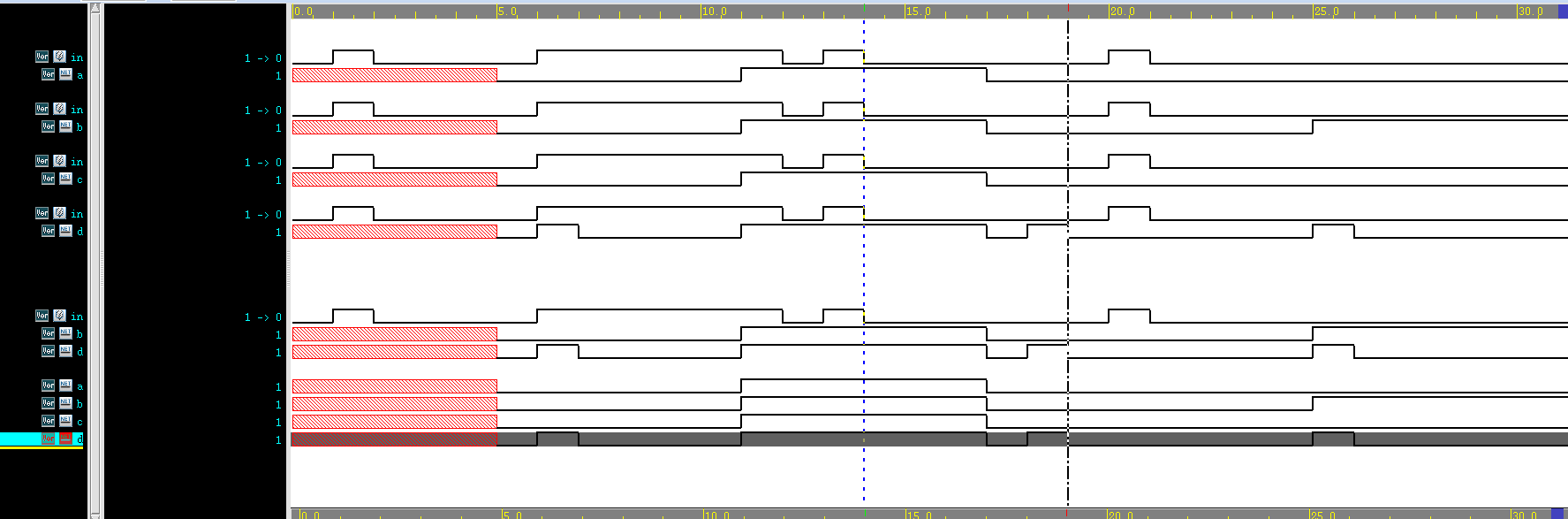

下面是以上代码再vcs下的仿真波形:

首先看信号a,c

信号a,c都是再always块被赋值,敏感条件是*,也就是只要输入信号in变化就会触发对应always块的执行,该always块内部先是执行#5,等待5个时间单位,然后把in的当前值(5ns时刻的值)赋给a,c。也就是在0时刻该always块触发以后等待5ns,将5ns时刻的in值0赋值给a,c.在always内部的#5等待5ns的这个时间段以内,输入信号in的任何变化都不会被响应。下次触发always的条件就是5ns后in的再次跳变。

再来看信号b,d

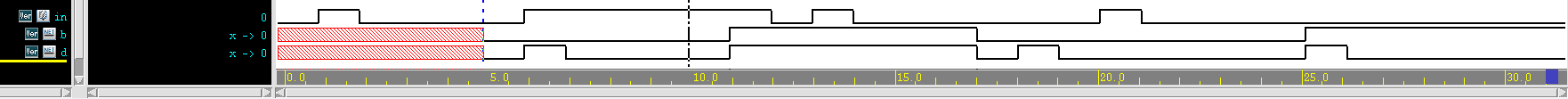

#5放在赋值符号之后,不同在于b采用的阻塞赋值,d采用的非阻塞赋值。两者都是将5ns之前的in值赋给b,d。但是阻塞赋值的情况信号b会忽略等待5ns这段时间的输入信号的变化。换个说法就是in信号的跳变触发always块,记录当前in值,然后等待#5,同时在等待的过程中忽略in的变化,等#5时间一到将之前记录的in值赋给b;信号d则不同,in信号的跳变触发always块,记录当前in值,然后等待#5,但是在等待#5的过程中也会记录in的变化。这种情况相当于信号d是将in整体后移了5ns。

遗留问题

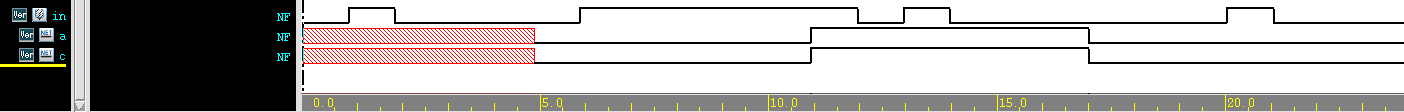

assign #5 e=in;